(54) УСТРОЙСТВО ДЛЯ ЛИНЕАРИЗАЦИИ ХАРАКТЕРИСТИК ЧАСТОТНЫХ ДАТЧИКОВ

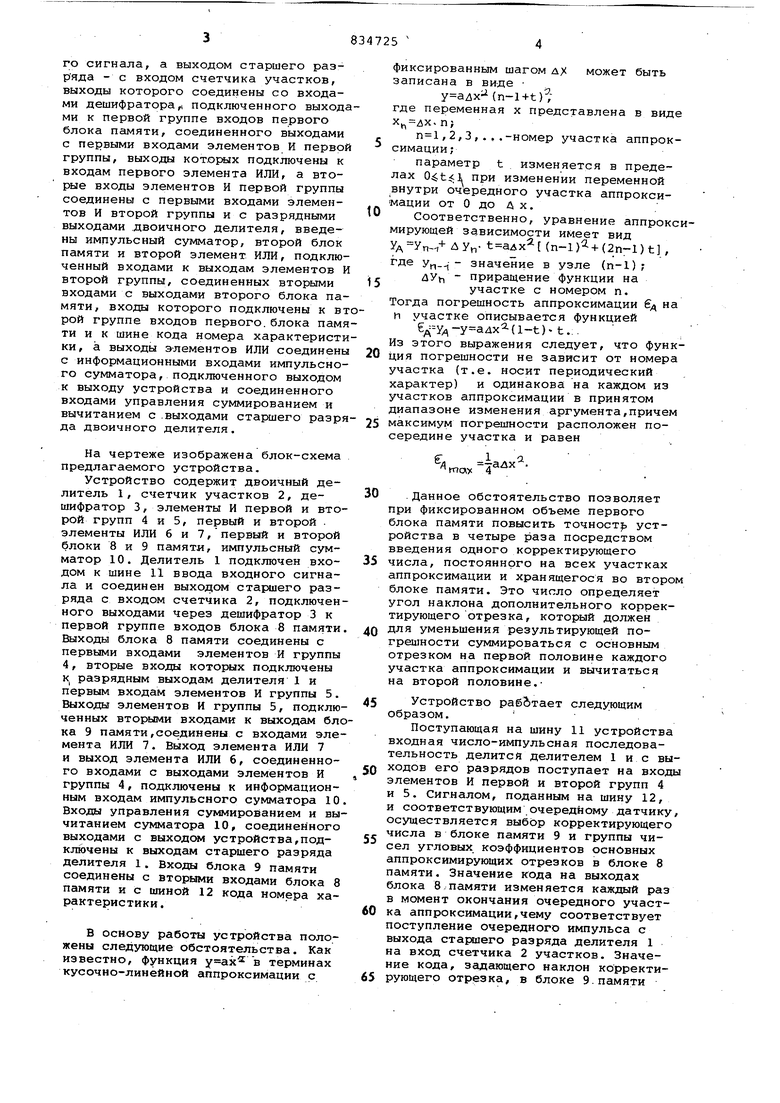

го сигнала, а выходом старшего разряда - с входом счетчика участков, выходы которого соединены со входами дешифратора, подключенного выходами к первой группе входов первого блока памяти, соединенного выходами с первыми входами элементов И первой группы, выходы которых подключены к входам первого элемента ИЛИ, а вторые входы элементов И первой группы соединены с первыми входами элементов И второй группы и с разрядными выходами .двоичного делителя, введены импульсный сумматор, второй блок памяти и второй элемент ИЛИ, подключенный входами к выходам элементов И второй группы, соединенных вторыми входами с выходами второго блока памяти, входы которого подключены к второй группе входов первого.блока памяти и к шине кода номера характеристики , а выходы элементов ИЛИ соединены с информационными входами импульсного сумматора, подключенного выходом к выходу устройства и соединенного входами управления суммированием и вычитанием с .выходами старшего разряда двоичного делителя. На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит двоичный делитель 1, счетчик участков 2, дешифратор 3, элементы И первой и второй групп 4 и 5, первый и второй . элементы ИЛИ 6 и 7, первый и второй блоки 8 и 9 памяти, импульсный сумматор 10. Делитель 1 подключен входом к шине 11 ввода входного сигнала и соединен выходом старшего разряда с входом счетчика 2, подключен ного выходами через дешифратор 3 к первой группе входов блока 8 памяти Выходы блока 8 памяти соединены с первыми входами элементов И группы 4, вторые входы которых подключены к разрядным выходам делителя 1 и первым входам элементов И группы 5. Выходы элементов И группы 5, подклю ченных вторыми входами к выходам бло ка 9 памяти,соединены с входами эле мента ИЛИ 7. Выход элемента ИЛИ 7 и выход элемента ИЛИ 6, соединенного входами с выходами элементов И группы 4, подключены к информационным входам импульсного сумматора 10 Входы управления суммированием и вы читанием сумматора 10, соединенного выходами с выходом устройства,подключены к выходам старшего разряда делителя 1. Входы блока 9 памяти соединены с вторыми входами блока 8 памяти и с шиной 12 кода номера характеристики. В основу работы устройства положены следующие обстоятельства. Как известно, функция в терминах кусочно-линейной аппроксимации с

фиксированным шагом дх может быть записана в виде

(n-1+t)где переменная х представлена в виде .п;

,2,3,...-номер участка аппроксимации;

параметр t изменяется в пределах при изменении переменной внутри очередного участка аппроксимации от О до д X,

Соответственно, уравнение аппроксимирующей зависимости имеет вид ,+ ДУп- (n-l) + {2n-l)t , где значение в узле (п-1) ;

с ЛУ приращение функции на

участке с номером п.

Тогда погрешность аппроксимации €д на h участке описывается функцией

(l-t) t.:. Из этого выражения следует, что функция погрешности не зависит от номера участка (т.е. носит периодический характер) и одинакова на каждом из участков аппроксимации в принятом диапазоне изменения аргумента,причем

5 максимум погрешности расположен посередине участка и равен А 4адх. 4 .Данное обстоятельство позволяет при фиксированном объеме первого блока памяти повысить точност устройства в четыре раза посредством введения одного корректирующего числа, постоянного на всех участках аппроксимации и хранящегося во втором блоке памяти. Это число определяет угол наклона дополнительного корректирующего отрезка, который должен для уменьшения результирующей погрешности суммироваться с основным отрезком на первой половине каждого участка аппроксимации и вычитаться на второй половине.Устройство работает следующим образом. Поступающая на шину 11 устройства входная число-импульсная последовательность делите делителем 1 и с выходов его разрядов поступает на входы элементов И первой и второй групп 4 и 5. Сигналом, поданным на шину 12, и соответствующим очередному датчику, осуществляется выбор корректирующего числа в блоке памяти 9 и группы чисел угловых, коэффициентов основных аппроксимирующих отрезков в блоке 8 памяти. Значение кода на выходах блока В.памяти изменяется каждый раз в момент окончания очередного участка аппроксимации,чему соответствует поступление очередного импульса с выхода старнего разряда делителя 1 на вход счетчика 2 участков. Значение кода, задающего наклон корректирующего отрезка, в блоке 9.памяти

не изменяется в течение всего времени линеаризации характеристики датчика.

Как следует из принципа рассмотренного метода линеаризации, числоимпульсная последовательность, поступающая с выхода элемента ИЛИ 7, в течение времени отработки первой пол вины каждого участка аппроксимации должна вычитаться из число-импульсной последовательности, поступающей ,с выхода элемента ИЛИ 6, а в течение времени отработки второй половины участков - суммироваться. Такой режим работы сумматора 10 осуществляется путем подключения входов управления сложением- и вычитанием сумматора к выходам старшего разряда делителя 1 (прямому и инверсному выходу триггера старшего,разряда), сигналы на входах которого изменяются в указанные моменты времени. Суммарная импульсная последовательность, определяемая наклоном очередного линейного отрезка нг очередном участке аппроксимации и знаком и наклоном корректирующего отрезка, с выхода , сумматора 10 поступает, на выход устройства. В момент окончания входной число-импульсной последовательности на выход устройства поступает суммарное число импульсов,линейно связанное с изменяемым параметром.

Таким образом, предлагаемое устройство по сравнению с известным позволяет при заданной точности линеаризации упростить конструкцию устройства за счет уменьшения объема блока памяти, причем выигрыш в числе ячеек памяти особенно существенный при линеаризации характеристик не одного, а нескольких датчиков. Формула изобретения

Устррйство для линеаризации характеристик частотных датчиков,содержащее двоичный делитель, соединенный входом с шиной ввода входного сигнала, а выходом старшего раэрядас входом счетчика участков, выходы которого соединены со входами дешифратора , подключенного выходами к первой группе входов первого блока памяти, соединенного выходами с первыми входами элементов И первой группы, выходы которых подключены к входам первого элемента ИЛИ, а

0 входы элементов И первой группы соединены с первыми входами элементов И второй группы и с разрядными выходами двоичного делителя, отличающееся тем, что, с целью

5 упрощения устройства при линеаризации датчиков с квадратичной характеристикой , в устройство введены импульсный сумматор, второй блок памяти и второй элемент ИЛИ, подключенный входами к выходам элементов И

0 второй группы, соединенных вторыми входами с выходами второго блока памяти, входы которого подключены к второй группе входов первого блока памяти и к шине кода номера характе5ристики, а выходы элементов ИЛИ соединены с информационными входами импульсного сумматора, подключенного выходом к выходу устройства и соединенного входами управления суммиро0:ванием и вычитанием с выходами старшего разряда двоичного делителя.

Источники информации, принятые во внимание при экспертизе

5

1.Новопашенньтй Г.Н. Информационно-измерительные системы. М., Высшая школа , 1977, с.89.

2.Авторское свидетельство СССР

0 552623, кл. G 06 G 7/26, 1975 (прототип).

11

0-

Г

1

IT J

И

}

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции характеристик датчиков | 1978 |

|

SU781850A1 |

| Устройство для воспроизведенияКВАдРАТичНыХ фуНКций | 1978 |

|

SU842802A1 |

| Устройство для воспроизведенияфуНКций | 1979 |

|

SU809200A1 |

| Устройство для вычисления логарифмических функций | 1978 |

|

SU771672A1 |

| Устройство для воспроизведения экспоненциальных функций | 1977 |

|

SU618746A1 |

| Вычислительное устройство | 1981 |

|

SU1008749A1 |

| Устройство для вычисления логарифмических функций | 1980 |

|

SU934469A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU826347A1 |

| Устройство для измерения полей давления в газотурбинном двигателе | 1980 |

|

SU909605A1 |

| Устройство для вычисления функций вида у=ах @ и у= @ | 1980 |

|

SU885998A1 |

Авторы

Даты

1981-05-30—Публикация

1978-05-22—Подача