(54) ФОРМИРОВАТЕЛЬ ВРЕМЕННОГО ИНТЕРВАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь временного интервала | 1974 |

|

SU680159A2 |

| Формирователь временного интервала | 1974 |

|

SU496669A1 |

| Формирователь временного интервала | 1973 |

|

SU457175A1 |

| Формирователь импульсов | 1985 |

|

SU1298871A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Устройство для синхронизации резервированного делителя частоты | 1981 |

|

SU1001104A1 |

| Цифровое устройство для обработки информации частотных датчиков | 1984 |

|

SU1239622A1 |

| Устройство для определения параметров изображения | 1985 |

|

SU1283814A1 |

| Преобразователь частота-код | 1983 |

|

SU1129543A1 |

1

Изобретение относится к импульсной технике, может быть использовано в радиоэлектронных устройствах для запоминания времейного интервала.

По основному авт. св. № 496660 известен формирователь временного интервала, который содержит кольцевую схему п последовательно соединенных ячеек задержки, два триггера и логический элемент И, причем входы 1-ой и К-ой ячеек .задержки подключены к источникам информационных сигналов, вход, одной или нескольких ячеек задержки и входы установки О триггеров соединены с источником опорного сигнала, счетные входы триггеров подключены к выходам 1-ой и К-ой ячеек задержки, а выходы триггеров соединены с элементом И 1.

Недостатком известного устройства является eifo низкое быстродействие (мало отношение максимальной длительности заЦоминаемого интервала времени к периоду генерации).

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в формирователь временного интервала, содержащий кольцевую схему п последователь

но соединенных ячеек задержки, -два триггера и логический элемент И, причем входы 1-ой и К-ой ячеек задержки подключены к источникам информационных сигналов, вход одной или нескольких ячеек задержки и входы установки О триггеров соединены с источником опорного сигнала, счетные входы триггеров подключенц к выходам 1-ой и К-ой ячеек задержки, а выходы триггеров соединены с элементом И, введены два дополнительных триггера со счетным входом,

0 элементы 2 И-ИЛИ, ЗИ-ИЛИ и коммутатор, входы которого подключены к выходам ячеек задержки и к шинам входного и опорного сигналов, выходы управления - ко входам 1-ой и К-ой ячеек задержки, а логические выходы - ко входам элемента

5 ЗИ-ИЛИ, вход первого элемента И которого соединен с выходом элемента 2И-ИЛИ вход второго элемента И - с выходом основного элемента И, вход третьего элемента И - с выходом первого основного триг. гера и со счетным входом первого дополнительного триггера, выходы которого подключены ко входам элемента 2И-ИЛИ, другие входы которого соединены с выходами второго дополнительного триггера, счетный

вход которого подключен к выходу второго основного триггера, а вход установки О - ко входу установки О первого дополнительного триггера и к шине опорного сигнала.

Коммутатор содержит три канала, каждый из которых состоит из последовательно соединенных элемента ИЛИ, первого элемента И, RS-триггера и второго элемента И, причем R-входы триггеров соединены и подклгсьчены к шине опорного сигнала, инверсный выход триггера одного канала подключен ко входам первых элементов И двух других каналов, прямые выходы триггеров являются логическими выходами коммутатора, при этом выходы вторых элементов И двух каналов объединены по ИЛИ, а все элементы И соединены между собой по одному входу.

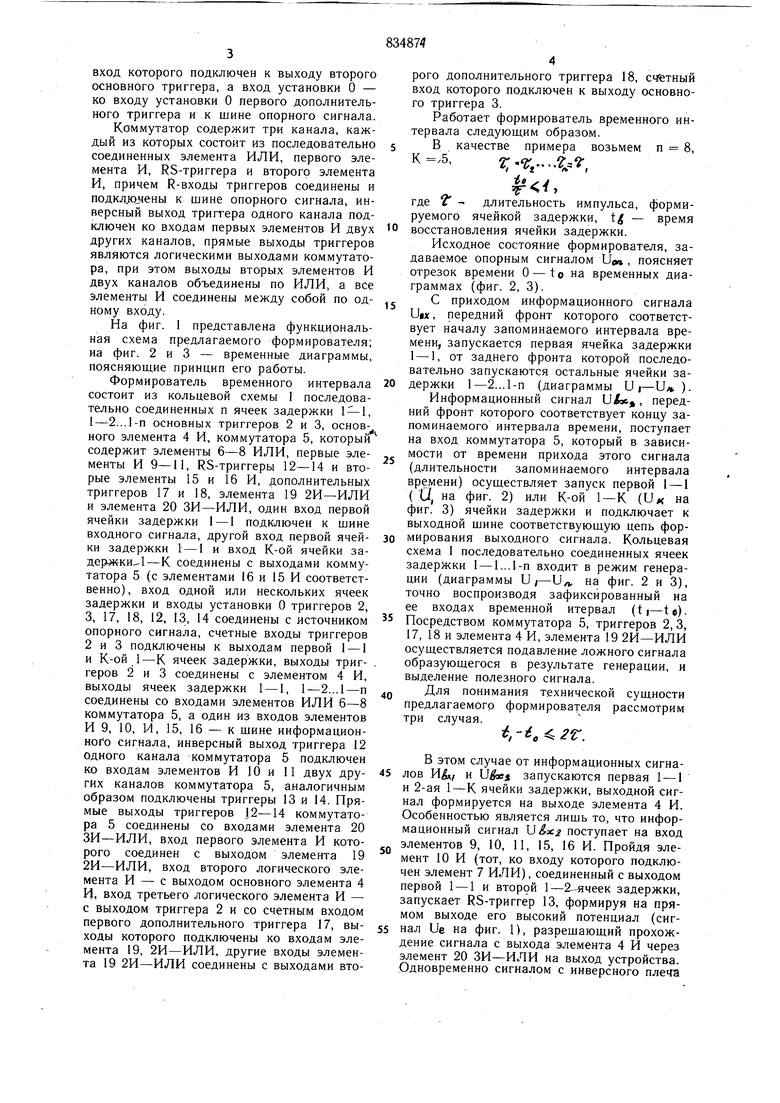

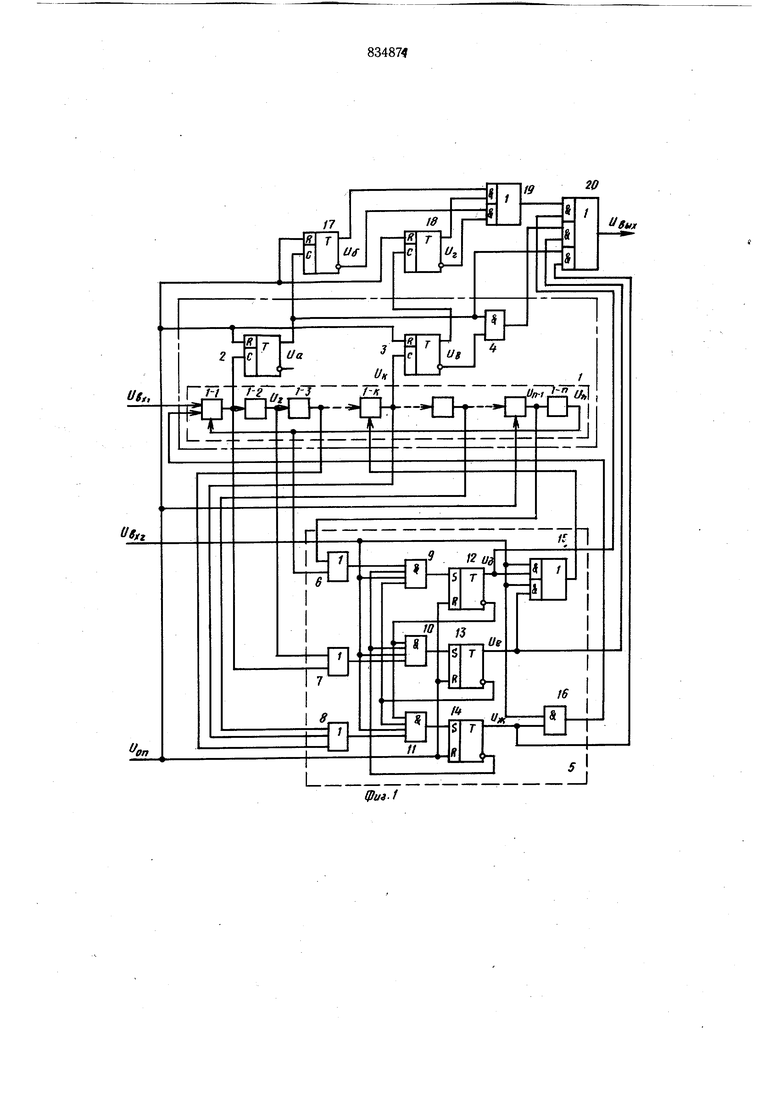

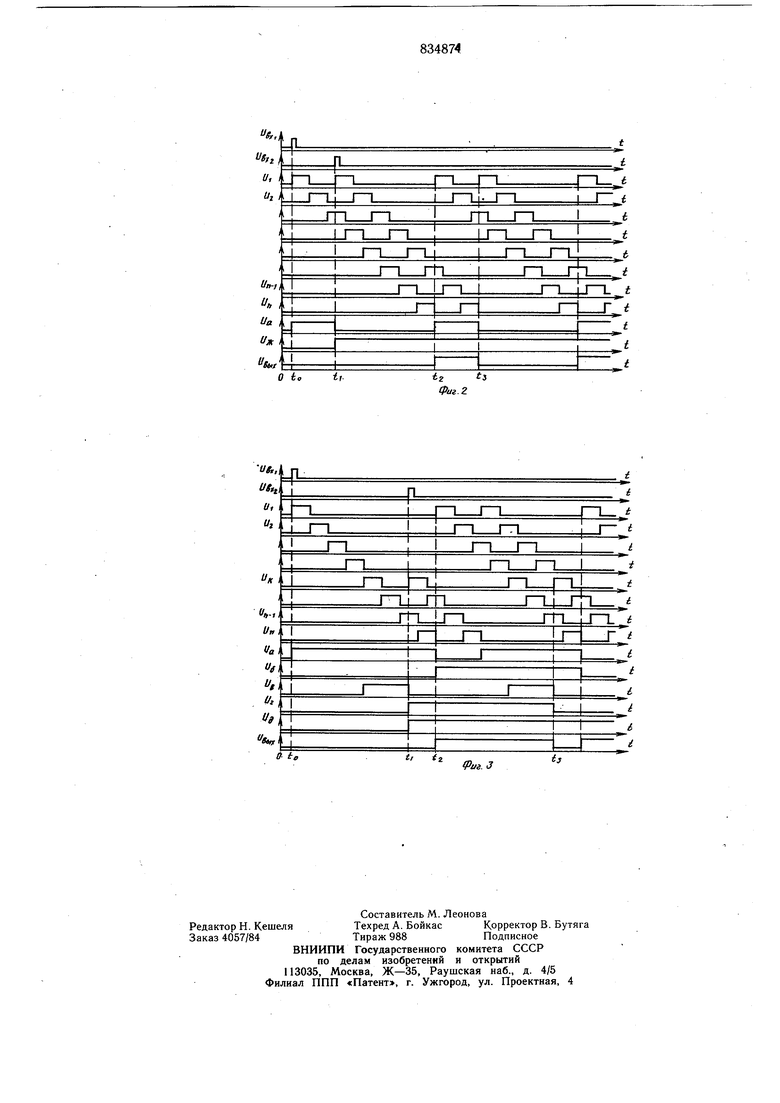

На фиг. I представлена функциональная схема предлагаемого формирователя; на фиг. 2 и 3 - временные диаграммы, поясняющие принцип его работы.

Формирователь временного интервала состоит из кольцевой схемы 1 последовательно соединенных п ячеек задержки , 1-2...1-П основных триггеров 2 и 3, основного элемента 4 И, коммутатора 5, который содержит элементы 6-8 ИЛИ, первые элементы И 9-11, RS-триггеры 12-14 и вторые элементы 15 и 16 И, дополнительных триггеров 17 и 18, элемента 19 2И-ИЛИ и элемента 20 ЗИ-ИЛИ, один вход первой ячейки задержки 1 - I подключен к шине входного сигнала, другой вход первой ячейки задержки 1 - I и вход К-ой ячейки задержки-- -К соединены с выходами коммутатора 5 (с элементами 16 и 15 И соответственно) , вход одной или нескольких ячеек задержки и входы установки О триггеров 2, 3, 17, 18, 12, 13, 14 соединены с источником опорного сигнала, счетные входы триггеров 2 и 3 подключены к выходам первой 1 - 1 и К-ой 1-К ячеек задержки, выходы триггерое 2 и 3 соединены с элементом 4 И, выходы ячеек задержки 1 - 1, 1-2...1-п соединены со входами элементов ИЛИ 6-8 коммутатора 5, а один из входов элементов И 9, 10, И, 15, 16 - к шине информационного сигнала, инверсный выход триггера 12 одного канала коммутатора 5 подключен ко входам элементов И 10 и 11 двух других каналов коммутатора 5, аналогичным образом подключены триггеры 13 и 14. Прямые выходы триггеров 12-14 коммутатора 5 соединены со входами элемента 20 ЗИ-ИЛИ, вход первого элемента И которого соединен с выходом элемента 19 2И-ИЛИ, вход второго логического элемента И - с выходом основного элемента 4 И, вход третьего логического элемента И - с выходом триггера 2 и со счетным входом первого дополнительного триггера 17, выходы которого подключены ко входам элемента 19, 2И-ИЛИ, другие входы элемента 19 2И-ИЛИ соединены с выходами второго дополнительного триггера 18, счётный вход которого подключен к выходу основного триггера 3.

Работает формирователь временного интервала следующим образом. В качестве примера возьмем п 8,

......, 1-ч-г,

где t - длительность импульса, формируемого ячейкой задержки, t - время

О восстановления ячейки задержки.

Исходное состояние формирователя, задаваемое опорным сигналом Ue , поясняет отрезок времени О - to на временных диаграммах (фиг. 2, 3).

С приходом информационного сигнала UM , передний фронт которого соответствует началу запоминаемого интервала времени, запускается первая ячейка задержки 1 - 1, от заднего фронта которой последовательно запускаются остальные ячейки задержки 1-2...1-П (диаграммы U|-U )Информационный сигнал UA,, передний фронт которого соответствует концу запоминаемого интервала времени, поступает на вход коммутатора 5, который в зависимости от времени прихода этого сигнала (длительности запоминаемого интервала времени) осуществляет запуск первой 1 - 1 (О, на фиг. 2) или К-ой 1-К (Ux на фиг. 3) ячейки задержки и подключает к выходной шине соответствующую цепь формирования выходного сигнала. Кольцевая схема I последовательно соединенных ячеек задержки 1 - l...l-п входит в режим генерации (диаграммы U/-U/ на фиг. 2 и 3), точно воспроизводя зафиксированный на ее входах временной итервал (t(-tc).

Посредством коммутатора 5, триггеров 2,3, 17, 18 и элемента 4 И, элемента 19 2И-ИЛИ осуществляется подавление ложного сигнала образующегося в результате генерации, и выделение полезного сигнала.

jj Для понимания технической сущности предлагаемого формирователя рассмотрим три случая.

,.2Т.

В этом случае от информационных сигналов ИА(, и запускаются первая 1 - 1 и 2-ая 1-К ячейки задержки, выходной сигнал формируется на выходе элемента 4 И. Особенностью является лищь то, что информационный сигнал &ж.2 поступает на вход элементов 9, 10, 11, 15, 16 И. Пройдя элемент 10 И (тот, ко входу которого подключен элемент 7 ИЛИ), соединенный с выходом первой 1 - 1 и второй 1-2-ячеек задержки, запускает RS-триггер 13, формируя на прямом выходе его высокий потенциал (сигнал Ue на фиг. П, разрешающий прохождение сигнала с выхода элемента 4 И через элемент 20 ЗИ-ИЛИ на выход устройства. Одновременно сигналом с инверсного плеча

триггера 13 осуществляется запрет запуска триггеров 12 и 14, обеспечивающих запрет прохождения сигналов с выхода триггера 2 и с выхода элемента 19 2И-ИЛИ на выход устройства.

2,-, .

в этом случае информационный сигнал Uexa через элемент 11 И, ко входу которого подключен элемент 8 ИЛИ, соединенный с выходами ячеек задержки 1-3...1-6, запускает триггер 14, формирующий сигнал УЖ (фиг. 1), разрешающий повторный запуск сигналом Uex2. ячейки задержки 1 - 1 и прохождение на выход устройства сигнала Ua, сформированного триггером 2 (сигналы . , Ит , и а Uewx на фиг. 1 и 2). Одновременно инверсным сигналом с триггера 14 обеспечивается запрет запуска других триггеров 13 и 12, предотвращающих выдачу ложной информации.

в этом случае информационный сигнал и й, через элемент 9 И, ко входу которого подключен элемент 6 ИЛИ, соединенный с выходами ячеек задержки 1--7, 1-8, запускает триггер 12, формирующий сигнал ид (см. фиг. 1), разрешающий запуск сигналом UeX2 ячейки задержки 1-к и прохождение на выход устройства сигнала с выхода элемента 19 2И-ИЛИ (фиг. 1 и 3).

Одновременно инверсным сигналом с триггера 12 предотвращается запуск других триггеров 13 и 14.

Быстродействие формирователя наглядно поясняют временные диаграммы, где отнощение максимальной длительности запоминаемого интервала времени (t/-to)/nax к периоду генерации Т равно 1.

Быстродействие известного формирователя определяется количеством ячеек задержки, включенных между первой и К-ой ячейками задержки,.и для ячеек задержки - ,i;i. и у 4 1, т. е. таких же, как и в предложенном формирователе, связано с колическом ячеек задержки п выражением п -.-т-, где f iij fiiax коэффициент, характеризующий быстродействие устройства. Или ( 1 - , т.,е. f 1 при п ,

что практически не реализуемо.

Формула изобретения 5

0 ИЛИ, ЗИ-ИЛИ и коммутатор, входы которого подключены к выходам ячеек задержки и к щинам входного и опорного сигналов, выходы управления ко входам 1-ой и К-ой ячеек задержки, алогические выходы5 ко входам элемента ЗИ-ИЛИ, вход первого элемента И которого соединен с выходом элемента 2И-ИЛИ, вход второго элемента И - с выходом основного элемента И, вход третьего элемента И - с выходом первого основного триггера и со счетным

0 входом первого дополнительного триггера, выходы которого подключены ко входам элемента 2И-ИЛИ, другие входы которого соединены с выходами второго дополнительного триггера, счетный вход которого подключен к выходу второго основного тригге5ра, а вход установки О - ко входу установки О первого дополнительного триггера и к шине опорного сигнала.

5 подключен ко входам первцх элементов И двух других каналов, прямые выходы триггеров являются логическими выходами ком.мутатора, при этом выходы вторых элементов И двух каналов объединены по ИЛИ, а все остальные элементы И соединены между собой по одному входу.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 496669, кл. Н 03 К 5/153, 03.06.74.

,

l te

t, fi

lput.3

Авторы

Даты

1981-05-30—Публикация

1977-07-14—Подача