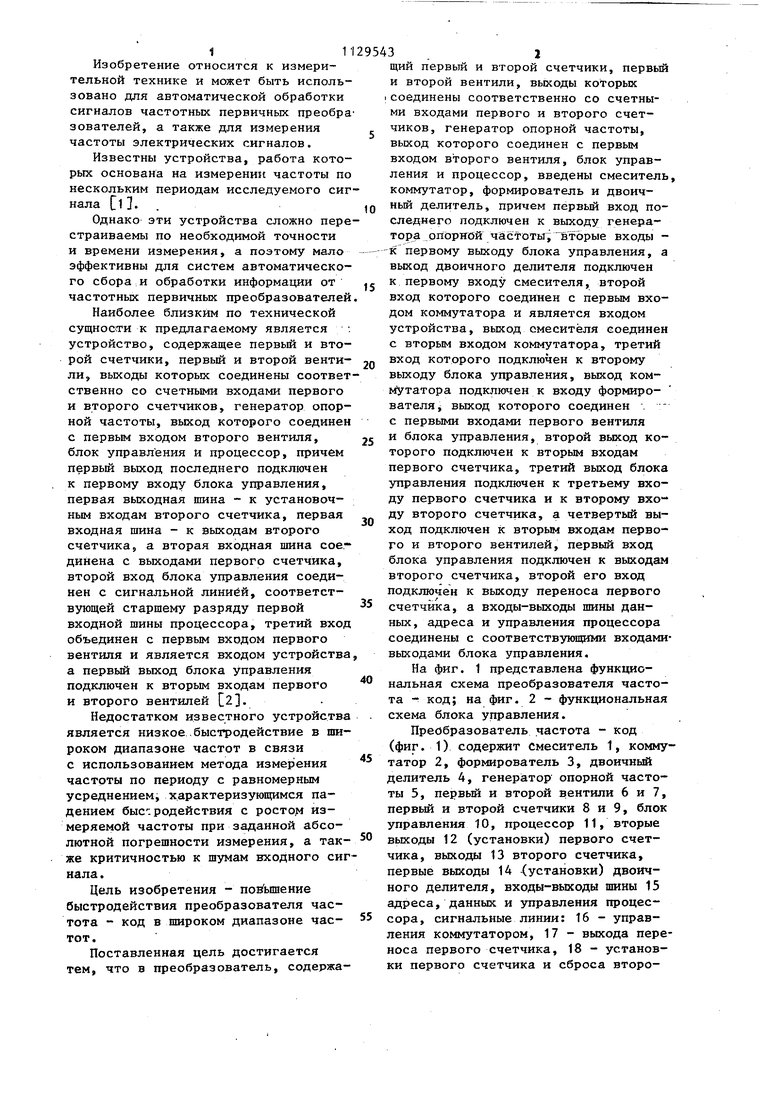

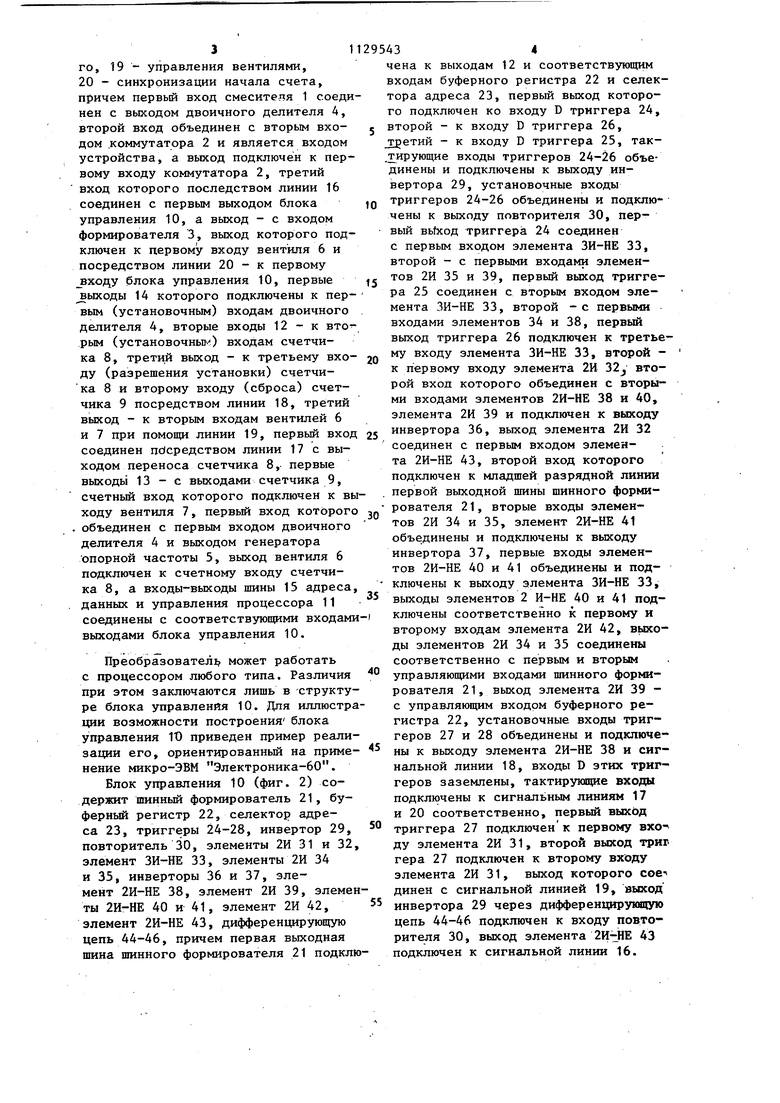

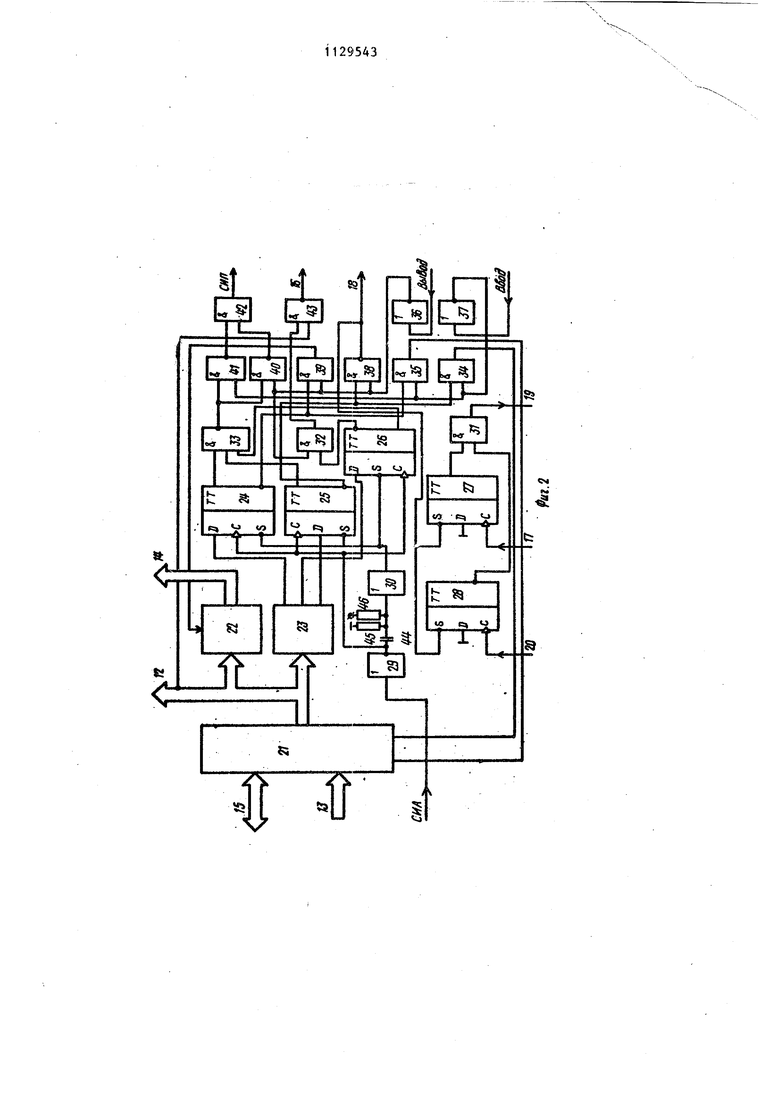

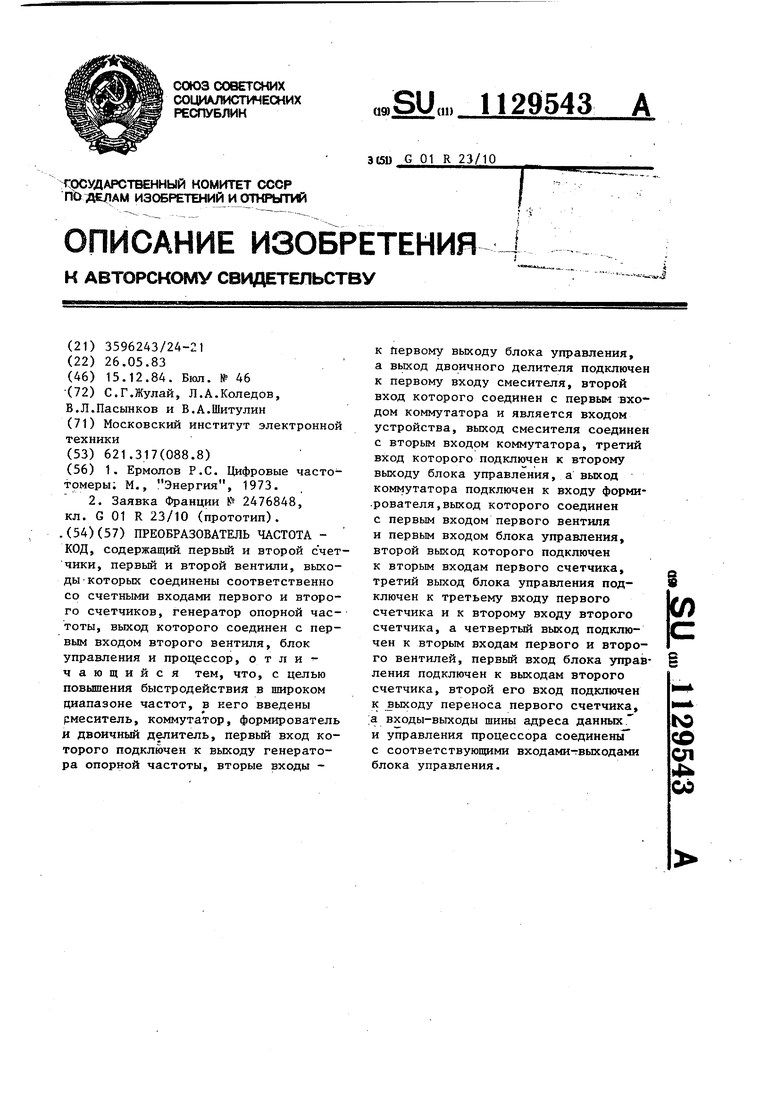

Изобретение относится к измерительной технике и может быть использовано для автоматической обработки сигналов частотных первичных преобра зователей, а также для измерения частоты электрических сигналов. Известны устройства, работа которых основана на измерении частоты по нескольким периодам исследуемого сиг нала l. . Однако эти устройства сложно пере страиваемы по необходимой точности и времени измерения, а поэтому мало эффективны для систем автоматического сбора и обработки информации от частотных первичных преобразователей Наиболее близким по технической сущности к предлагаемому является устройство, содержащее первый и второй счетчики, первый и второй вентили, выходы которых соединены соответ ственно со счетными входами первого и второго счетчиков, генератор опорной частоты, выход которого соединен с первым входом второго вентиля, блок управления и процессор, причем первый выход последнего подключен к первому входу блока управления, первая выходная шина - к установочным входам второго счетчика, первая входная шина - к выходам второго счетчика, а вторая входная шина соединена с выходами первого счетчика, второй вход блока управления соединен с сигнальной линией, соответствующей старшему разряду первой входной шины процессора, третий вход объединен с первым входом первого вентиля и является входом устройства а первый выход блока управления подключен к вторым входам первого и второго вентилей 2. Недостатком известного устройства является низкое-быстродействие в широком диапазоне частот в связи с использованием метода измерения частоты по периоду с равномерным усреднением, характеризующимся падением быс.родействия с ростом измеряемой частоты при заданной абсолютной погрешности измерения, а также критичностью к шумам входного сиг нала. Цель изобретения - быстродействия преобразователя частота - код в широком диапазоне час тот. Поставленная цель достигается тем, что в преобразователь, содержащий первый и второй счетчики, первый и второй вентили, вь1ходы которых соединены соответственно со счетными входами первого и второго счетчиков, генератор опорной частоты, выход которого соединен с первым входом второго вентиля, блок управления и процессор, введены смеситель, коммутатор, формирователь и двоичный делитель, причем первый вход последнего подключен к выходу генератора рлорной частоты вторые входы - к первому выходу блока управления, а выход двоичного делителя подключен к первому входу смесителя, второй вход которого соединен с первым входом коммутатора и является входом устройства, выход смесителя соединен с вторым входом коммутатора, третий вход которого подключен к второму выходу блока управления, выход коммутатора подключен к входу формирователя j выход которого соединен . с первыми входами первого вентиля и блока управления, второй выход которого подключен к вторым входам первого счетчика, третий выход блока управления подключен к третьему входу первого счетчика и к второму входу второго счетчика, а четвертый выход подключен к вторьм входам первого и второго вентилей, первый вход блока управления подключен к выходам второго счетчика, второй его вход подключен к выходу переноса первого счетчика, а входы-выходы шины данных, адреса и управления процессора соединены с соответствующими входамивыходами блока управления. На фиг. 1 представлена функциональная схема преобразователя частота - код; на фиг. 2 - функциональная схема блока управления. Преобразователь частота - код (фиг. 1) содержит смеситель 1, коммутатор 2, формирователь 3, двоичный делитель 4, генератор опорной частоты 5, первый и второй вентили 6 и 7, первый и второй счетчики 8 и 9, блок управления 10, процессор 11, вторые выходы 12 (установки) первого счетчика, выходы 13 второго счетчика, первые выходы 14 установки) двоичного делителя, входы-выходы шины 15 адреса, данных и управления процессора, сигнальные линии: 16 - управления коммутатором, 17 - выхода переноса первого счетчика, 18 - установки первого счетчика и сброса второго, 19 - управления вентилями, 20 - синхронизации начала счета, причем первьй вход смесителя 1 соеди нен с выходом двоичного делителя 4, второй вход объединен с вторым входом коммутатора 2 и является входом устройства, а выход подключён к первому входу коммутатора 2, третий вход которого последством линии 16 соединен с первым выходом блока управления 10, а выход - с входом формирователя 3, выход которого подключен к первому входу вентиля 6 и посредством линии 20 - к первому блока управления 10, первые Лыходы 14 которого подключены к первым (установочным) входам двоичного делителя 4, вторые входы 12 - к вторым (установочньв О входам счетчика 8, третий выход - к третьему входу (разрешения установки) счетчика 8 и второму входу (сброса) счетчика 9 посредством линии 18, третий выход - к вторым входам вентилей 6 и 7 при помощи линии 19, первый вход соединен пс/средством линии 17 с выходом переноса счетчика 8, первые выходы 13 - с выходами счетчика 9, счетный вход которого подключен к вы ходу вентиля 7, первый вход которого . объединен с первым входом двоичного делителя 4 и выходом генератора опорной частоты 5, выход вентиля 6 подключен к счетному входу счетчика 8, а входы-выходы шины 15 адреса данных и управления процессора 11 соединены с соответствующими входами выходами блока управления 10. Преобразователь может работать с процессором любого типа. Различия при этом заключаются лишь в -структуре блока управления 10. Для иллюстра ции возможности построения блока управления 1t) приведен пример реализации его, ориентированный на применение микро-ЭВМ Электроника-60. Блок управления 10 (фиг. 2) содержит шинный формирователь 21, буферный регистр 22, селектор адреса 23, триггеры 24-28, инвертор 29, повторитель 30, элементы 2И 31 и 32 элемент ЗИ-НЕ 33, элементы 2И 34 и 35, инверторы 36 и 37, элемент 2И-НЕ 38, элемент 2И 39, элемен ты 2И-НЕ 40 и 41, элемент 2И 42, элемент 2И-НЕ 43, дифференцирующую цепь 44-46, причем первая выходная шина шинного формирователя 21 подклю чека к выходам 12 и соответствующим входам буферного регистра 22 и селектора адреса 23, первый выход которого подключен ко входу D триггера 24, второй - к входу D триггера 26, третий к входу D триггера 25, такгирующие входы триггеров 24-26 объединены и подключены к выходу инвертора 29, установочные входы триггеров 24-26 объединены и подключены к выходу повторителя 30, первый вь1ход триггера 24 соединен с первым входом элемента ЗИ-НЕ 33, второй - с первыми входами элементов 2И 35 и 39, первый выход триггера 25 соединен с вторым входом элемента ЗИ-НЕ 33, второй -с первыми входами элементов 34 и 38, первый выход триггера 26 подключен к третьему входу элемента ЗИ-НЕ 33, второй к первому входу элемента 2И 32 второй вход которого объединен с вторыми входами элементов 2И-НЕ 38 и 40, элемента 2И 39 и подключен к выходу инвертора 36, выход элемента 2И 32 соединен с первым входом элемента 2И-НЕ 43, второй вход которого подключен к младшей разрядной линии первой выходной шины шинного формирователя 21, вторые входы элементов 2И 34 и 35, элемент 2И-НЕ 41 объединены и подключены к выходу инвертора 37, первые входы элементов 2И-НЕ 40 и 41 объединены и подключены к вьЕходу элемента ЗИ-НЕ 33, выходы элементов 2 И-НЕ 40 и 41 подключены соответственно к первому и второму входам элемента 2И 42, выходы элементов 2И 34 и 35 соединены соответственно с первым и вторым управляющими входами шинного формирователя 21, выход элемента 2И 39 с управляющим входом буферного регистра 22, установочные входы триггеров 27 и 28 объединены и подключены к выходу элемента 2И-НЕ 38 и сигнальной линии 18, входы D этих триггеров заземлены, тактируннцие входы подключены к сигнальным линиям 17 и 20 соответственно, первый выход триггера 27 подключен к первому вхо- ду элемента 2И 31, второй выход триг гера 27 подключен к второму входу элемента 2И 31, выход которого сое- динен с сигнальной линией 19, выход инвертора 29 через дифференцирующую цепь 44-46 подключен к входу повторителя 30, выход элемента 2И-НЕ 43 подключен к сигнальной линии 16. 511 Сигнальные линии синхроимпульс активный (сил), синхроимпульс пассивный (СИП), входящие в шину 15, являются управляющими для процессор 1 микро-ЭВМ Электроника-60 и вьшолня ют следуюпще функции. СИЛ служит для идентификации адреса внешнего устрой ства на шине 15. При этом во время всего цикла обмена процессора с указанным устройством на данной линии (Поддерживается низкий логический уровень. СИП формируется внешним VCTройством (в данном случае блоком управления 10). Его низкий уровень информирует процессор в цикле Вывод о конце приема данных из процессора, а в цикле наличии выводимых в процессор данных на шине 15. Выход элемента 2И 42 подключен к сигнальной линии СИП шины адреса, данных и управления процессора, вход инвертора 29 - к сигнальной линии СИЛ шины адреса, данных и управления: процессора, входы- инверторов 36 и 37 - к сигнальным линиям Вывод и Ввод шины адреса, данных и управления процессора соответственно, выходы буферного регистра 22 соедине ны с выходами 14, первая входная шина шинного формирователя 21 - с вы ходами 13о . Блок управления 10 выполняет следующие функции: обеспечивает передачу с шины 15 на установочные входы первого счетчика 8 по выходам 12 кода числа измеряемых периодов, а на установочные входы двоичного делителя 4 по выходам 14 - кода коэффициента деления; обеспечивает прием кода измеренных периодов с выходов 13 на шину 15; селектирует адреса двоич ного делителя 4, счетчиков 8 и 9, коммутатора 2; вьфабатывает сигналы, управляющие работой вентилей 6 и 7, счетчиков 8 и 9, коммутатора 2. Сущность работу преобразователя заключается в том, что измерению под вергается не сама неизвестная частота f,, , а разность f,., формируемая смесителем, между ней и некоторой опорной частотой f uf,, причем последняя автоматически регулируется таким образом, чтобы эта разность лежала в окрестности некоторого наперед зада.ннЬго значения частоты f цо . Частота fon вьфабатывается делением часто ты опорного генератора f,,, причем 3 коэффициент деления рассчитывается процессором и записывается в двоичный делитель. Необходимая величина fp fjj-+f определяется путем прикидочного измерения частоты fj( за малое время. Оно осуществляется подключением при помощи коммутатора измеряемой частоты через формирователь непосредственно на вход первого вентиля и подсчетом числа импульсов опорной частоты, поступающих на счетный вход второго счетчика за время, равное длительности выбранного числа периодов измеряемой частоты, которое задается предварительной установкой первого счетчика. Поскольку абсолютная погрешность измерения равна аналогичной для f, (в пренебрежении погрешностью установки fjj), а f может быть существенно меньше f , происходит уменьшение времени измерения в раз. Усттойство работает следующим образом. С помощью коммутатора 2 сигнал измеряемой частоты f посредством линии 16 подключается к входу формирователя 3, осуществляющего его преобразование в прямоугольные импульсы нужной амплитуды. Процессор 11 помещает на выходы 12, соединенные с установочными входами счетчика 8, код начального числа периодов исследуемого сигнала. Одновременно по линии 18 выдается сигнал разрешения установки счетчика 8 и сброса счетчика. После снятия сигнала С линии 18 по первому фронту измеряемого сигнала, поступающего в блок управления 10 по линии 205 там вьфабатывается сигнал, который посредством линии 19 открывает вентили-6 и 7, обеспечивая тем самым поступление измеряемого сигнала на вычитающий вход счетчика 8 и опорного сигнала на.суммирующий вход счетчика 9, В момент своего обнуления счетчик 8 выдает по линии 17 в блок управления сигнал, обеспечивающий снятие открывающего уровня на линии 19 и запирание вентилей 6 и 7. Таким образом, содержимое счетчика 9 пропорционально длительности начального числа измеряемых периодов. Процессор 11 принимает данные из счетчика 9 (из выходов 13) и рассчитывает частоту по формуле f S f Х HOW ш °

где n - число измеряемых периодов,

записываемое в счетчик 8; га - содержимое счетчика 9; fg - частота опорного генератора. Процессором 11 определяется значе ние коэффициента деления: fo

+f

-X ном

ко

где f - выбранное значение выходной частоты смесителя 1.

Это число округляется до ближайшего большего целого числа К и засылается в двоичный делитель посредством выходов 14. При этом на выходе двоичного делителя 4 появится сигнал с частотой fр/к, а на выходе смесителя 1 - с частотой f f JJ/К--f „ .

С помощью коммутатора 2 выход смесителя 1 посредством линии 16 подключается к входу формирователя 3. .Далее производится в описанном порядке измерение частоты ц с необхо«димой абсолютной погрешностью. После этого процессор 11 рассчитывает значение измеряемой частоты:

f, ,.

Таким образом, общее время измерения частоты f с абсолютной погрешностью 4f складывается из времени Начального измерения, которое носит прикидочный характер и может быть очень быстрым, и времени измерения частоты f, с погрешностью д, причем f выбирается меньшей f,, а этим методом по периоду измеряется в раз быстрее.

Блок управления 10 работает следующим образом.

Обращение к счётчикам 8 и 9, двоичному делителю 4, коммутатору 2 со стороны процессора 11 осуществляется как к обычным ячейкам памяти, причем используются общие адреса для счетчика 8 и младщих двух байтов счетчика 9, двоичного делителя 4 и старших разрядов счетчика 9 и отдельный адрес для коммутатора 2. В начальном состоянии шинньй формирователь 21 включен на прием адреса-данных из шины 15 процессора 11. По отрицательному фронту сигнала СИЛ, поступающего из процессора 11, происходит дешифрация адреса в селекторе адреса 23, и состояние его выходов записывается в триггеры 24-26. Выборка нужного адреса соответствует нулевому уровню на одном из выходов селектора адреса 23, Далее в зависимости от режима обмена процессор 11 вырабатывает нулевые сигналы Ввод или Вывод. В первом случае инициируется появление единичных уровней на выходах элементов 2И 34 и 35, которые переключают шинный формирователь 21 на прием данных в шину 15 по выходам 13 из младших или старших разрядов счетчика 9 соответственно. Во втором случае вырабатывается либо единичный уровень на выходе элемента 2И 39, разрешающий запись данных из шины 15 в буферный регистр 22, выходы которого соединены с установочными входами двоичного делителя 4 посредством линии 14, либо нулевой на выходе элемента 2И-НЕ 38. поступающий по линии 18 на входы разрешения установки счетчика 8 и сброса счетчика 9, а также устанавливающий триггеры 27 и 28, либо младший разряд шины 15 посредством линии 16, подключенной к выходу элемента 2И-НЕ 43, соединяется с управляющим входом коммутатора 2. По первому фронту импульса измеряемой частоты, поступившему на тактовьш вход триггера 28 по линии 20 после окончания сигнала Вывод, происходит опрокидывание триггера 28 и появление единичного сигнала на выходе элемента 2И 31, открывающего посредством линии 19 управляющие вентили 6 и 7. При обнулении счетчика 8 в нем вырабатывается импульс переноса, обнуляющий по линии 17 триггер 27 и тем самым сбрасывающий единичный уровень на линии 19. Появление нулевого уровня на одном из входов элемента ЗИ-НЕ 33 соответствующее выборке одного из адресов, при наличии инвертированных сигналов Ввод или Вывод на вхо-г. дах элементов 2И-НЕ 41 и 40 соответственно

вызывает появление на выходе элемента 2И 42 нулевого уровня сигнала СИП, который информирует процессор 11 при выводе о конце приема данныз5, а при вводе - о наличии выводимых данных на шине 15. По положительному фронту сигнала СИА, свидетельствующему о конце обмена, при помощи дифференцирующей цепи 4446 и повторителя 30 происходит формирование отрицательного импульса, устанавливающего триггеры 24-26 в начальное единичное состояние. : Сигнальные линии СИА, Ввод, Вывод, СИП на фиг. 1 входят в соетав шины 15 адреса, данных и управпения процессора 11. Частоту выходе смесителя мож но вьщелять с помощью узкополосного фильтра с центральной частотой f , что способствует подавлению аддитивных шумов. Предположим, что послед-; ние обусловлены в основном выходными шумами датчика и Занимают полосу частот, равную максимальной полезной девиации его частоты , Допустим что они представляют собой нормальный стационарный процесс с нулевым средним и равномерным в указанной полосе хчастот энергетическим спектром (типичный для практики случай). В этом случае фильтр с полосой пропускания обеспечивает уменьшение среднеквадратического зна чения шума в m раз, где число m равноil&fmat f f-Таким образом, в данном случае время измерения не зависит от частоты входного сигнала и составляет йеличинугае и«« - амплитуда сигнала; бд, - среднеквадратичное значение шума на входе преобразовате .ля; 6 - необходимая абсолютная дис персия измерения частоты. При этом для частот f f ц +1/2Л оно может уменьшаться более чем в fy/(fj,+1/2f) раз по сравнению х с тактовым у прототипа при том же значении А. Оценим рабочий диапазон частот предлагаемого преобразователя. Если выполняются следующие условия: амшш туда входного сигнала с частотой fу подаваемого на смеситель, выбрана та кой, чтобы обеспечивался линейный режим работы последнего; в качестве гетеродинного используется сигнал с выхода делителя, то на выходе смесителя наряду с полезной частотой возникают комбинационные частоты видаfon. |fon-nfx. где п 2,3,4,0.. . Для их подавления достаточно выполнения условия х т;п- -2нс+л „. - минимальное значение измеряемой частоты. Округление коэффициента деления К до ближайшего большего целого числа к приводитк отклонению частоты f от f ij, на максимальную величину ( )/f д . Чтобы н не выходила за пределы полосы пропускания flf выходного фильтра смесителя, необходимо выполнение условия д ikiljlS.li откуда имеем максимальное значение измеряемой частоты оЛ«п Таким образом, рабочий диапазон частот преобразователя составляет величину 2fHo- fn V fM n . Например, при МГц, ко кГц, кГц 13 кГц Вне этого диапазона данный преобразователь может работать как прототип. Структура преобразоватёля частота - код позволяет повысить производительность труда за счет сокращения времени измерения, ручного труда и рабочего времени при настройке, регулировке и ремонте прибора, а также автоматизации процесса измерения, кроме того, сократить объем и номенклатуру кoнtpoльнo-измepи тельного оборудования за счет обслуивания широкого набора разнопшнных первичных преобразователей с необхо-имьит точностью и быстродействием.

il

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля качества часовых механизмов | 1986 |

|

SU1332257A1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094815C1 |

| Фазометр | 1985 |

|

SU1273837A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Измеритель переходных характеристик частотных прецизионных устройств | 1987 |

|

SU1620992A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для управления фотоколориметрическим газоанализатором | 1982 |

|

SU1092468A1 |

| Термографический регистратор | 1984 |

|

SU1174288A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА КОД, содержащий первый и второй счетчики, первый и второй вентили, выходы -которых соединены соответственно со счетными входами первого и второго счетчиков, генератор опорной частоты, выход которого соединен с первым входом второго вентиля, блок управления и процессор, о т л и чающийся тем, что, с целью повышения быстродействия в широком диапазоне частот, в него введены рмеситель, коммутатор, формирователь и двоичный делитель, первый вход которого подключен к выходу генератора опорной частоты, вторые входы к йервому выходу блока управления, а вькод двоичного делителя подключен к первому входу смесителя, второй вход которого соединен с первым входом коммутатора и является входом устройства, выход смесителя соединен с вторым входом коммутатора, третий вход которого подключен к второму выходу блока управления, а выход коммутатора подключен к входу форми.рователя,выход которого соединен с первым входом первого вентиля и первым входом блока управления, второй выход которого подключен к вторым входам первого счетчика, § третий выход блока управления подключен к третьему входу первого счетчика и к второму входу второго счетчика, а четвертый выход подключен к вторым входам первого и второго вентилей, первый вход блока управления подключен к выходам второго счетчика, второй его вход подключен к выходу переноса первого счетчика, 1С ;а входы-выходы шины адреса данных. и управления процессора соединены СО ел с соответствующими входами-выходами блока управления. оо

7Г

1

u:

fo

ч

7гг

v

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ермолов Р.С | |||

| Цифровые частотомеры; М., Энергия, 1973 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ ДАТЧИКОВ МАССОВОГО РАСХОДА ВОЗДУХА НА АВТОМОБИЛЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2476848C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| . | |||

Авторы

Даты

1984-12-15—Публикация

1983-05-26—Подача