(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь ток-частота с импульсной обратной связью | 1986 |

|

SU1451863A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1559407A2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1510087A1 |

| Интегрирующий преобразователь тока в код | 1989 |

|

SU1741264A1 |

| Биполярный преобразователь ток-частота | 1985 |

|

SU1277400A1 |

| УСТРОЙСТВО ДЛЯ БЕСКОНТАКТНОГО ИЗМЕРЕНИЯ ИМПУЛЬСНЫХ ТОКОВ | 1990 |

|

RU2024025C1 |

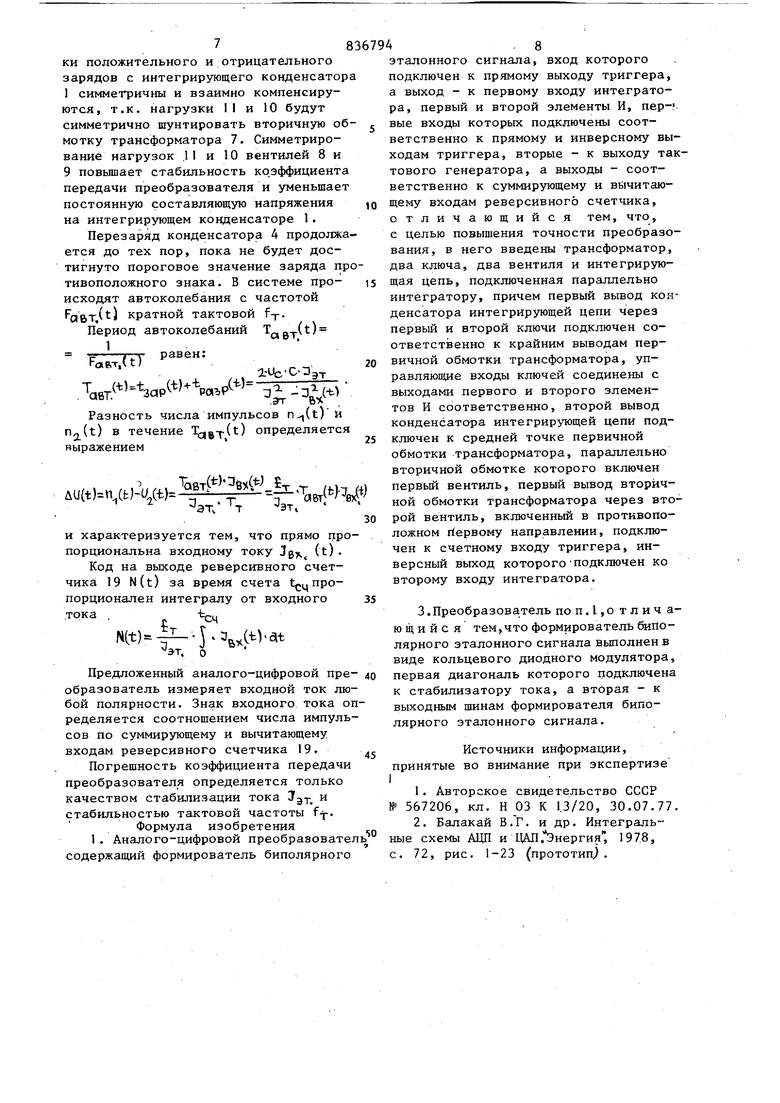

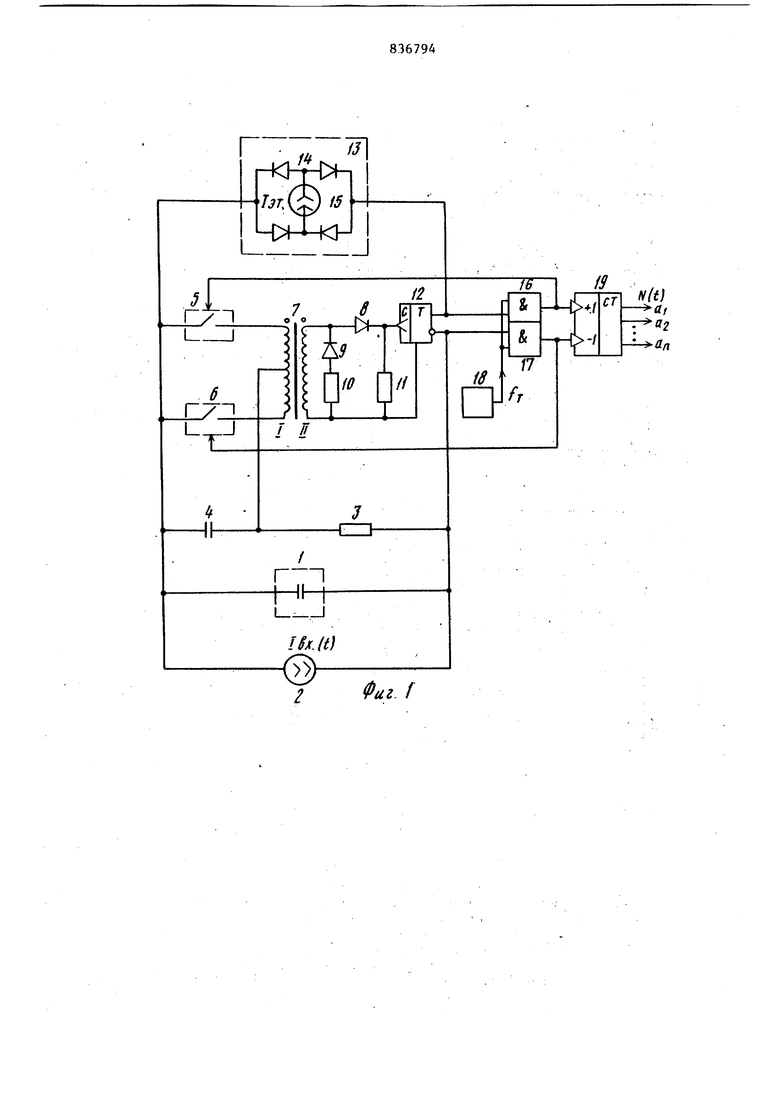

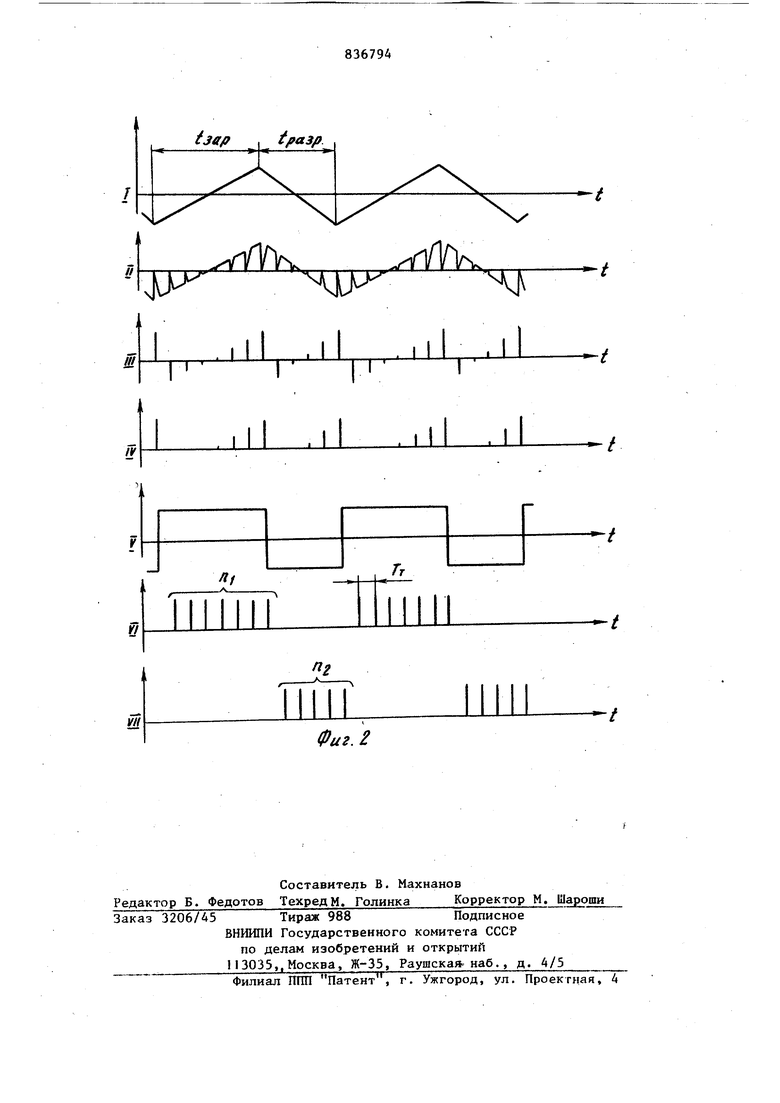

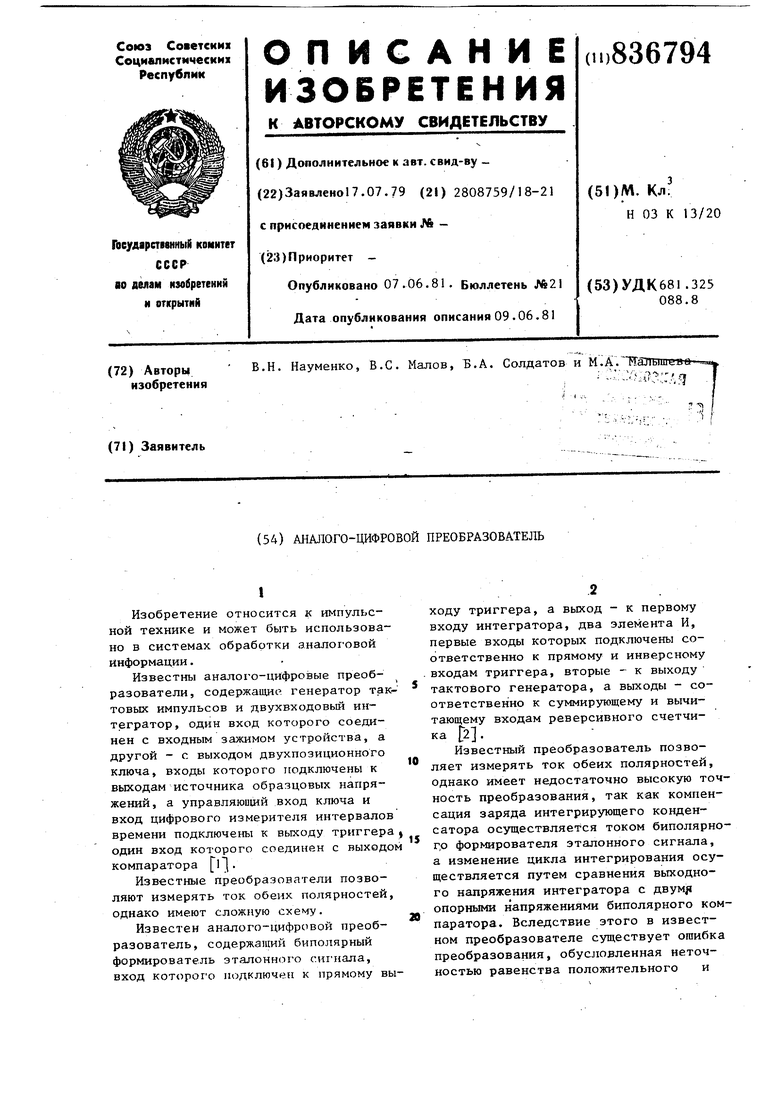

Изобретение относится к импульсной технике и может быть использовано в системах обработки аналоговой информации. Известны аналого-цифровые преобразователи, содержащие генератор так товых импульсов и двухвходовый интегратор, один вход которого соединен с входным зажимом устройства, а другой - с выходом двухпозиционного ключа, входы которого подключены к выходам источника образцовых напряжений, а управляюишй вход ключа и вход цифрового измерителя интервалов времени подключены к выходу триггера один вход которого соединен с выходо компаратора l. Известные преобразователи позволяют измерять ток обеих полярностей однако имеют сложную схему. Известен аналого-цифровой преобразователь, содержащий биполярный формирователь эталонного гигнала, вход которого подключен к прямому вы ходу триггера, а выход - к первому входу интегратора, два элемента И, первые входы которых подключены соответственно к прямому и инверсному входам триггера, вторые - к выходу тактового генератора, а выходы - соответственно к суммирующему и вычитающему входам реверсивного счетчика Г2. Известный преобразователь позволяет измерять ток обеих полярностей, однако имеет недостаточно высокую точность преобразования, так как компенсация заряда интегрирующего конденсатора осуществляет ся током биполярног,о формирователя эталонного сигнала, а изменение цикла интегрирования осуществляется путем сравнения выходного напряжения интегратора с опорными напряжениями биполярного компаратора. Вследствие этого в известном преобразователе существует ошибка преобразования, обусловленная неточностью равенства положительного и отрицательного токов биполярного фор мирователя эталонного сигнапа и опор ных напрйжений биполярного компаратора. Целью изобретения является повышение точности преобразования. . Указанная цель достигается тем, что в известный аналого-цифровой пре образователь, содержащий формировате биполярного эталонного сигнала, вход которого подключен к прямому выходу триггера, а выход - к первому входу интегратора, два элемента И, первые входы которых подключены соответст-. .венно к прямому « инверсному выходам триггера, вторые - к выходу тактового генератора, а выходы - соответственно к суммирующему и вычитающему входам реверсивного счетчика , введены трансформатор, два ключа, два вен тиля и интегрирующая цепь, подключенная параллельно интегратору, причем первый вывод конденсатора интегрирующей цепи через первый и второй ключи подключен соответственно к кра ним выводам первичной обмотки трансформатора, управляющие входы ключей соединены с выходами первого и второго элементов И соответственно, вто рой вывод конденсатора интегрирующей цепи подключен к средней точке первичной обмотки- трансформатора, параллельно вторичной обмотке которого включен первый вентиль, первьш вывод вторичной обмотки трансформатора через второй вентиль, включенный в противоположном первому направ лению, подключен к счетному входу триггера, инверсный выход которого подключен ко второму входу интегратора, а формирователь биполярного эталонного сигнала выполнен в виде кольцевого диодного модулятора, первая диагональ которого подключена к стабилизатору тока, а вторая - к выходным щинам формирователя биполярного эталонного сигнала. На фиг. 1 представлена принципиальная электрическая схема предлагаемого аналого-цифрового преобразователя . Схема содержит интегратор 1, к входам которого подключен источник входного тока 2, интегрирующзто цепь, состоящую из резистора 3 и конденсатора 4, ключи 5,6, импульсный тран сформатор 7, вентили 8, 9, резисторы 10 и 11, триггер со счетным уходом 12, формирователь биполярного эталон ного сигнапа 13, состоящий из кольцевого диодного модулятора 14 и однополярного стабилизатора тока 15,элементы И 16-17, тактовый генератор 18 и реверсивный счетчик 19. На фиг. 2 приведены временные диаграммы устройства, иллюстрирующие его работу, где: I- напряжение на выводах интегратора 1; II- напряжение на выводах конденсатора 4 интегрирующей цепи; Ml- импульсы во вторичной обмотке трансформатора 7; IV - импульсы на входе счетного триггера 12; V- напряжение между прямым и инверсным выходами триггера 12; VI- импульсы по суммирующему входу реверсивного счетчика 19; VII- импульсы по вычитающейу входу реверсивного счетчика 19. Преобразование тока в цифровой код основано на принципе сравнения „„тегралов от входного и эталонного ТОКОВ. Предложенный аналого-цифровой преобразователь работает следующим образом. Под действием тока, определяемого алгебраической суммой dg, источника тока 2 и Зд стабилизатора тока 15, протекающего через кольцевой диодный модулятор 14, прямой и инверсный выходы триггера 12, происходит заряд емкости интегратора 1 (см.фиг.2|). В качестве интегратора применяется высококачественный конденсатор. Если на прямом выходе триггера 12 высокий потенциал (логическая 1), на инверсном - низкий (О), то ток стабилизатора 15 протекает через два открытых диода кольцевого модулятора 14, интегрирующий конденсатор 1, инверсный выход триггера, 12, его йсточник питания и прямой выход триггера 12. При этом время заряда конденсатора 1 UcC .(Ч ,;Г5;;щ. где С - емкость конденсатора 1. Импульсный трансформатор 7, ключи 5,6, вентили 8,9, резисторы 10,11 и интегрирующая цепь 3,4 образуют логическое устройство сравнения. Выводы интегрирующей цепи 3,4 образуют ее аналоговый вход. Напряжение с интегрирующего конденсатора подается на аналоговый вход 1. Управляющие входы ключей 5 и 6 образуют импульсные входы II и III логического устрой ства сравнения, на них поступают импульсы с выходов элементов И I6 и 17 (см. фиг. 2 VI.VII) Логическое устройство сравнения производит проверку знака и величины заряда интегрирующего конденсатора I Выходом 1 логического устройства сравнения является резистор 1I,выходом II - резистор 10. Если на прямом выходе триггера 12 1, на инверсном О, то импульсы тактовой частоты проходят на выход элемента И 16 и управляющий, вход ключа 5. При этом на выходе элемента И 17 и управляющем входе ключа 6 тактовых импульсов нет.. Реверсивный счетчик 19 производит подсчет числа импульсов п (t) тактовой частоты.f по суммирующему входу в течение времени ). Число импульсовn(t) tt,)/T-r где Т - период тактовой частоты. Конденсатор 4 интегрирующей цепи подзаряжается от интегрирующего конденсатора 1 через резистор 3 в течение TT и разряжается с тактовой частотой f-f- через ключ 5, который откры вается по входу И в течение времени V, , равного длительности тактового импульса, и первичную обмотку импуль ного трансформатора 7 (см.фиг.2 И). При этом ключ 6 закрыт. 1/ри положительном заряде конденсаторе 4 (1 по входу I) импульсный сигнал во вторичной обмотке (фиг.2 II проходит через вентиль 8 и нагрузку в виде резистора 11 . Импульс в нагру ке 1Г (вых.1) положителен. При отрицательном заряде на конденсаторе 4 (О по входу I) импульс во вторичной обмотке замыкается чере вентиль 9 и нагрузку в виде резистоpa 10. Импульс в нагрузке 10 (выход II) отрицателен. Амплитуда импульсного сигнала на выходаХТ и II логического устройства сравнения линейно зависит от величин заряда на конденсаторе 1 (вход I). При достижении величины заряда интегрирующего конденсатора I (i(t) и соответственно амплитуды импульса по счетному входу порогового значени срабатывает триггер 12, положительна входная характеристика которого выполняет функцию noporoBoio устройства. 8 При срабатывании триггера 12 инвертируются потенциалы выходов триггера: на прямом выходе устананлчвается низкий потенциал (О) , на инверсном - высокий (1). При этом ток стабилизатора 15 протекает через два других открытых диода модулятора 14 прямой выход триггера 12, его источник питания, инверсный выход триггера и интегрирующий конденсатор 1. Конденсатор 1 начинает разряжать ся, время разряда и. с tpoBP. При этом импульсы тактовой частоты f проходят на выход элемента И 17, на выходе элемента И 16 тактовых импульсов нет. Реверсивный счетчик 19 производит подсчет числа импульсов n,j(t) тактовой частоты f- по вычитающему входу в течение времени tpQ,(t) Конденсатор 4 интегрирующей цепи подзаряжается от конденсатора 1 через резистор 3 в течение T-j- и разряжается с тактовой частотой f-j- через ключ 6, который открывается по входу I I I в течение времени С, , и первичную обмотку 1. При этом ключ 5 закрыт . При положительном заряде на конденсаторе 4 1 по входу I отрицательные импульсы во вторичной обмотке замыкаются через вентиль 9 .и нагрузку 10. Сигнгш в нагрузке 10 (выход I Г) отрицателен. При отрицательном заряде на конденсаторе 4 О по входу 1 положительные импульсы во вторичной обмотке проходят через вентиль 8 и нагрузку 11. Импульс в нагрузке 11 (выход l) положителен. В этом случае инверсия импульсного сигнала на выходе Г осуществляется за счет противофазного подключения первичной обмотки импульсного трансформатора 7. В логическом устройстве сравнения опрос конденсатора 4 интегрирующей цепи производится непрерьшно независимо от состояний сигналов по входам. При этом постоянная составляющая напряжения на конденсаторе 4 интегрирумщей цепи равна нулю. Для уменьшения ощибки преобразования за счет утечки заряда с интегрирующего конденсатора 1 через резистор 3 во время опроса конденсатора 4 необходимо, чтобы нагрузки 11 и 10 вентилей 8 и 9 были равны. При этом утечки положительного и отрицательного зарядов с интегрирующего конденсатор 1 симметричны и взаимно компенсируются, т.к. нагрузки 1I и 10 будут симметрично шунтировать вторичную об мотку трансформатора 7. Симметрирование нагрузок 11 и 10 вентилей 8 и 9 повьппает стабильность коэффициента передачи преобразователя и уменьшает постоянную составляющую напряжения на интегрирующем конденсаторе 1. Перезаряд конденсатора А продолжа ется до тех пор, пока не будет достигнуто пороговое значение заряда пр тивоположного знака. В системе происходят автоколебания с частотой Fggi-(t) кратной тактовой fТавт ЬПериод автоколебаний равен: FoWt a-Uc-co T ,W.,a .. .ЭТD А Разность числа импульсов n(t)И n2(t) в течение TqefCt) определяется выражением 4U(tl-n,(t).T,( эт. т и характеризуется тем, что прямо про порциональна входному току Jg (t). Код на выходе реверсивного счетчика 19 N(t) за время счета tp пропорционален интегралу от входного .тока . . сц .. VCt).at . i Предложенный аналого-цифровой пре образователь измеряет входной ток лю бой полярности. Знак входного тока о ределяется соотношением числа импуль сов по суммирующему и вычитающему входам реверсивного счетчика 19. Погрешность коэффициента передачи преобразователя определяется только качеством стабилизации тока . и стабильностью тактовой частоты . Формула изобретения 1. Аналого-цифровой преобразовате содержащий формирователь биполярного А, 8 эталонного сигнала, вход которого подключен к прямому выходу триггера, а выход - к первому входу интегратора, первый и второй элементы И, пер-вые входы которых подключены соответственно к прямому и инверсному выходам триггера, вторые - к выходу тактового генератора, а выходы - соответственно к суммирующему и вйчитающему входам реверсивного счетчика, отличающийся тем, что, с целью повышения точности преобразования, в него введены трансформатор, два ключа, два вентиля и интегрирующая цепь, подключенная параллельно интегратору, причем первый вывод конденсатора интегрирующей цепи через первый и второй ключи подключен соответственно к крайним выводам первичной обмотки трансформатора, управляющие входы ключей соединены с выходами первого и второго элементов И соответственно, второй вывод конденсатора интегрирующей цепи подключен к средней точке первичной обмотки трансформатора, параллельно вторичной обмотке которого включен первый вентиль, первый вывод вторичной обмотки трансформатора через второй вентиль, включенный в противоположном йервому направлении, подключен к счетному входу триггера, инверсный выход которогоПодключен ко второму входу интегратора. 3. Преобразователь по и. I, о т л и ч ающийся тем,что формирователь биполярного эталонного сигнала вьшолнен в виде кольцевого диодного модулятора, первая диагональ которого подключена к стабилизатору тока, а вторая - к выходным шинам формирователя биполярного эталонного сигнала. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 567206, кл. Н 03 К 1.3/20, 30.07.77. 2.Балакай В.Г. и др. Интегральые схемы АЦП иЦАП.Энергия, 1978, . 72, рис. 1-23 (прототип) .

rflTK

//

XIM

vM

4

Ш

M

.

wVl/K

ll..l

Авторы

Даты

1981-06-07—Публикация

1979-07-17—Подача