Изобретение относится к импульс - ной технике и может, быть использовано в синтезаторах частот, в цифровых фазометрах, в измерительной аппаратуре и в цифровых системах автоподстройки частоты.

Цель изобретения расширение диапазона коэффициентов деления снизу (вплоть до 1) при наличии п младших управляемых каскадов и сохранении высокого быстродействия устройства и верхней границы диапазона- коэффициентов деления,

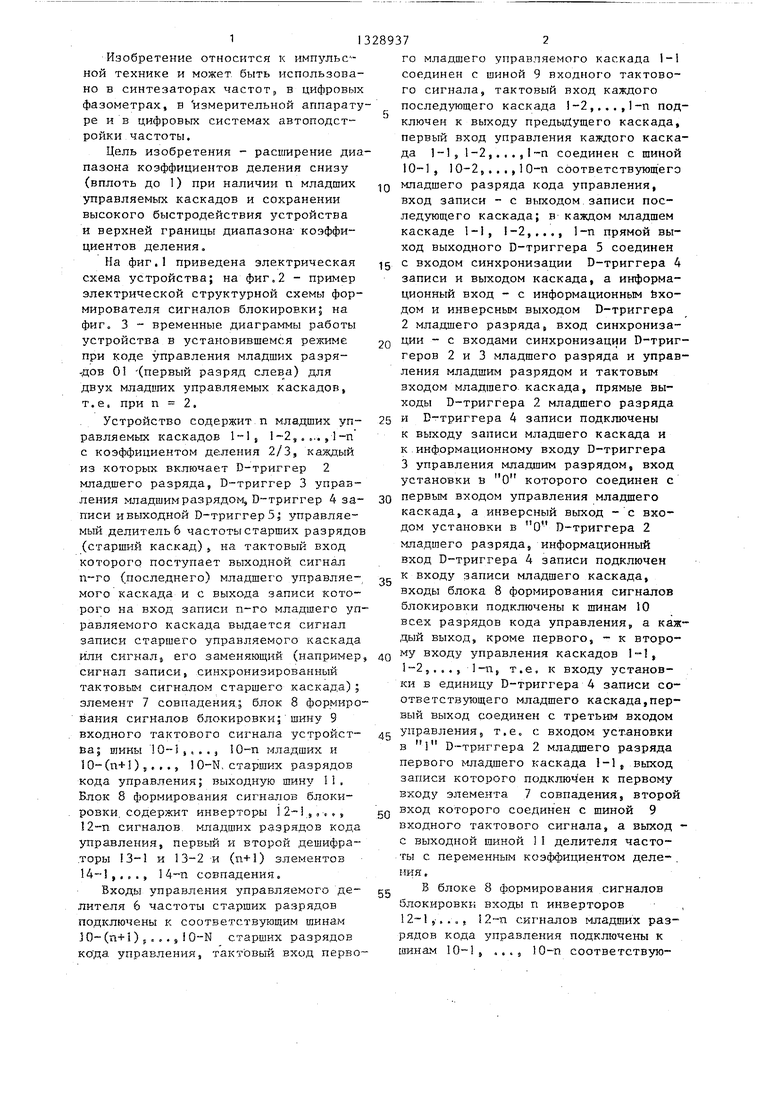

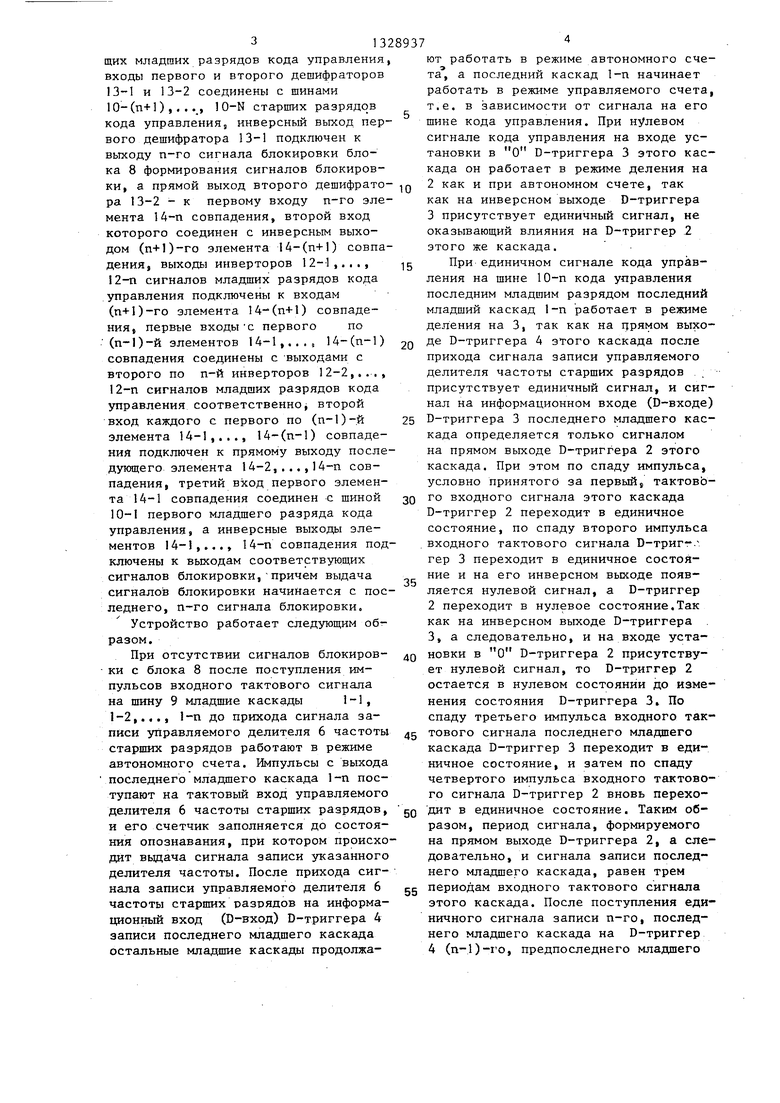

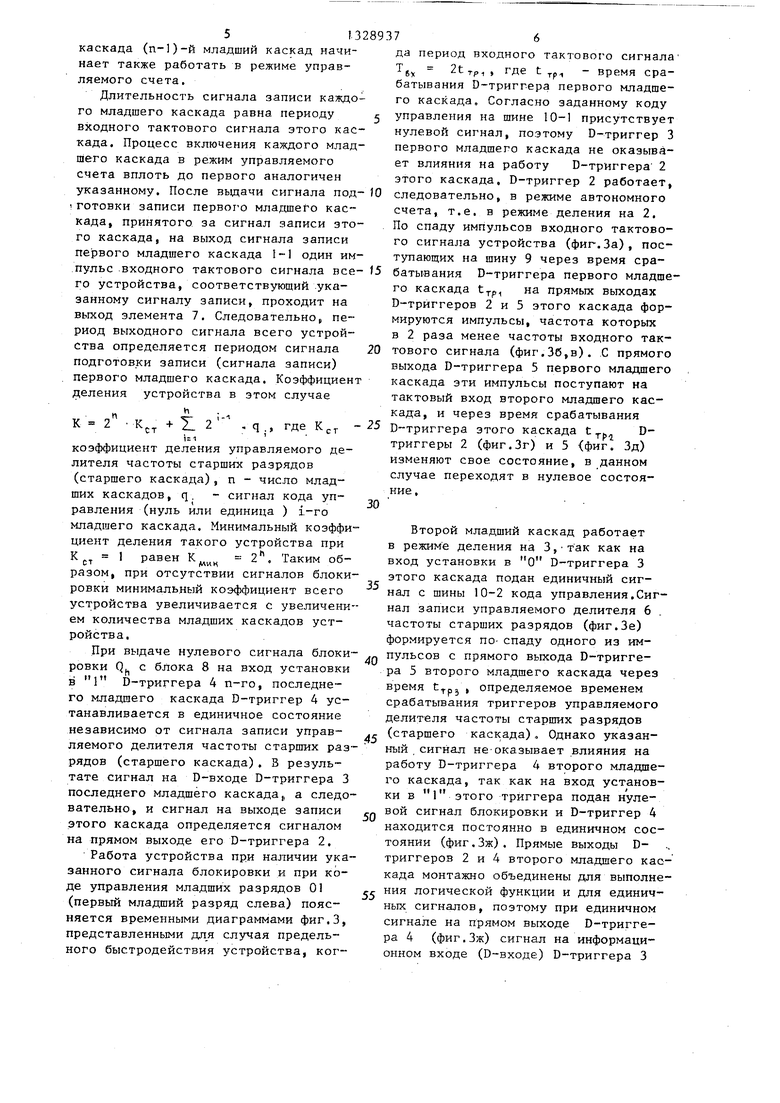

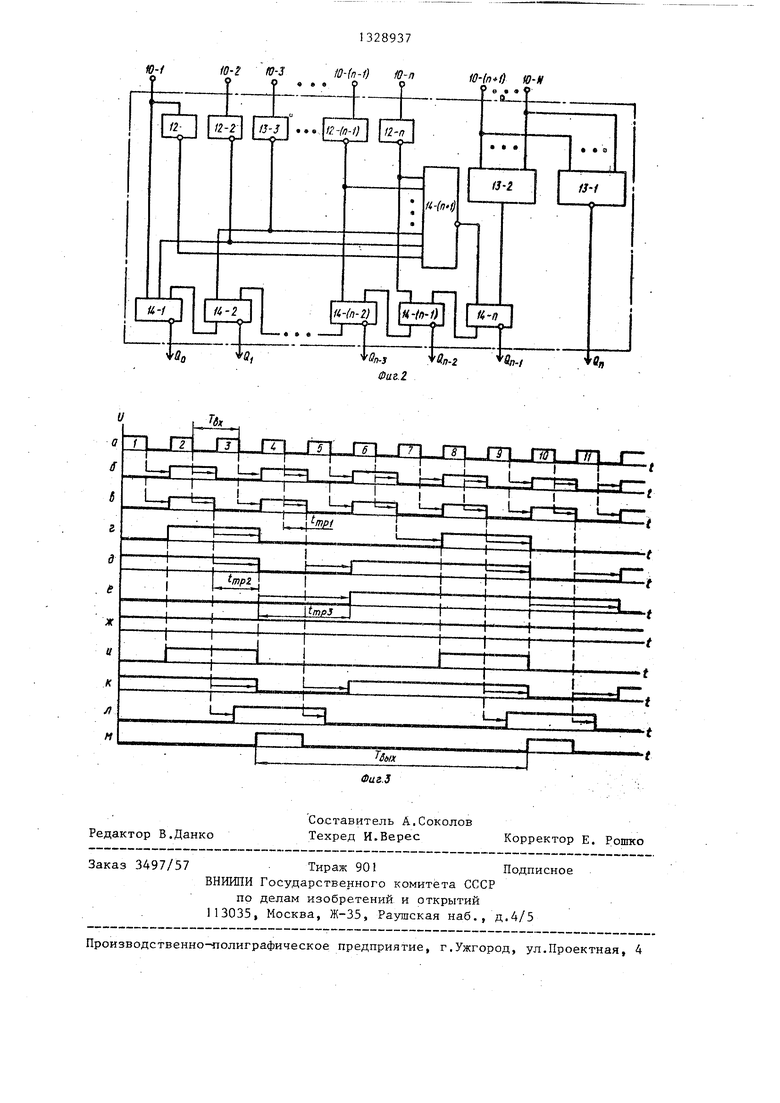

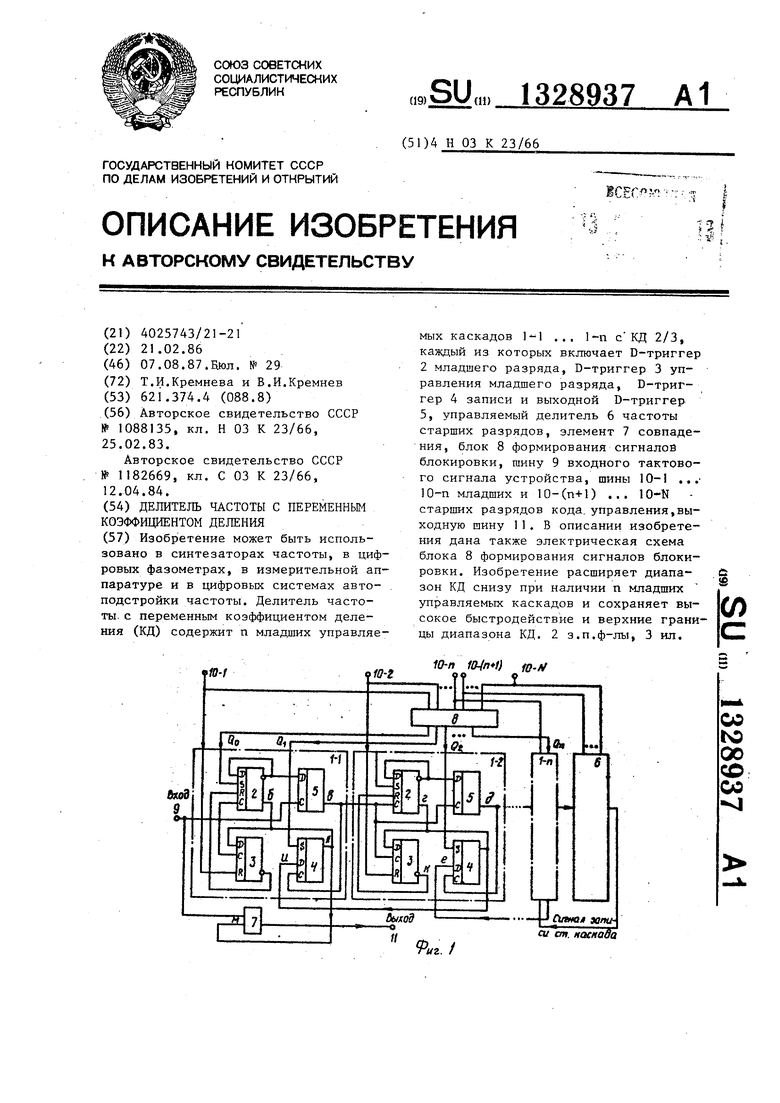

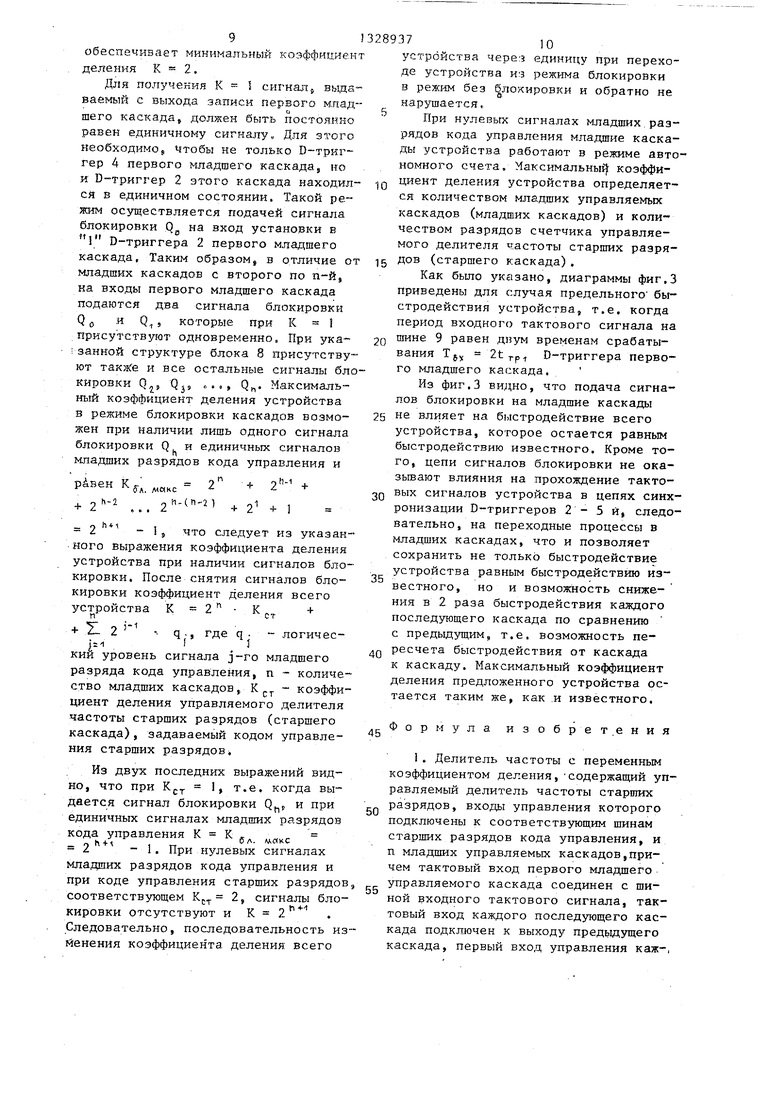

На фиг.1 приведена электрическая схема устройства; на фиг.2 - пример электрической структурной схемы формирователя сигналов блокировки; на фиг 3 - временные диаграммы работы устройства в установившемся режиме при коде управления младших разрядов 01 (первый разряд ) для двух младпшх управляемых каскадов, т.е. при п 2,

Устройство содержит п младших управляемых каскадов l-lj 1-2,.... ,1-п с коэффициентом деления 2/3, каждый из которых включает D-триггер 2 младшего разряда, D-триггер 3 управления младшим разрядом, D-триггер 4 записи и выходной D-триггер5; управляемый делитель 6 частоты старших разрядов (старший каскад) на тактовый вход которого поступает выходной сигнал п-го (последнего) младшего управляемого каскада и с выхода записи которого на вход записи п-го младшего управляемого каскада выдается сигнал записи старшего управляемого каскада или сигналS его заменяющий (например сигнал записи, синхронизированный тактовым сигналом старшего каскада); элемент 7 совпадения.; блок 8 формирования сигналов блокировки; шину 9 входного тактового сигнала устройства; шины lO-Jj,.., 0-п младших и 10-(п+1)S.,., 0-N,старших разрядов кода управления; выходную шину 11, Блок 8 формирования сигналов блокировки, содержит инверторы 12-19,., 2-п сигналов, младших разрядов кода управления, первый и второй дешифра- .торы 3-1 и 13-2 и (п+1) элементов 14-1,,.., 14-п совпадения.

Входы управления управляемого делителя 6 частоты старших разрядов подключены к соответствующим шинам J0-(n+i)5... старших разрядов ко да управления, тактовый вход первого младшего управляемого каскада 1-1 соединен с шиной 9 входного тактового сигнала, тактовый вход каждого последующего каскада -2,...,1-п под

ключен к выходу предыдущего каскада, первый вход управления каждого каскада -1, 1-2,.,.,1-п соединен с шиной 10-15 10-2,...,10-п соответствующего

младшего разряда кода управления, вход записи - с выходом записи последующего каскада; в каждом младшем каскаде 1-1, 1-2,..., 1-п прямой выход выходного D-триггера 5 соединен

с входом синхронизации D-триггера 4 записи и выходом каскада, а информационный вход - с информационным fexo- дом и инверсным выходом D-триггера

2младшего разряда, вход синхрониза- ции - с входами синхронизации D-триггеров 2 и 3 младшего разряда и управления младшим разрядом и тактовым входом младшего каскада, прямые выходы D-триггера 2 младшего разряда и D-триггера 4 записи подключены к выходу записи младшего каскада и к.информационному входу D-триггера

3управления младшим разрядом, вход установки в О которого соединен с

первым входом управления младшего каскада, а инверсный выход - с входом установки в О D-триггера 2 младшего разряда, информационный вход D-триггера 4 записи подключен

к входу записи младшего каскада, входы блока 8 формирования сигналов блокировки подключены к шинам 10 всех разрядов кода управления, а каждый выход, кроме первого, - к второму входу управления каскадов , ..., 1-п, т.е. к входу установки в единицу D-триггера 4 записи соответствующего младшего каскада,первый выход соединен с. третьим входом

управления, т.е. с входом установки в 1 D-триггера 2 младшего разряда первого младшего каскада 1-1, выход записи которого подключ ен к первому входу элемента 7 совпадения, второй

вход которого соединен с шиной 9

входного тактового сигнала, а выход - с выходной шиной 1i делителя частоты с переменным коэффициентом деле- . ния,

В блоке 8 ф.ормирования сигналов блокировки входы п инверторов 12-1,-..., 12-п сигналов г падших разрядов кода управления подключе1 ы к шинам 10--1 5 ...3 10-п соответствуюих младших разрядов кода управления, ходы первого и второго дешифраторов 13-1 и 13-2 соединены с шинами 10-(п+1) ,..., 10-N старших разрядов ода управления, инверсный выход первого дешифратора 13-1 подключен к ыходу п-го сигнала блокировки блоа 8 формирования сигналов блокировки, а прямой выход второго дешифрато- д ра 13-2 - к первому входу п-го элемента 14-п совпадения, второй вход которого соединен с инверсным выходом (п+1)-го элемента 14-(п+1) совпадения, выходы инверторов 12--1 ,. . . , 5 12-п сигналов младших разрядов кода управления подключены к входам (п+1)-го элемента 14-(п+1) совпадения, первые входы с первого по (п-1)-й элементов 14-1,.,., 14-(п-1) 20 совпадения соединены с -выходами с второго по п-й инверторов 12-2,..,, 12-п сигналов младших разрядов кода управления соответственноj второй вход каждого с первого по (п-1)-й 25 элемента 14-1 14-(п-1) совпадения подключен к прямому выходу последующего элемента 14-2,...,14-п совпадения, третий вход первого элемента 14-1 совпадения соединен с шиной зо 10-1 первого младшего разряда кода управления, а инверсные выходы элементов 14-1,.,., 14-п совпадения подключены к выходам соответствующих сигналов блокировки,-причем выдача сигналов блокировки начинается с последнего, п-го сигнала блокировки.

Устройство работает следующим образом.

При отсутствии сигналов блокиров- до ки с блока 8 после поступления импульсов входного тактового сигнала на шину 9 младшие каскады , 1-2,..., 1-п до прихода сигнала записи управляемого делителя 6 частоты 45 старших разрядов работают в режиме автономного счета. Импульсы с выхода последнего младшего каскада 1-п поступают на тактовый вход управляемого делителя 6 частоты старших разрядов, gQ и его счетчик заполняется до состояния опознавания, при котором происходит вьщача сигнала записи указанного делителя частоты. После прихода сигнала записи управляемого делителя 6 gg частоты старших разрядов на информационный вход (D-вход) D-триггера 4 записи последнего младшего каскада остальные младшие каскады продолжают работать в режиме автономного счета, а последний каскад 1-п начинает работать в режиме управляемого счета, т.е. в зависимости от сигнала на его шине кода управления. При нулевом сигнале кода управления на входе установки в О D-триггера 3 этого каскада он работает в режиме деления на

2как и при автономном счете, так как на инверсном выходе D-триггера

3присутствует единичный сигнал, не оказывающий влияния на D-триггер 2 этого же каскада.

При единичном сигнале кода управления на шине 10-п кода управления последним младшим разрядом последний младший каскад 1-п работает в режиме деления на 3, так как на прямом выходе D-триггера 4 этого каскада после прихода сигнала записи управляемого делителя частоты старших разрядов присутствует единичный сигнал, и сигнал на информационном входе (D-входе) D-триггера 3 последнего младшего каскада определяется только сигналом на прямом выходе D-триггера 2 этого каскада. При этом по спаду импульса, условно принятого за первый, тактового входного сигнала этого каскада D-триггер 2 переходит в единичное состояние, по спаду второго импульса входного тактового сигнала Б-триг-. гер 3 переходит в единичное состояние и на его инверсном выходе появляется нулевой сигнал, а D-триггер 2 переходит в нулевое состояние.Так как на инверсном выходе D-триггера . 3, а следовательно, и на входе установки в О D-триггера 2 присутствует нулевой сигнал, то D-триггер 2 остается в нулевом состоянии до изменения состояния D-триггера 3, По спаду третьего импульса входного тактового сигнала последнего младшего каскада D-триггер 3 переходит в единичное состояние, и затем по спаду четвертого импульса входного тактового сигнала D-триггер 2 вновь перехо- дит в единичное состояние. Таким образом, период сигнала, формируемого на прямом выходе D-триггера 2, а следовательно, и сигнала записи последнего младшего каскада, равен трем периодам входного тактового сигнала этого каскада. После поступления единичного сигнала записи п-го, последнего младшего каскада на D-триггер

4(n-l)-ro, предпоследнего младшего

каскада {п-1)-й младший каскад начинает также работать в режиме управляемого счета.

Длительность сигнала записи каждого младшего каскада равна периоду входного тактового сигнала этого каскада. Процесс включения каждого млад- Шето каскада в режим управляемого счета вплоть до первого аналогичен указанному. После выдачи сигнала под- готовки записи первого младшего каскада, принятого за сигнал записи этого каскада, на выход сигнала записи первого младшего каскада 1-1 один импульс .входного тактового сигнала всего устройства, соответствующий указанному сигналу записи, проходит на выход элемента 7. Следовательно период выходного сигнала всего устройства определяется периодом сигнала подготовки записи (сигнала записи) первого младшего каскада. Коэффициент деления устройства в зтом случае ti

К 2 К + Ц 2 . q ., где К,, -ь Ц 2

коэффициент деления управляемого делителя частоты старших разрядов (старшего каскада), п - число младших каскадов, q. - сигнал кода управления (нуль или единица ) i-ro младшего каскада. Минимальный коэффициент деления такого устройства при К 1 равен К 2. Таким образом, при отсутствии сигналов блокировки минимальный коэффициент всего устройства увеличивается с увеличением количества младших каскадов устройства.

При выдаче нулевого сигнала блокировки Q. с блока 8 на вход установки в 1 D-триггера 4 п-го, последнего младшего каскада D-триггер 4 устанавливается в единичное состояние независимо от сигнала записи управляемого делителя частоты старших разрядов (старшего каскада). В результате сигнал на D-входе D-триггера 3 последнего младшего каскада, а следовательно, и сигнал на выходе записи этого каскада определяется сигналом на прямом выходе его D-триггера 2.

Работа устройства при наличии указанного сигнала блокировки и при коде управления младших разрядов 01 (первый младший разряд слева) поясняется временными диаграммами фиг.З, представленными предельного быстродействия устройства, когда период входного тактового сигнала Tj 2trpi, где t р - время срабатывания О-триггера первого младшего каскада. Согласно заданному коду

управления на шине 10-1 присутствует нулевой сигнал, поэтому О-триггер 3 первого младшего каскада не оказывает влияния на работу D-триггера 2 этого каскада, D-триггер 2 работает,

следовательно, в режиме автономного счета, т.е. в режиме деления на 2. По спаду импульсов входного тактового сигнала устройства (фиг.За), поступающих на шину 9 через время срабатывания D-триггера первого младшего каскада на прямых выходах D-трйггеров 2 и 5 этого каскада формируются импульсы, частота которьпс в 2 раза менее частоты входного тактового сигнала (фиг,36,в). С прямого выхода О-триггера 5 первого младшего каскада эти импульсы поступают на тактовый вход второго младшего каскада, и через время срабатывания

D-триггера этого каскада t ,, D- триггеры 2 (фиг.Зг) и 5 (фиг. Зд) изменяют свое состояние, в данном случае переходят в нулевое состояние.

5

0

5

Второй младший каскад работает в режиме деления на 3,так как на вход установки в О D-триггера 3 этого каскада подан единичный сигнал с шины 10-2 кода управления,Сигнал записи управляемого делителя 6 частоты старших разрядов (фиг.Зе) формируется по- спаду одного из импульсов с прямого выхода D-триггера 5 второго младшего каскада через время , определяемое временем срабатывания триггеров управляемого делителя частоты старших разрядов (старшего каскада). Однако указанный сигнал не-оказывает влияния на работу D-триггера 4 второго младшего каскада, так как на вход установки в 1 этого триггера подан нуле50

55

вой сигнал блокировки и D-триггер 4 находится постоянно в единичном состоянии (фиг.Зж). Прямые выходы D- триггеров 2 и 4 второго младшего каскада монтажно объединены для выполнения логической функции и для единичных сигналов, поэтому при единичном сигнале на прямом выходе D-триггера 4 (фиг.Зж) сигнал на информационном входе (D-входе) D-триггера 3

(фиг.Зи) повторяет сигнал прямого выхода D-триггера 2 (фиг.Зг),

При единичном сигнале на D-входе D-триггера 3 (фиг.Зи) по спаду импульса на входе синхронизации этого триггера (фиг.Зв) D-триггер 3 переходит в единичное состояние, а на его инверсном выходе формируется нулевой сигнал Сфиг.Зк), который блокирует изменение состояния D-триггера 2 (фиг.Зг) по спаду очередного,второго импульса на его входе синхронизации (фиг.Зв). D-триггер 2 продолжает оставаться в нулевом состоянии (фиг. Зг), а D-триггер 3 по спаду второго тактового импульса второго младшего каскада (фиг.Зв,к) переходит в это состояние. Так как на инверсном выходе D-триггера 3 (фиг.Зк) вновь присутствует единичный сигнал, D- триггер 2 по спаду третьего тактового импульса (фиг.Зв) переходит в единичное состояние. Таким образом, на

П-1

прямом выходе D-триггера 2 (фиг.Зг), 25 (п-1)-й младший каскад с той лишь

а следовательно, на выходе записи второго младшего каскада (фиг.Зи) формируется сигнал, период которого равен трем периодам входного тактового сигнала этого каскада (фиг. Зв,и). Этот же сигнал поступает и на информационный вход (D-вход) D,-тpиг- гера 4 первого младшего каскада.

При единичном сигнале кода управления второго младшего каскада. D- триггер 4 первого младшего каскада работает аналогично D-триггеру 3 второго младшего каскада с той лишь разницей, что его время срабатывания

, а время срабатывания D-тригге- Q нии коэффициента деления всего уст- ра 3 рабно , (фиг.2в,к,л). Дли- ройства не учитываются. При этом ко

эффициент деления всего устройства

Тр2

тельность сигнала на прямом выходе D-триггера 4 равна периоду выходного сигнала первого младшего каскада (фиг. Зв,л). Прямые выходы D-тригге-. ров 2 и 4 монтажно объединены для выполнения логической функции и для единичных сигналов, поэтому на информационном входе D-триггера 3 и, следовательно, на выходе записи первого младшего каскада формируется сигнал . (фиг.3м), длигельность .которого равна периоду входного тактового сигнала устройства, а период повторения (фиг. За,м) составляет шесть периодов этого сигнала. На шине 10-1 согласно заданному коду управления присутствует нулевой сигнал, поэтому D-триггер 3 первого младшего каскада

К,

2 + 1 2

1-1

50

f-д. Z 1- Z qj, где 1 - номер

I J l

ДЕ младшего каскада, начиная с которого поданы сигналы блокировки, q. - логический уровень (нуль или единица) сигйсша j-ro разряда кода управления младших разрядов.

На фиг.З представлен случай, когда сигнал блокировки подан на второй младший каскад, т.е. i 2. Код управления младших разрядов 01 (первый младший разряд слева), поэтому коg эффициент деления всего устройства при этом Kj 2 + - 1 + (фиг.За,м). При подаче сигналов блокировки Q,,...Qp, т.е.

при

и при q 0 устройство

5

0

не оказывает влияния на работу D- триггера 2 этого каскада и D-триггер 2 работает в режиме автономного счета, а первый младший каскад - в режиме деления на 2. Коэффициент деления всего устройства в данном случае К 6, так как на выходе элемента 7 вьщается сигнал, частота которого равна частоте сигнала на выходе записи первого младшего каскада (фиг.3м), а длительность - длительности импульса входного тактового сигнала устройства (на фиг. За импульсы 4 и 10).

Таким образом, при наличии сигнала блокировки на п-м, в данном случае втором, младшем каскаде делитель частоты с переменным коэффициентом деления работает независимо от сигнала записи yпpaвJfяeмoгo делителя частоты старших разрядов (старшего каскада).

Аналогично работает устройство при

подаче сигнала блокировки Q

П-1

на

(п-1)-й младший каскад с той лишь

разницей, что в этом случае не оказывают влияния на работу предьщущих (п-)-х младших каскадов устройства как сигнал с выхода записи старшего 0 каскада, так и сигнал с выхода записи п-го младшего каскада. Как было указано, выдача сигнала блокировки на i-й младший каскад производится при наличии сигналов блокировки на входах всех последующих, начиная с (1+1)-го по п-й, младших каскадах, поэтому при поступлении сигнала блокировки на i-й младший каскад младшие каскады (i+l)...n при определеК,

2 + 1 2

1-1

0

f-д. Z 1- Z qj, где 1 - номер

I J l

Е младшего каскада, начиная с которого поданы сигналы блокировки, q. - логический уровень (нуль или единица) сигйсша j-ro разряда кода управления младших разрядов.

На фиг.З представлен случай, когда сигнал блокировки подан на второй младший каскад, т.е. i 2. Код управления младших разрядов 01 (первый младший разряд слева), поэтому ко эффициент деления всего устройства при этом Kj 2 + - 1 + (фиг.За,м). При подаче сигналов блокировки Q,,...Qp, т.е.

при

и при q 0 устройство

обеспечивает минимальный коэффициен деления К 2.

Для получения К 1 сигналj вьщаваемый с выхода записи первого младti

шего каскадаt должен быть постоянно

равен единичному сигналу. Для si oro необходимоS чтобь не только D-триг- гер 4 первого младшего каскада, но и D-триггер 2 этого каскада находил- ей в единичном состоянии. Такой режим осуществляется подачей сигнала блокировки Qg на вкод установки в D-триггера 2 первого младшего каскада, Таким образом, в отличие от младших каскадов с второго по п-й, на входы первого младшего каскада подаются два сигнала блокировки Q д и Q, которые при К 1 присутствуют одновременно. При ука ;занной структуре блока 8 присутствуют и все остальные сигналы блокировки Q,, QJ, «.., Q. Максимальный коэффициент деления устройства в режиме блокировки каскадов возмо- жен при Наличии лишь одного сигнала блокировки Q1 и единичных сигналов младших разрядов кода управления и

+

рАвен К у ,„,, 2

+ 2

11-2

п-(П 2)

2 + 1

h + 1

2 S ЧТО следует из указан- ного выражения коэффициента деления устройства при наличии сигналов блокировки. После снятия сигналов блокировки коэффициент деления всего

устройства п

)-ч

к 2

К

с т

где

логичес Z 2

кии уровень сигнала j-ro младшего разряда кода управления, п - количество младших каскадов, К, - коэффициент деления управляемого делителя частоты старших разрядов (старшего каскада), задаваемый кодом управления старших разрядов .

Из двух последних выражений видно, что при К I, т.е. когда выдается сигнал блокировки и при единичных сигналах младших разрядов К К

кода управления 2 - 1, При

длякс сигналах

ел. нулевых

младших разрядов кода управления и при коде управления старших разрядо соответствующем К 2, сигналы блокировки отсутствуют и К 2 Следовательно, последовательность и йенения коэффициента деления всего

устройства чере:з единицу при переходе устройства из режима блокировки в режим без локировки и обратно не нарушается.

При нулевых сигналах младших.разрядов кода управления младшие каскады устройства работают в режиме автономного счета. Максимальны коэффициент деления устройства определяет- ся количеством младших управляемых каскадов (младших каскадов) и количеством разрядов счетчика управляемого делителя частоты старших разрядов (старшего каскада).

Как было указано, диаграммы фиг.З приведены для случая предельного быстродействия устройства, т.е. когда период входного тактового сигнала на шине 9 равен д)ум временам срабаты

вания Т

б(

2t

тр, D-триггера первого младшего каскада,

Из фиг.З видно, что подача сигналов блокировки на младшие каскады не влияет на быстродействие всего устройства, которое остается равным быстродействию известного. Кроме того, цепи сигналов блокировки не ока- зьшают влияния на прохождение тактовых сигналов устройства в цепях синхронизации D-триггеров 2 - 5 И, следовательно, на переходные процессы в младших каскадах, что и позволяет сохранить не только быстродействие устройства равным быстродействию известного, но и возможность снижения в 2 раза быстродействия каждого последующего каскада по сравнению с предьщущим, т.е. возможность пересчета быстродействия от каскада к каскаду. Максимальный коэффициент деления предложенного устройства остается таким же, как .и известного,

Формула изобрет.ения

1, Делитель частоты с переменным коэффициентом деления, содержащий управляемый делитель частоты старших разрядов, входы управления которого подключены к соответствующим шинам старших разрядов кода управления, и п младших управляемых каскадов,причем тактовый вход первого младшего управляемого каскада соединен с шиной входного тактового сигнала, тактовый вход каждого последующего каскада подключен к выходу предьщущего каскада, первый вход управления каж-,

дого младшего управляемого каскада соединен с шиной соответствующего младшего разряда кода управления, вход записи - с выходом записи последующего младшего управляемого каскада, о т л и ч а. ю щ и и с я тем, что, с целью расширения диапазона коэффициентов деления снизу при наличии п младших управляемых каскадов и сохранении высокого быстродействия и верхней границы диапазона коэффициентов деления, в него введены элемент совпадения и блок формирования сигналов блокировки, входы которого подключены к шинам всех разрядов кода управления, а каждый выход, кроме первого, подключен к второму входу управления соответствующего младшего управляемого каскада, первый выход соединен с третьим входом управления первого младшего управляемого каскада, выход записи которого подключен к первому входу элемента совпадения, второй вход которого соединен с шиной входного тактового сигнала, а выход - с выходной шиной.

2. Делитель поп.1, отличающийся тем, что блок формирования сигналов блокировки содержит п инверторов, сигналов младших разрядов кода управления, входы которых подключены к шинам соответствующих младших разрядов кода управления, (п+1) элементов совпадения и двзгх дешифраторов, входы каждого из которых соединены с шинами старших разрядов кода управления, инверсный выход первого дешифратора подключен к выходу п-го сигнала блокировки блока формирования сигналов блокировки, а выход второго дешифратора - к первому входу п-го элемента совпадения, второй вход которого соединен с инверсным выходом (п+1)-го элемента совпадения, выходы инверторов сигналов младших разрядов кода управления подключены к входам (п+1)-го элемента совпадения, первые входы с первого по (п-1)-й элементов совпадения соединены с выходами с второго по п-й инверторов сигналов младших разрядов кода управления соответственно, второй вход каждого с первого по (п-1)-й элемента совпадения подключен к прямому выходу последующего элемента совпадения, третий вход первого элемента совпадения соединен с

шиной первого младшего разряда кода управления, а инверсные выходы п элементов совпадения подключены к выходам соответствующих сигналов блокировки блока формирования сигналов

блокировки.

3. Делитель п.1, отличающий с я тем, что младший управляемый каскад содержит D-триггер младшего разряда, )-триггер управления младшим разрядом, D-триггер записи и выходной D-триггер, прямой выход которого соединен с входом синхронизации D-триггера записи и выходом младшего управляемого каскада, информационный вход - с информационным

входом и инверсным выходом D-триггера младшего разряда, вход синхрониза- ции - с входами синхронизации D- триггеров младшего разряда и управления младшим разрядом и с тактовым входом младшего управляемого каскада, прямые выходы D-триггеров младшего разряда и записи подключены к выходу записи младшего управляемого

каскада и к информационному входу D-триггера управления младшим разрядом, вход установки в О которого соединен с первым входом управления младшего управляемого каскада, инверсный выход - с входом установки в О В-триггера младшего разряда, информационный вход D-триггера записи соединен с входом записи младшего управляемого каскада, второй и

третий входы управления которого соединены с входами установки в l соответственно D-триггера записи и D-триггера младшего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

| Делитель частоты с переменным коэффициентом деления | 1984 |

|

SU1182669A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Делитель частоты с переменным коэффициентом деления | 1987 |

|

SU1444939A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1396277A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

Изобретение может быть использовано в синтезаторах частоты, в цифровых фазометрах, в измерительной аппаратуре и в цифровых системах автоподстройки частоты. Делитель частоты, с переменным коэффициентом деления (КД) содержит п младших управляемых каскадов ... 1-п с КД 2/3, каждый из которых включает D-триггер 2 младшего разряда, D-триггер 3 управления младшего разряда, D-триггер 4 записи и выходной D-триггер 5, управляемый делитель 6 частоты старших разрядов, элемент 7 совпадения, блок 8 формирования сигналов блокировки, шину 9 входного тактового сигнала устройства, шины 10-1 .. . 10-п младших и lO-(n-i-l) ... 10-N старших разрядов кода, управления,выходную шину 11. В описании изобретения дана также электрическая схема блока 8 формирования сигналов блокировки. Изобретение расширяет диапазон КД снизу при наличии п младших управляемых каскадов и сохраняет высокое быстродействие и верхние границы диапазона КД. 2 з.п.ф-лы, 3 ил. (Л 10-п fO-ff Б оо to 00 х оо . / си ст. носнааа

| Управляемый делитель частоты импульсов | 1983 |

|

SU1088135A1 |

| Делитель частоты с переменным коэффициентом деления | 1984 |

|

SU1182669A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-07—Публикация

1986-02-21—Подача