(54) ТРАНСФОРМАТОРНОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Трансформаторное постоянное запоминающее устройство | 1974 |

|

SU502396A1 |

| Постоянное запоминающее устройство | 1972 |

|

SU466551A1 |

| СПОСОБ ВЫБОРКИ ИНФОРМАЦИИ | 1969 |

|

SU253142A1 |

| ДОЛГОВРЕМЕННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ТРАНСФОРМАТОРНОГО ТИПА С ЗАПИСЬЮ ЧИСЕЛ В СИСТЕМЕ СЧИСЛЕНИЯ С ОСНОВАНИЕМ Р, БОЛЬШИМ ДВУХ | 1973 |

|

SU393771A1 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1310901A2 |

| ПОСТОЯННОЕ З.ЛПОМИНЛЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU346752A1 |

| НАКОПИТЕЛЬ ПОСТОЯННОГО ЗАПОМИН.ЛЮЩЕГО УСТРОЙСТВА | 1973 |

|

SU409295A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU750562A1 |

| Постоянное запоминающее устройство трансформаторного типа | 1972 |

|

SU576610A1 |

| Трансформаторное постоянное запоминающее устройство | 1974 |

|

SU577566A1 |

1

Изобретение относится к автоматике и вычислительной технике, а именно к постоянным запоминаюп.1им устройствам трансформаторного типа (ПЗУ).

Известно трансформаторное ПЗУ, содержащее числовые линейки из трансформаторов на ферромагнитных сердечниках, прошитых общими информационными проводами, подключенными к дешифраторам считывания, блок запрета, вход которого подключен к одному из дещифраторов считывания. Выходы блока запрета соединены с проводами запрета соответствующих числовых линеек 1.

Однако при некоторых кодах записанной информации изменяется амплитуда тока опроса в информационных проводах. Это приводит к нарушению равенства амплитуды тока опроса и тока запрета, что вызывает появление разностного тока в первичной цепи трансформаторов числовых линеек. Разностный ток вызывает появление помех на выходных обмотках трансформаторов невыбранных числовых линеек, что ухудшает надежность устройства.

Наиболее близким по технической сущности к предлагаемому является трансформаторное постоянное запоминающее устройство, содержащее объединенные числовые линейки, запоминающие трансформаторы которых прошиты кодовыми проводами и проводами противотока, дополнительный трансформатор, одна обмотка которого включена последовательно с кодовыми проводами другая - с проводами противотока 2.

Недостатком такого устройства является то, что при неизменной амплитуде тока опроса амплитуда сигналов и помех на выходных обмотках запоминающих трансформаторов выбранных числовых линеек зависит от расположения опрашиваемых кодовых проводов относительно выходных обмоток запоминающих трансформаторов. Это определяет низкое соотнощение сигнал/помеха на выходе накопителя и, таким образом, низкую надежность работы устройства.

Цель изобретения - повышение надежности устройства.

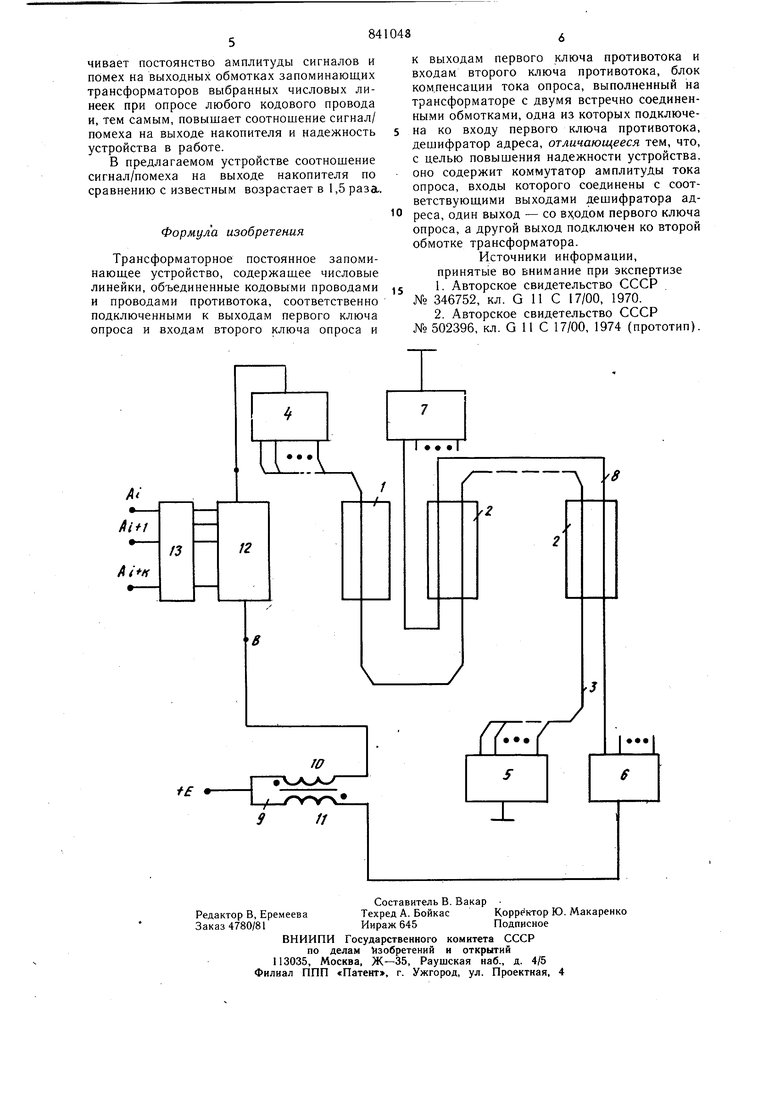

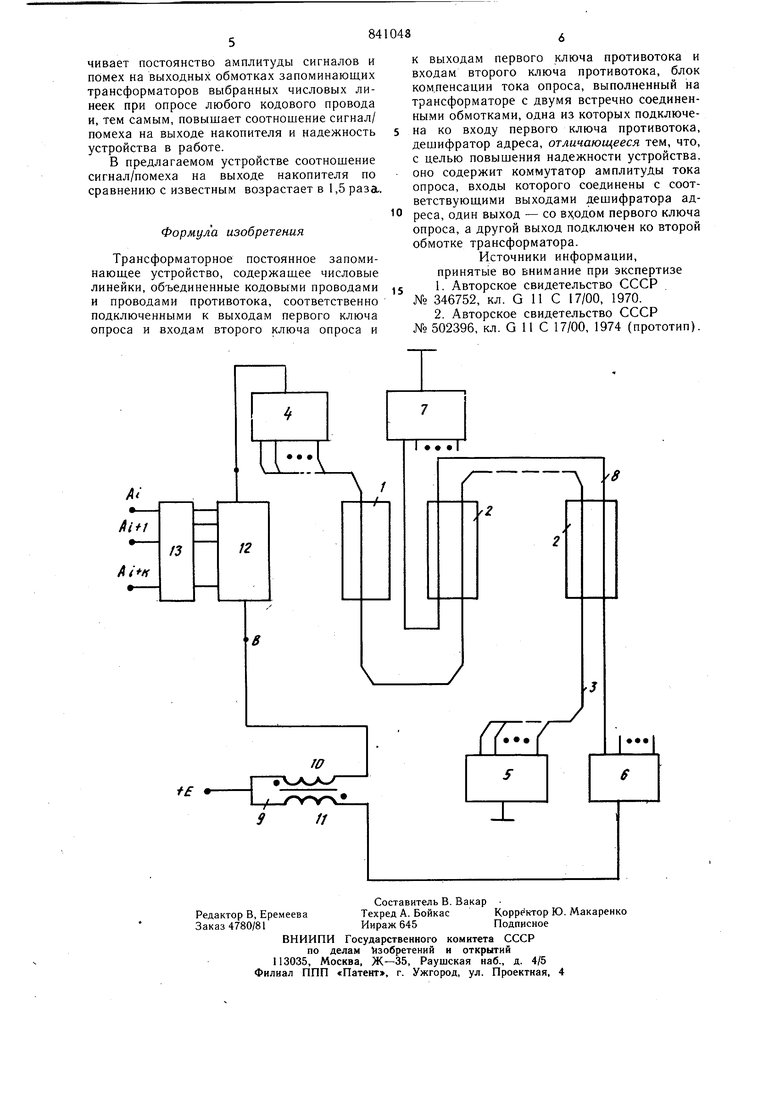

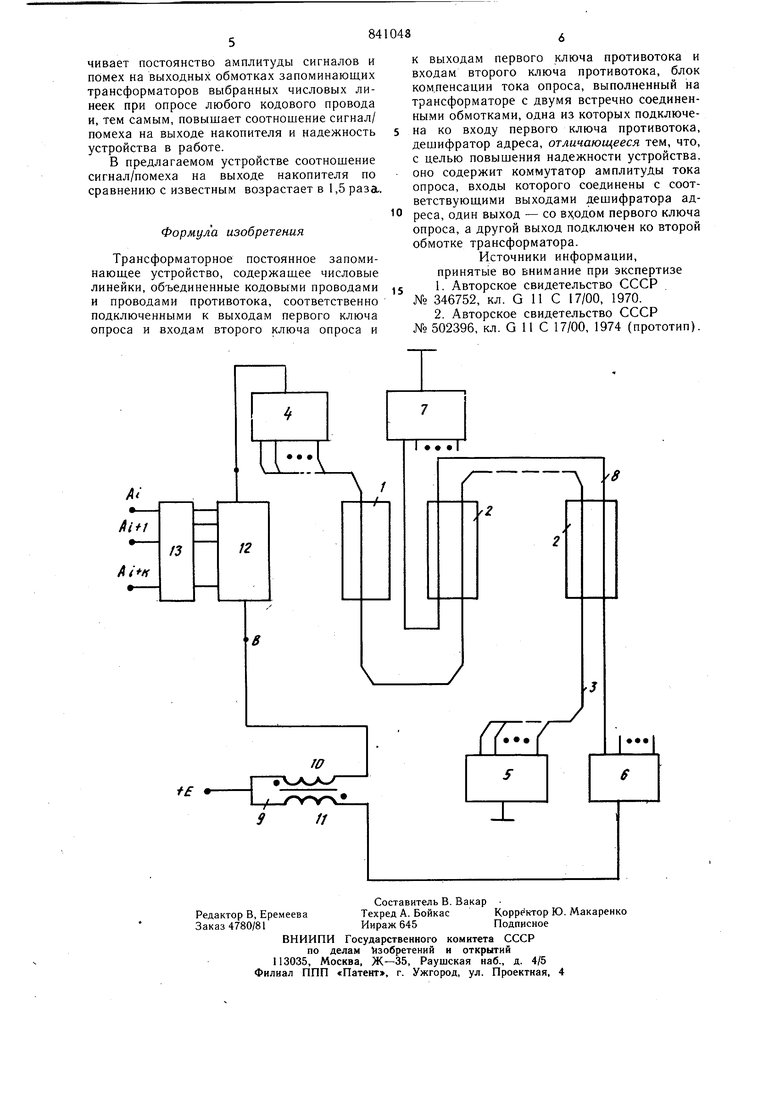

Поставленная цель достигается тем, что в устройство, содержащее числовые линейки, объединенные кодовыми проводами и проводами противотока, соответственно подключенными к выходам первого ключа опроса и входам второго ключа опроса и к вьГходам первого ключа противотока и входам второго ключа противотока, блок компенсации тока опроса, выполненный на трансформаторе с двумя встречно соединенными обмотками, одна из которых подключена ко входу первого ключа противотока, дешифратор адреса, введен коммутатор амплитуды тока опроса, входы которого соединены с соответствующими выходами дешифратора адреса, один выход - со входом первого ключа опроса, а другой выход подключен ко второй-обмотке трансформатора. Включение последовательно с кодовыми проводами коммутатора амплитуды тока опроса, управляемого дешифратором адреса по признаку принадлежности опрашиваемого кодового провода одной из групп кодовых проводов (одному из кодовых жгутов), последовательность укладки которых пр.и изготовлении ПЗУ, а следовательно, и расположение их относительно выходных обмоток запоминающих трансформаторов определяется принятой последовательностью адресации, позволяет изменять амплитуду тока опроса в функции кодовой комбинации адреса, а следовательно, и в функции расположения кодовых проводов относительно выходных обмоток запоминающих трансформаторов, что обеспечивает постоянство амплитуды сигналов и помех на выходах запоминающих трансформаторов выбранных числовых линеек при опросе любого кодового провода. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит числовые линейки 1 и 2, состоящие из запоминающих трансформаторов, выполненных на разъемных ферритовых сердечниках, прошитые кодовыми проводами 3, первый и второй ключи 4 и 5 опроса, первый и второй ключи 6 и 7 противотока, провода 8 противотока, трансформатор 9, одна обмотка 10 которого включена последовательно с кодовыми проводами 3, а другая обмотка 11 - последовательно с проводами 8 противотока. Число проводов 8 противотока равно количеству числовых линеек 1 и 2. Обмотки 10 и 11 трансформатора 9 имеют одинаковое количество витков и включены между источником питания + Е и первым ключом 4 опроса и первым ключом 6 противотока, коммутатор 12 амплитуды тока опроса, дешифратор 13 адреса. . В качестве коммутатора амплитуды тока опроса может быть использована транзисторная матрица с различной резистивной нагрузкой в цепи коллектора каждого транзистора. Эмиттеры транзисторов матрицы объединяются и подключаются к точке Б, резисторы нагрузки объединяются общей щиной, которая подключается к точке В. Базы транзисторов подключаются к выходам дешифратора 13 адреса. Таким образом, ЧИСЛО транзисторов в матрице определяется числом выходов дещифратора 13 адреса, которое определяется из выражения N 2 где i, k-индексы, соответствующие номерам разрядов кодовых шин адреса А, к которым подключаются входы дешифратора 13 адреса. Устройство работает следующим образом, В соответствии с пришедшим кодом адреса открываются ключи 4 и 5 опроса и ключи 6 и 7 противотока. Одновременно с этим дешифратор 13 адреса осушествляет запуск коммутатора. 12 амплитуды тока опроса, задающего амплитуду тока опроса в функции приходящего на кодовые шины Ai, ... A,it кода адреса. Сформированные ток опроса и противоток протекают по опрашиваемому кодовому проводу 3 и проводу .8 противотока. В невыбранных числовых линейках 2 действие.тока опроса компенсируется противотоком и информация считывается только из выбранной числовой линейки 1. Компенсация тока опроса противотоком в невыбранных числовых линейках 2 осуществляется трансформатором 9, который производит перекачку энергии из одной цепи в другую, поддерживая равенство тока опроса и противотока по амплитуде и совпадение их во времени. При выборе ключами 4 и 5 опроса различных кодовых проводов 3, коммутатор 12 амплитуды тока опроса изменяет амплитуду тока опроса, пропорционально расстоянию от опрашиваемого кодового провода 3 до выходных обмоток запоминающих трансформаторов числовых линеек 1 и 2. Чем больше расстояние от опрашиваемого кодового провода до выходных обмоток запоминающих трансформаторов, тем больше амплитуда тока опроса, формируемого коммутатором 12 амплитуды тока опроса. Управление коммутатором 12 амплитуды тока опроса осуществляется дешифратором 13 адреса в соответствии с кодовой комбинацией на кодовых шинах адреса Ai ... Ai. Последовательность укладки кодовых проводов при изготовлении устройства, а следовательно, и расстояние их до выходных обмоток запоминающих трансформаторов, определяется принятой последовательностью адресации, т. е. порядком изменения кодовых комбинаций на кодовых щинах адреса Ai ... А|,л. Таким образом, введение в устройство коммутатора амплитуды тока опроса и соответствующих новых связей приводит к тому, что изменение амплитуды сигналов и помех на выходах запоминающих трансформаторов выбранных числовых линеек 1 в функции расположения опрашиваемых кодовых проводов относительно выходных обмоток запоминающих трансформаторов компенсируется изменением амплитуды тока опроса в опрашиваемых кодовых проводах, что обеспе

Авторы

Даты

1981-06-23—Публикация

1979-10-12—Подача