1

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах для хранения таблиц, программ, микрокоманд программного управления и т. д.

Известно постоянное запоминающее устройство трансформаторного типа, содерлсащее дешифраторы, выходы одного из которых подключены пеиосредственно, и другого - через разделительные элементы к соответствующим входам наконителя, а выходы накопнтеля подключены к соответствующим входам выходного регистра.

Цель изобретения - повыщение быстродействия устройства, надежности его работы и его информационной CMKOCTII. В описываемом устройстве это достигается тем, что в нем между соответствующими входами дешифраторов включен блок формирования тока опроса, между одним из выходов иакопнтеля и щинами питания включен блок формирования логической единицы и между выходами второго деншфратора и иакопителя включены дополнительные раздел тельные элементы.

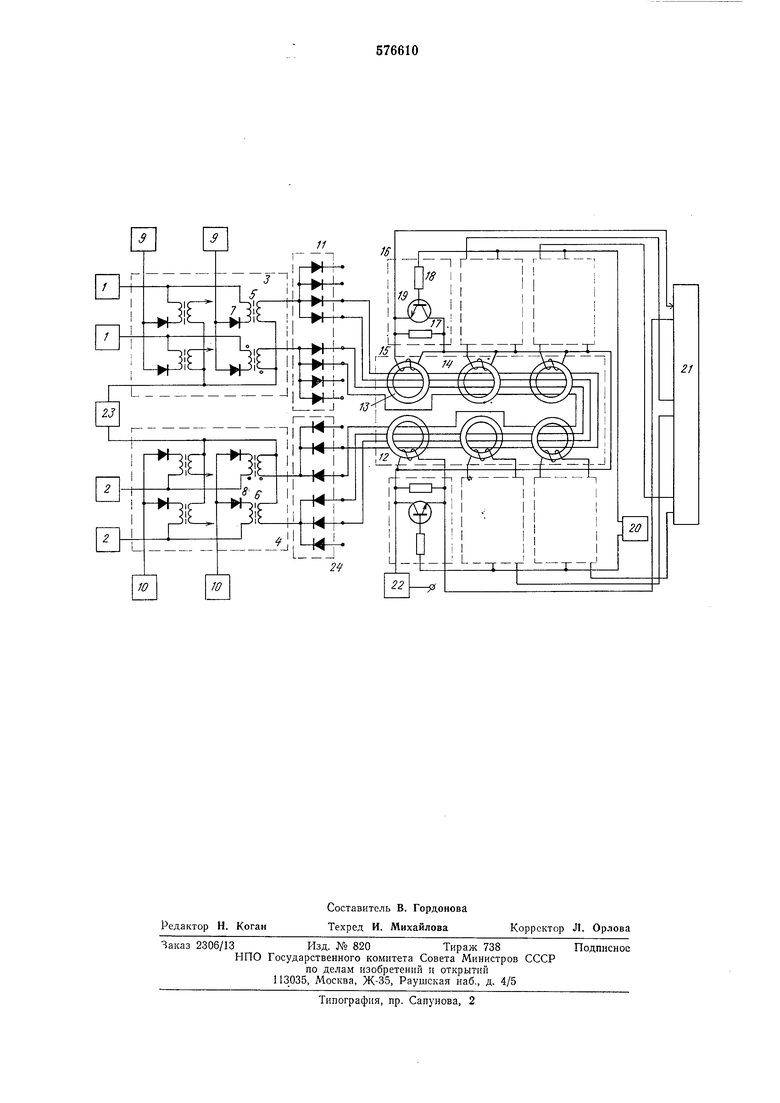

Иа чертеже ноказана функциональная схема онисываемого устройства для случая 32 трехразрядных слоев.

Оно состоит из формирователей тока 1, 2, служаииьх для формирования импульсов тока; двух дешифраторов 3, 4, состояищх из координатных трансформаторов 5, 6 и диодов 7, 8 соответственно, предназначенных для коммутации тока опроса в выбранном числовом проподе; приемников тока 9, 10 для коммзтации

импульсов тока в первичных обмотках координатных трансформаторов 5, 6; блока разделительных элементов 11 для обеспечения протекапия тока опроса только в выбранном числовом проводе; накопителя 12, состоящего из

ферритовых сердечников с непрямоугольной петлей гистерезпса 13, прошитых числовыми проводами 14, и обмоток считывания 15, иредназиаченного для хранения записанной информации; блоков з правления 16, состоящих

из резисторов 17, 18 и транзистора 19, обеспечивающих считывание только одного из слоев, хранящихся на числовом нроводе 14, путем И1унтировання остальных невыбранных обмоток считывания 15; блока ключей 20, служаи;,его для коммутации сигналов выборки слова на входы блоков управления 16; блока выходного регистра 21, служащего для объединения .одноименных разрядов всех слоев, хранящихся на числовом нроводе 14, и формирования считанного кода; блока формирования «логической единнцы 22, служащего для формировання уровня логической единицы и иозволяющего в блоках 20 и 21 использовать стандартные логическне элементы; блока формпровання тока опроса 23, служащего для

формирования двухступенчатых импульсов тока опроса, а также для вырабатывания папряжения смещения; блока дополнительных разделительных элементов 24, предназначеппого для уменьшеипя емкостных помех.

В исходном состоянии диоды блока разделительных эле1ментов И и блока дополнительных разделительных элементов 24 cMeHJ,eны в обратном направлении напряжением смещения, которое вырабатывается блоком 23, включенным в цепь, соединяющую общий вывод вторичных обмоток координатных трансформаторов 5 с общим выводом вторичных обмоток координатных трансформаторов 6. Выбранный формирователь тока 1 формирует импульсы тока, которые нротекают через первичную обмотку коордппатного трансформатора 5, диод 7 деп1ифратора 3 и выбранный приемник тока 9. Вторичная обмотка координатного трансформатора 5 включена так, что выбранный координатный трансформатор 5 формирует иоложительный импульс напряжения. Одновременно выбираются формнрователь тока 2 и нриемник тока 9, которые формируют импульсы тока в первичной обмотке координатного трансформатора 6 дешифратора 4. Вторичные обмотки координатных трансформаторов 6 включены так, что выбранный коордннатный трансформатор 6 формирует отрипательный импульс иапрял ения. В результате к концам выбранного числового провода 14 по отнон1ению к земляному уровню прикладываются импульсы напряжения, равные по амплитуде, но противоположной иоляриости. Сумма этих напряжений обеспечивает в выбранном числовом проводе 14 ток опроса. В остальных (невыбранных) чпсловых проводах 14 протекает незначительный ток помехи, так как к иим ирикладывается имиульс наиряжения только одного из выбрапиых координатных трапсформаторов 5 (или 6), иедостаточный для преодоления напряжения смеИ1еиия, вырабатываемого блоком 23.

Дальпейптее умеиыпение емкостных помех может быть достигнуто путем иодключепия числовых проводов к выходам дещпфратора 4 через блок дополнительных разделительных элементов 24.

Так как диоды блока разделительных элементов 11 и блока дополнительиых разделительных элементов 24 имеют конечное |зремя включения, то в начальный момент времени ток оироса распределяется между выбранными и иевыбрапными числовыми ироводамп 14. В этот момент происходит заряд межпроводиых паразитных емкостей, но величииа тока ограничивается блоком формирования тока опроса 23. Поэтому на вторичных обмотках

трансформаторов числовой матрицы наводятся только пезначнтельпые с гиалы помехи. После того, как заряд паразитных емкостей закапчивается, ток опроса в выбраином числовом ироводе 14 достигает максимального значения.

Таким образом, но выбранному числовому нроводу протекает двухступенчатый ток опроса, который нозволяет производнть заряд

паразитиых емкостей током по амплитуде в два раза меньщим рабочего, вследствие чего увеличивается отиошеиие полезиого сигнала к помехе, а также получат времепное разделение помехи и сигнала.

Ток опроса, протекая по выбранному числовому нроводу 14, индуктирует сигиалы «нуля пли «едииицы па обмотках считывания 15 в соответствии с кодировкой. Разрешеиие на считывание информации одного из слов, хранящихся на выбранном числовом ироводе 14, иостуиает из блока ключей 20. Выходные сигиалы с обмотки считывания 15 иоступают иа входы блоков выходного регистра 21. Па соответствующие входы блока 21 с блока формирования «логической едииицы 22 через обмотки считывания 15 постояино иостуиает потенинал, соответствующий уровню «логической единицы, а на выходах блока выходного региетра 21 вырабатывается уровень «логического нуля.

Обмотки считываиия 15 включены так, что считанное слово ностунает на соответствуюHuie входы блока выходного регистра 21 в обратном коде.

Следовательно, при считывании из описываемого устройства любого слова оно формируется в прямо.м коде на выходах блока 21.

Формула изобретения

Постоянное заномииающее устройство трансформаторного типа, содержащее дещифраторы, выходы одного из которых подключены неиосредственно, а другого - через разделительные элементы к соответствуюпиш входам иакоиителя, а выходы иакоиителя подключены к соответствующим входам выходного регистра, отличающееся тем, что, с целью повышепия быстродействия устройства, надежности его работы и его информационной емкости, оно содержит блок формирования тока опроса, включенный между соответствующими входами дешифраторов, блок формирования логической едииицы, включенный между одним из выходов накопителя и щинами питаиия, и дополнительные разделительные элементы, включенные между выходами второго дешифратора и иакоиителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСТОЯННОЕ З.ЛПОМИНЛЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU346752A1 |

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1310901A2 |

| Устройство для обращения к блокам памяти | 1982 |

|

SU1112405A1 |

| Устройство для считывания сигналов из накопителя | 1975 |

|

SU570919A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1287234A1 |

| НАКОПИТЕЛЬ ПОСТОЯННОГО ЗАПОМИН.ЛЮЩЕГО УСТРОЙСТВА | 1973 |

|

SU409295A1 |

| ДОЛГОВРЕМЕННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ТРАНСФОРМАТОРНОГО ТИПА С ЗАПИСЬЮ ЧИСЕЛ В СИСТЕМЕ СЧИСЛЕНИЯ С ОСНОВАНИЕМ Р, БОЛЬШИМ ДВУХ | 1973 |

|

SU393771A1 |

| Постоянное запоминающее устройство | 1972 |

|

SU466551A1 |

Авторы

Даты

1977-10-15—Публикация

1972-05-12—Подача