Изобретение относится к автоматике и вычислительной технике, а именно к постоянным запоминающим устройствам, преимущественно, электронных вычислительных машин и является усовершенствованием известного устройства, описанного в авт. св. № 1196951.

Целью изобретения является повышение помехоустойчивости ПЗУ.

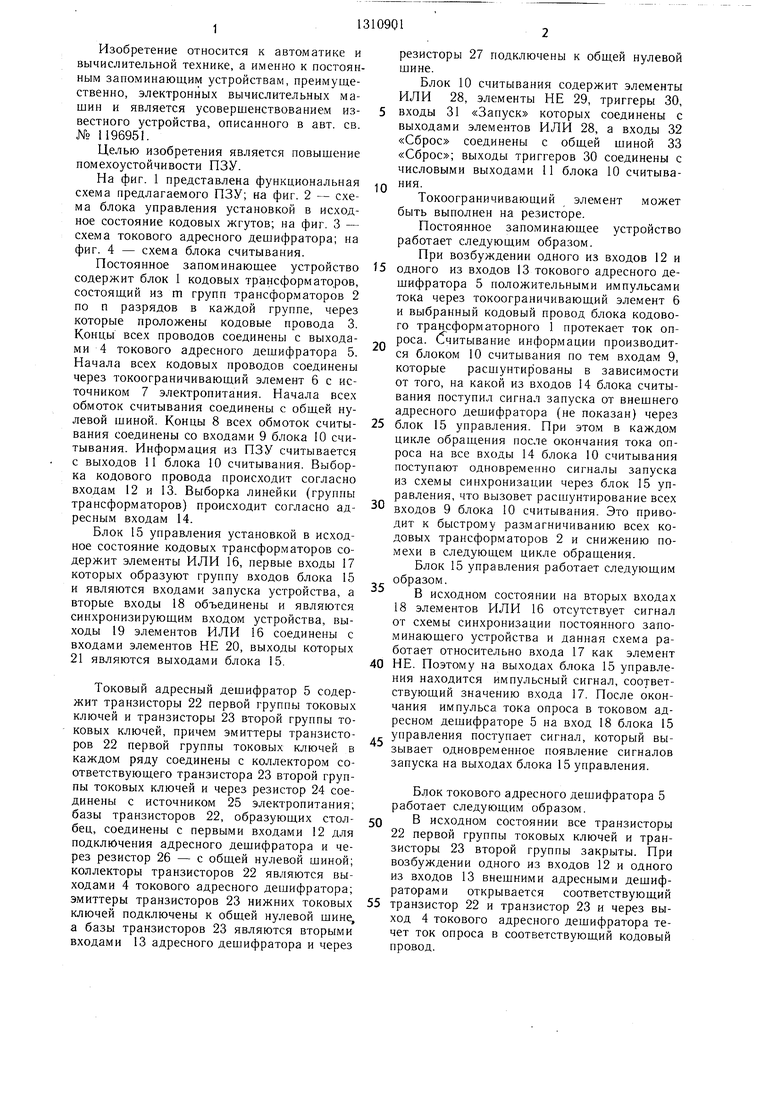

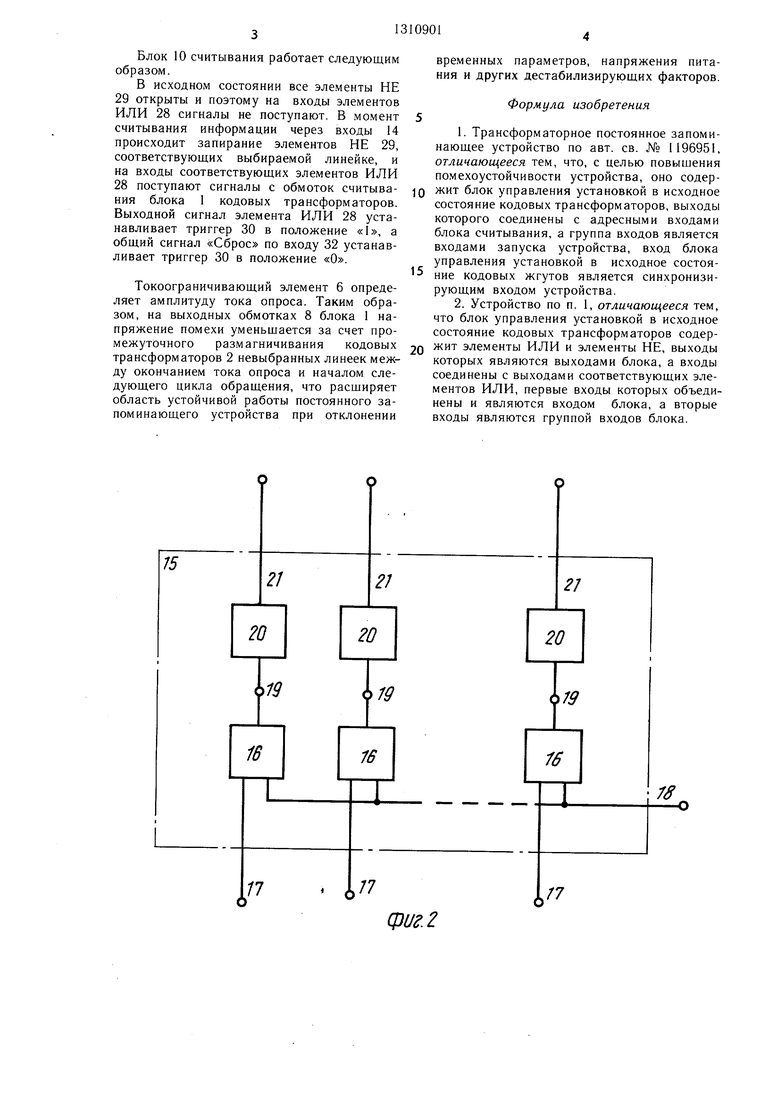

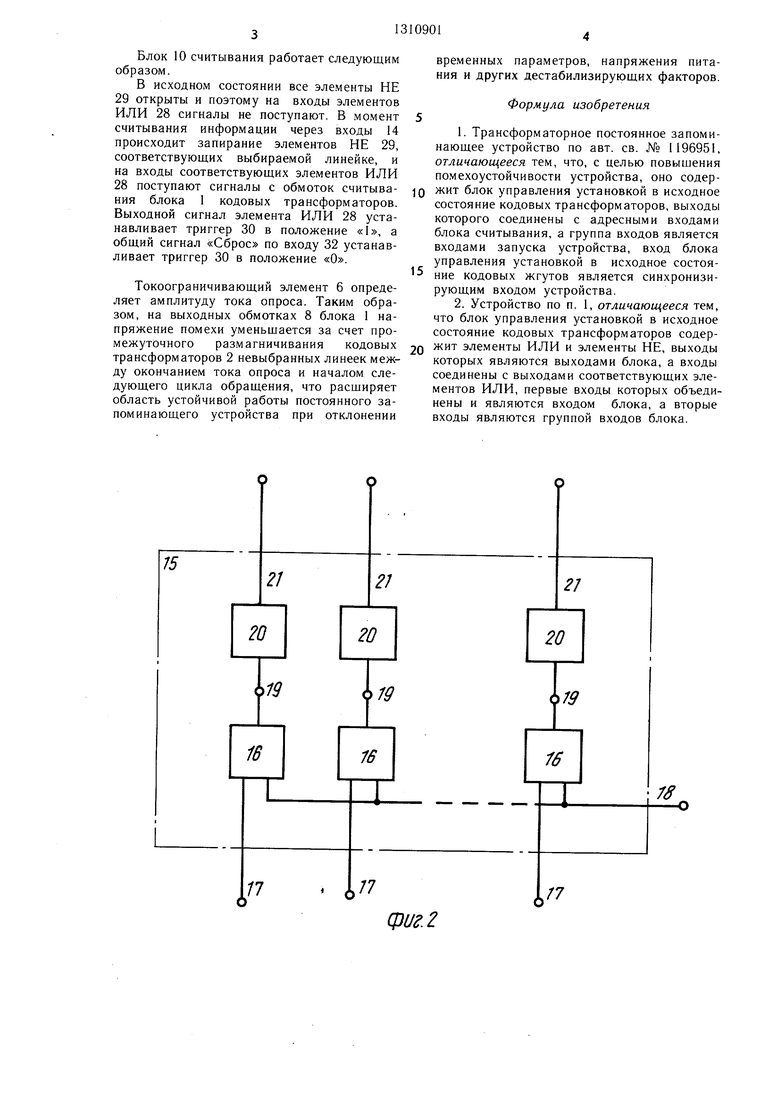

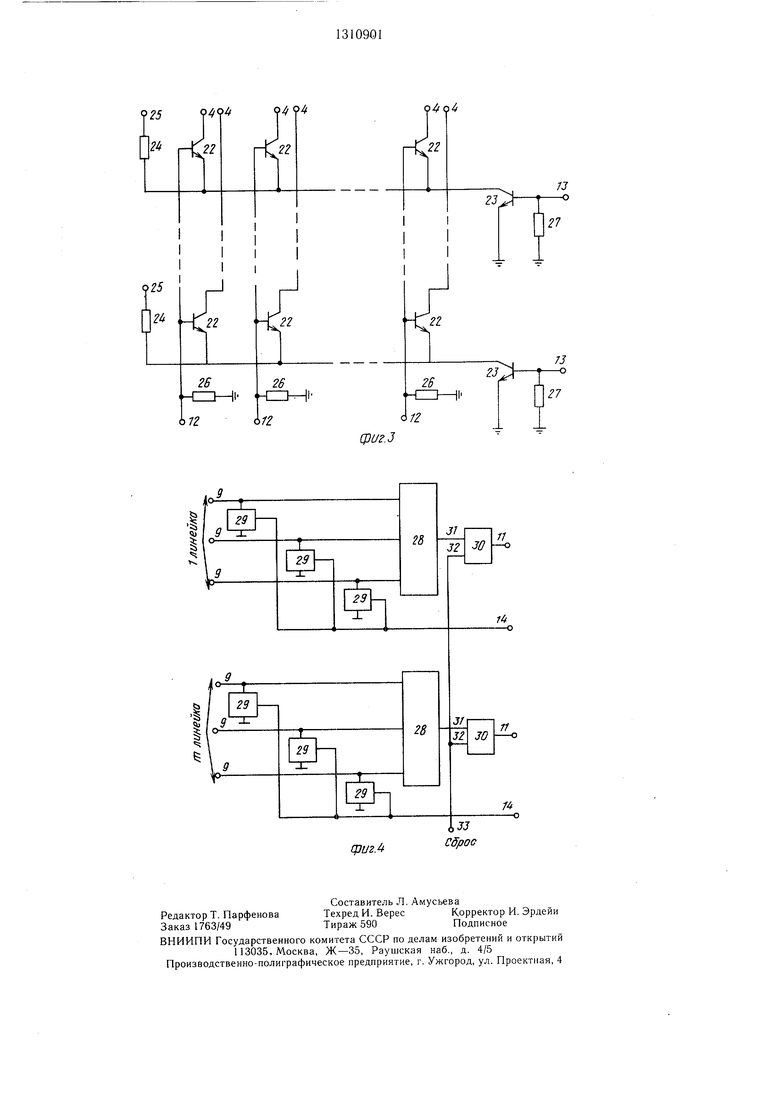

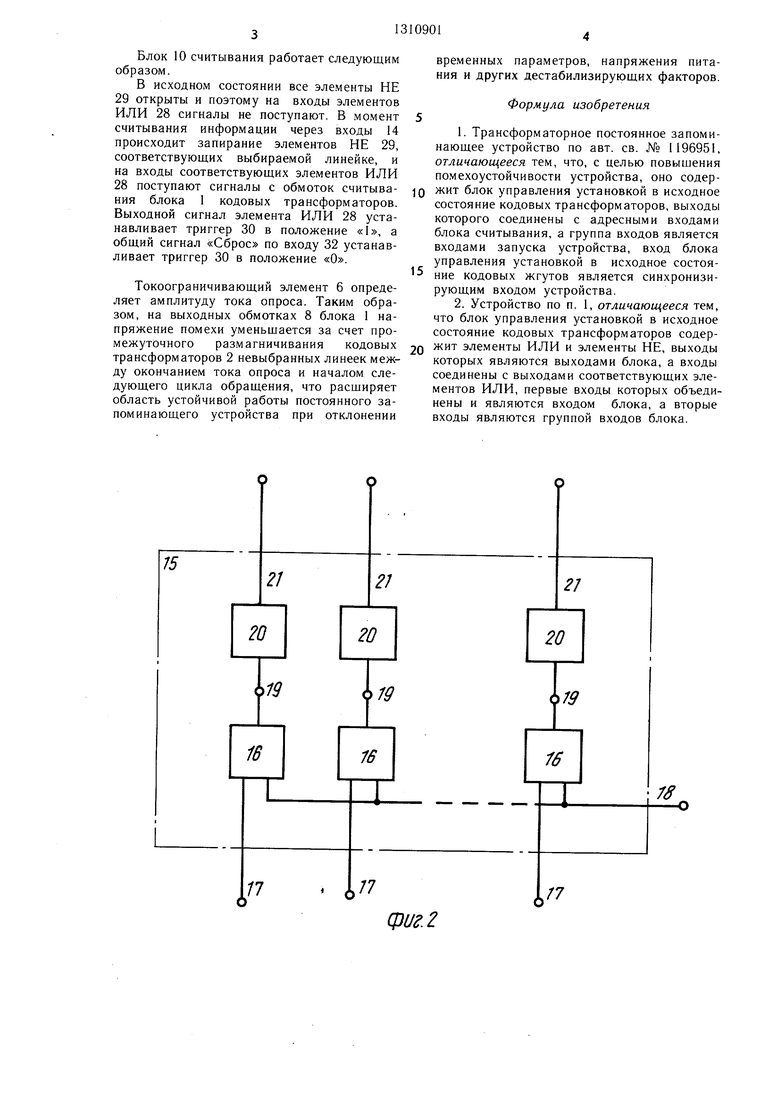

На фиг. 1 представлена функциональная схема предлагаемого ПЗУ; на фиг. 2 - схема блока управления установкой в исходное состояние кодовых жгутов; на фиг. 3 - схема токового адресного дешифратора; на фиг. 4 - схема блока считывания.

Постоянное запоминающее устройство содержит блок 1 кодовых трансформаторов, состоящий из m групп трансформаторов 2 по п разрядов в каждой группе, через которые проложены кодовые провода 3. Концы всех проводов соединены с выходами 4 токового адресного дешифратора 5. Начала всех кодовых проводов соединены через токоограничивающий элемент 6 с источником 7 электропитания. Начала всех обмоток считывания соединены с общей нулевой шиной. Концы 8 всех обмоток считывания соединены со входами 9 блока 10 считывания. Информация из ПЗУ считывается с выходов 11 блока 10 считывания. Выборка кодового провода происходит согласно входам 12 и 13. Выборка линейки (группы трансформаторов) происходит согласно адресным входам 14.

Блок 15 управления установкой в исходное состояние кодовых трансформаторов содержит элементы ИЛИ 16, первые входы 17 которых образуют группу входов блока 15 и являются входами запуска устройства, а вторые входы 18 объединены и являются синхронизирующим входом устройства, выходы 19 элементов ИЛИ 16 соединены с входами элементов НЕ 20, выходы которых 21 являются выходами блока 15.

Токовый адресный дешифратор 5 содержит транзисторы 22 первой группы токовых ключей и транзисторы 23 второй группы токовых ключей, причем эмиттеры транзисторов 22 первой группы токовых ключей в каждом ряду соединены с коллектором соответствующего транзистора 23 второй группы токовых ключей и через резистор 24 соединены с источником 25 электропитания; базы транзисторов 22, образующих столбец, соединены с первыми входами 12 для подключения адресного дешифратора и через резистор 26 - с общей нулевой шиной; коллекторы транзисторов 22 являются выходами 4 токового адресного дешифратора; эмиттеры транзисторов 23 нижних токовых ключей подключены к общей нулевой щине, а базы транзисторов 23 являются вторыми входами 13 адресного дещифратора и через

0

5

0

5

0

5

резисторы 27 подключены к общей нулевой шине.

Блок 10 считывания содержит элементы ИЛИ 28, элементы НЕ 29, триггеры 30, входы 31 «Запуск которых соединены с выходами элементов ИЛИ 28, а входы 32 «Сброс соединены с общей шиной 33 «Сброс ; выходы триггеров 30 соединены с числовыми выходами 11 блока 10 считывания.

Токоограничивающий элемент .может быть выполнен на резисторе.

Постоянное запоминающее устройство работает следующим образом.

При возбуждении одного из входов 12 и одного из входов 13 токового адресного дешифратора 5 положительными импульсами тока через токоограничивающий элемент 6 и выбранный кодовый провод блока кодового трансформаторного 1 протекает ток опроса. (Считывание информации производится блоком 10 считывания по тем входам 9, которые расшунтированы в зависимости от того, на какой из входов 14 блока считывания поступил сигнал запуска от внешнего адресного дешифратора (не показан) через блок 15 управления. При этом в каждом цикле обращения после окончания тока опроса на все входы 14 блока 10 считывания поступают одновременно сигналы запуска из схемы синхронизации через блок 15 управления, что вызовет расшунтирование всех входов 9 блока 10 считывания. Это приводит к быстрому размагничиванию всех кодовых трансформаторов 2 и снижению помехи в следующем цикле обращения.

Блок 15 управления работает следующим образом.

В исходном состоянии на вторых входах 18 элементов Р1ЛИ 16 отсутствует сигнал от схемы синхронизации постоянного запоминающего устройства и данная схема работает относительно входа 17 как элемент НЕ. Поэтому на выходах блока 15 управления находится импульсный сигнал, соответствующий значению входа 17. После окончания импульса тока опроса в токовом адресном дещифраторе 5 на вход 18 блока 15 управления поступает сигнал, который вызывает одновременное появление сигналов запуска на выходах блока 15 управления.

БЛОК токового адресного дешифратора 5 работает следующим образом.

В исходном состоянии все транзисторы 22 первой группы токовых ключей и транзисторы 23 второй группы закрыты. При возбуждении одного из входов 12 и одного из входов 13 внешними адресными дещиф- раторами открывается соответствующий

транзистор 22 и транзистор 23 и через выход 4 токового адресного дещифратора течет ток опроса в соответствующий кодовый провод.

Блок 10 считывания работает следующим образом.

В исходном состоянии все элементы НЕ 29 открыты и поэтому на входы элементов ИЛИ 28 сигналы не поступают. В момент считывания информации через входы 14 происходит запирание элементов НЕ 29, соответствующих выбираемой линейке, и на входы соответствующих элементов ИЛИ 28 поступают сигналы с обмоток считывания блока 1 кодовых трансформаторов. Выходной сигнал элемента ИЛИ 28 устанавливает триггер 30 в положение «I, а общий сигнал «Сброс по входу 32 устанавливает триггер 30 в положение «О.

Токоограничивающий элемент 6 определяет амплитуду тока опроса. Таким образом, на выходных обмотках 8 блока 1 напряжение помехи уменьшается за счет промежуточного размагничивания кодовых трансформаторов 2 невыбранных линеек между окончанием тока опроса и началом следующего цикла обращения, что расширяет область устойчивой работы постоянного запоминающего устройства при отклонении

75

21

временных параметров, напряжения питания и других дестабилизирующих факторов.

Формула изобретения

1.Трансформаторное постоянное запоминающее устройство по авт. св. № 1196951, отличающееся тем, что, с целью повышения помехоустойчивости устройства, оно содержит блок управления установкой в исходное состояние кодовых трансформаторов, выходы которого соединены с адресными входами блока считывания, а группа входов является входами запуска устройства, вход блока управления установкой в исходное состояние кодовых жгутов является синхронизирующим входом устройства.

2.Устройство по п. 1, отличающееся тем, что блок управления установкой в исходное состояние кодовых трансформаторов содержит элементы ИЛИ и элементы НЕ, выходы которых являются выходами блока, а входы соединены с выходами соответствующих элементов ИЛИ, первые входы которых объединены и являются входом блока, а вторые входы являются группой входов блока.

2J

2J

20

ЬЮ

76

/

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

| Устройство для сопряжения телеграфных аппаратов с вычислительной машиной | 1975 |

|

SU608149A1 |

| Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1979 |

|

SU773731A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Табличное устройство для модульного умножения в системе остаточных классов | 1971 |

|

SU550636A1 |

| Устройство для выборки информации из блоков памяти типа 2,5д | 1978 |

|

SU765874A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU744730A1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1444736A1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано в постоянных запоминающих I ГТТ 72 12 -12 12 сриг.1 А., сли1976, ЯНО ке и исщих f устройствах и является усовершенствованием известного устройства по авт. св. № 1196951. Целью изобретения является повышение помехоустойчивости ПЗУ. Поставленная цель достигается Тем, что блок 15 управления установкой в исходное состояние кодовых трансформаторов содержит элементы ИЛИ и элементы НЕ. На вы.чод- ных обмотках 8 блока 1 кодовых трансформаторов напряжение помехи будет уменьшаться за счет промежуточного размагничивания групп трансформаторов 2 невыбранных линеек между окончанием тока опроса и началом следующего цикла обращения, что расширяет область устойчивой работы постоянного запоминающего устройства при отклонении временных параметров, напряжения питания и других дестабилизирующих факторов. 1 3. п. ф-лы, 4 ил. i СЛ .77 )// 7/ ,п со 1 о со rs rsj

17

/7

77

фиг. 2

biz

utZ

Редактор Т. Парфенова Заказ 1763/49

Составитель Л. Амусьева Техред И. ВересКорректор И. Эрдейи

Тираж 590Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ери г A

CSpOG

| Дроздов Е | |||

| А., Комарницкий В | |||

| А., Пятибратов А | |||

| П | |||

| Электронные вычислительные машины | |||

| М.: Машиностроение, 1976, с | |||

| Эксцентричный фильтр-пресс для отжатия торфяной массы, подвергшейся коагулированию и т.п. работ | 1924 |

|

SU203A1 |

| Трансформаторное постоянное запоминающее устройство | 1984 |

|

SU1196951A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-05-15—Публикация

1985-04-17—Подача