нительного запомннающехо конденсатора через четве XEjfl дополнительный кпюч подключена к выходу операционного усилителя, а через пятый допол нительный КЛЮЧ соединена с шиной нулевого потенциала, первая обкладка второго дополнительного запоминающего конденсатора через шестой дополнительный ключ соединена с первым выводом первого масштабного резистора, а через седьмой дополнительный ключ подключена к шине нулевого потенциала, вторая обкладка EiToporo дополнительного -запоминающего конденсатора через восьмой дополнительный конденсатор подключена к выходу операционного усилителя, а через девятый дополнительный ключ соединена с шиной нулевого, потенциг ала, выходы источника опорного напряжения, первого и второго дополнительных источников опорного напряжения соответственно через десятый, одиннадцатый и двенадцатый дополнительные ключи подключены к пернюму входу компаратора, второй вход которого соединен с выходом операционного усилителя, третья группа выходов блока управления подключена к управляющим входам соответствующих дополнительных ключей, первый вывод третьего масштабного резистора подключен к шине нулевого потенциала. 2. Преобразователь по п.1, о тличающ-ийся тем, что блок управления содержит генератор тактовых импульсов, выход которого подключен ко входу трехразрядного сдвигового регистра, выходы разрядов которого подключены-к соответствующим синхронизирующим входам

упла формирования управляющих сигналов, а через формирователи импульсов подключены к первым входам г;ервого, второго и элементов И, узел последовате льных приближений, выход старшего разряда которого соединен с вторыми входами первого и третьего элементов И, выходы разрядов узла последовательных приближений подключены к-соответствуюшим тактовым входам узла формирования управляющих сигналов, выходы которого образуют вторую и тре-тью группу выходов блока управления, первый, второй и третийD-триггеры, информационные входы которых соединены и являются входом блока управления, тактовые входы первого и третьегоD-триггеров подключены к выходам первого и третьего элементов И, а тактовый вход второго В триггера соединен с выходом второго формирователя импульсов, второй вход второго элемента И подключен к информационному входу первого D-триггера, выход второго элементам соединен с первым входом узла последовательных приближений, второй вход которого соединен с входом сброса трехразрядного сдвигового регистра и является входом запуска блока управления, выход третьего разряда трехразрядного сдвигового регистра подключен к тактовому входу узла последовательных приближений, выходыDтриггеров подключены к соответствуюши.м информационным входам узла фор-г мирования управляющих сигналов, выходы узла последовательных приближений являются первой группой выходов блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Устройство для интегрирования сигнала | 1988 |

|

SU1571623A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Множительное устройство | 1986 |

|

SU1352509A1 |

| Интегратор | 1978 |

|

SU748439A1 |

| Операционный усилитель с компенсацией дрейфа нулевого уровня | 1977 |

|

SU739549A1 |

| Преобразователь напряжения в интервал времени | 1984 |

|

SU1282331A1 |

| Устройство для перемножения электрических сигналов | 1984 |

|

SU1242991A1 |

| Многопредельный усилитель заряда | 1982 |

|

SU1113754A1 |

1. ЛОГАРИФМИЧЕСКИЙ АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ , содержащий операционный усилитель, источник входного сигнала, через первый ключ подключенный к первому выводу первого масштабного резистора, выход операционного усилителя соединен с первым выводом второго масштабного резистора, первый запоминающий конденсатор, первая обкладка которого через второй ключ подключена к первому выводу первого масштабного резисторау а через третий ключ соединена с шиной нулевого потенциала, вторая обкладка первого запоминающего конденсатора через четвертый ключ подключена к шине нулевого потенциала, а через пятый ключ соединена с выходом операционного усилителя, второй запоминающий конденсатор, первая обкладка которого через Шестой ключ соединена с первым выводом пер- вого масштабного резистора, а через С€5дьмой ключ подключена к tuHae нулевого пЬтенциала, вторая обкладка второго запоминающего конденсатора через восьмой ключ соединена с шиной нулевого потенциала, а через девятый ключ подключена к выходу операционного усилителя, третий, четвертый и пятый масштабные резисторы первые выводы которых соединены с шиной нулевого потенциала, второй вывод каждого из которых соединен с первым выводом соответственно десято о, одиннадцатого и двенадцатого ключей, компаратор, выход которого соединен q входом блока управления, первая группа выходов которого является разрядным выходом преобразо- . вателя, источник опорного напряжения, вторая группа выходов, блока управления соединена с управляю1цими входами ключей,отличаю щ и и с я тем, что, с целью повышения точности преобразования и расширения диапазона преобразуемого i сигнала, в него введены первый и второй дополнительные запоминающие (Л конденсаторы, первый и второй дополнительные источники опорного напряжения, дополнительные масштабные резисторы и дополнительные клюS чи, причем вторые выводы десятого, одиннадцатого и двенадцатого ключей .соединены с инвертирующим входом, операционного усилителя, нёинвертирующий вход которого подключен ко I 4 второму выводу первого масштабного резистора, выход операционного усиto лителя соединен с первыми выводами о первого, второго и третьего .дополнительных масштабных резисторов, W вторые выводы которых соединены со ф вторыми выводами соответственно третьего, четвертого и пятого масштабных резисторов, инвертирующий вход операционного усилителя через первый дополнительный ключ соединен со вторым выводом второго масштабного резистора, первая обкладка первого дополнительного запоминающего конденсатора через второй дополнительный ключ подключена к первому выводу первого масштабного резистора, а через третий дополнительный ключ соединена с шиной нулевого потенциала, вторая обкладка первого допол

Изобретение относится к устройствам преобразования электрического сигнала по логарифмическому закону и может быть использовано в вычислительных машинах.

Известен логарифмический аналогоцифровой преобразователь, содержащий Зс1поминающие устройства, ключи, компаратор, блок управления l.

Однако указанное устройство имеет малое быстродействие и низкую точность работы.

Наиболее близким к предложенному является логарифмический аналогоцифровой преобразователь, содержащий операционный усилитель, выход которого чарез первый масштабный резистор соединен с его инвертирующим входом, который через второй масштабный резистор и первый ключ соединен с шиной нулевого потенциала и через третий масштабный резистор и второй ключ - с выходом источника одного напряжения, источник преобразуемого сигнала, выход которого через третий ключ подключен к неинвертирующему входу -операционного усилителя и через четвертый и пятый ключи соотЕетственно к первым обклад1 ам первого и второго запоминающих конденсаторов, компаратор, выход которого подключен

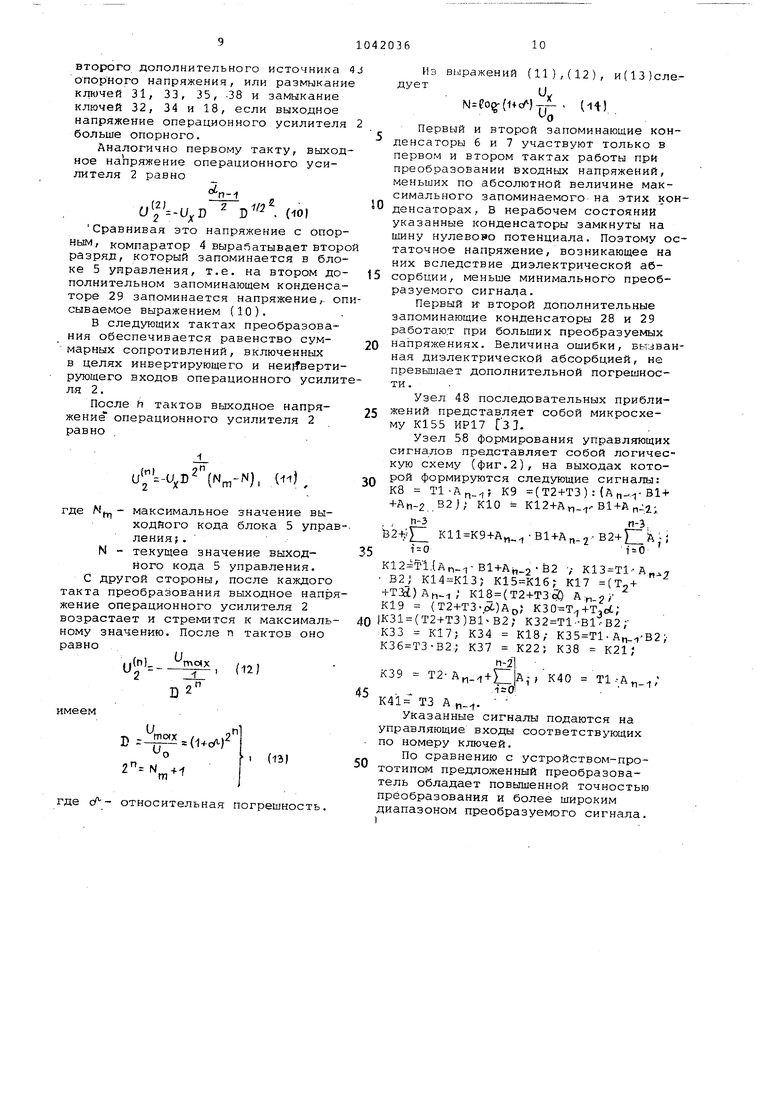

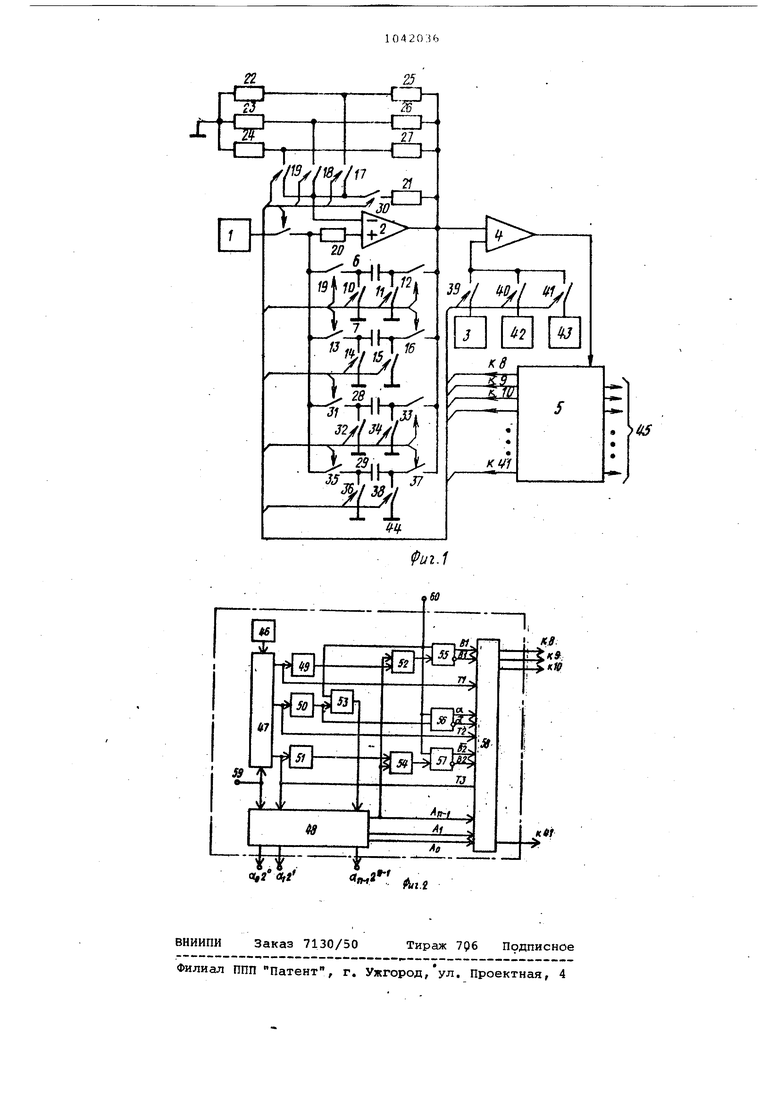

к входу .блока управления и первому входу сдвигового регистра; второй вход которого подключен к выходу блока управлекия, делитель напряжения, дополнительные ключи и блок масштабных резисторов, включенный между инвертирующим .входом операционного усилителя и шиной нулевого потенциала, первые и вторые обкладки первого и второго запоминающих конденсаторов через соответс твующие первый, второй/ третий и четвертый дополнительные ключи подключены к шине нулевого потенциала, вторые об кладки запоминающих конденсаторов через пятый и шестой дополнительные ключи соединены с первым входом компаратора и через делитель напряжения - с выходом операционного уси лителя/ второй вход компаратора соединен с шиной нулевого потенциал выходы блока управления соединены , с управляющими входами ключей fZ рД Недостатком известного преобр зо теля является малая точность преобразования сигналов в большом диапазоне изменения их величин. Цель изобретения - повышение точ ности преобразования Vi расширение диапазона преобразуемого сигнала. Для достижения цели в логарифмический аналого-цифровой преобразо ватель/ содержащий операционный усилитель, источник входного сигнала/ через первый ключ подключенный к первому выводу первого масштабног резистора, выход операционного усилителя соединен с первым выводом второго масштабного резистора, первый запоминающий конденсатор/ первая обкладка которого через второй ключ подключена к первому выводу первого масштабного резистора/ а через третий ключ соединена с шиЧ ной нулевого потенциала/ вторая обкладка первого запоминающего конденсатора через четвертый ключ .подключена к шине нулевого потенциала, а через пятый ключ соединена с выходом операционного усилителя/ второй запо ;1инающий конденсатор, перва обкладка которого через шестой ключ соединена с первым выводом первого масштабного резистора, а через седь мой ключ подключена к шине нулевого потенциала/ вторая обкладка второго запоминающего конденсатора через восьмой ключ соединена с шиной нулевого потенциала, а зерез девятый ключ подключена к выходу операцион ного усилителя/ третий/ четвертый/ и пятый масштабные резисторы/ первые выводы которых соединены с шиной нулевого потенциала/ второй вывод каждого из которых соединен с первым выводом соответственно десятого, одиннадцатого и двенадцатого ключей/ компаратор/ выход которого соединен с входом блока управления, первая группа выходов которого явля ется разрядным выходом преобразователя, источник опорного напряжения, вторая группа выходов блока управления соединена с управляющими входами ключей/ введены первый и второй дополнительные запоминающие конденсаторы, первый и второй дополнительные источники опорного напряжения/ дополнительные масштабные резисторы и дополнительные ключи, причем вторые выводы десятого/ одиннадцатого и двенадцатого ключей соединены с инвертирующим входом операционного усилителя/ неинвертирующий вход которого подключен к второму выводу первого масштабного резистора/ выход операционного усилителя соединен с первыми выводами первого/ второго и третьего дополнительных масштабных резисторов/ вторые выводы которых соединены с вторыми выводами соответственно третьего, четвертого и пятого масштабных резисторов, инвертирующий вход операционного усилителя через первый дополнительный ключ соединен с вторым выводом второго масштабного резистора, первая обкладка первого дополнительного запоминающего конденсатора через второй дополнительный ключ подключена к первому выводу первого масштабного резистора, а через третий дополнительный ключ соединена с шиной нулевого потенциала, вторая обкладка первого дополнительного запоминающего конденсатора через четвертый дополнительный ключ подключена к выходу операционного у силителя, а через пятый дополнительный ключ соединена с шиной нулевого потенциала, первая , обкладка второго дополнительного за;;; поминающего конденсатора через шестой дополнительный ключ соединена с первым выводом первого масштабного резистора, а через седьмой дополнительный ключ подключена к шине }1улевого потенц; ала, вторая обкладка второго дополнительного запоминающего конденсатора через восьмой дополнительный конденсатор подключена к выходу операционного усилителя, а через девятый дополнительный ключ соединена с шиной нулевого потенциала, выходы источника опорного напряжения/ первого и второго дополнительных источников опорного напряжения соответственно через десятый, одиннадцатый и двенадцатый дополнительные ключи подключены к первому входу компаратора, второй вход которого соедий н с выходом операционного усилителя, третья - группа выходов блока управления прдключена к управляющим входам соответствующих дополнительных ключей, первый вход третьего масштабного резистора подключен к шине нулевого по тенциала. При этом блок управления содержит генератор /актовых импульсов, вьоход которого подключен ко входу трехраэрядного сдвигового регистра выходы разрядов которого подключены к соответствутощим синхронизирующим входам узла формирования управляющих сигналов, а через формирова тели импульсов подключены к первым входам первого, второхО и третьего элементов И, узел последовательных приближений, выход старшего разряда которого соединен с вторыми входами первого и третьего элементов выходы разрядов узла последовательных приближений подключены к соответствующим тактовым входам узла формирования сигналов, выходы которого образуют вторую и третью - , группы выходов блока управления, первый, второй и третий D-триггеры, информационные входы которых соединены и являются входом блока управления, тактовые входы первого и третьего D-триггеров подключены к выходам первого и третьего элеме тов И, а тактовый вход второго П триггера соединен с выходом второ го формирователя импульсов, в горой вход второго элемента И подключен к информационному входу первого ГУ-триггера, выход второго элемента с первым входом -узла после довательных приближений, второй вхо которого соединен с входом сброса трехразрядного сдвигового регистра является входом запуска блока управ ления, выход третьего разряда трехразрядного сдвигового регистра подключен к тактовому входу узла последовательных приближений, выходы j5-тpиггepoв подключены к соответствующим информационным входам узла формирования управляющих сигналов, выходы узла последовательных прибли жений являются первой 1руппой выход блока управления. На фиг.1 изображена функциональная схема предложенного логарифмиче кого аналого-цифрового преобразователя; на фиг.2 - то же, блока управ ления . Преобразователь включает источник 1 входного сигнала, операционный усилитель 2, источник 3 опорног напряжения, компаратор 4, блок 5 уп 13авления, первый и второй запоминаю щие конденсаторы 6 и 7, первый, вто рой, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, с диннадцатый и двенадцатый к/почи 8-19, первый, второй, третий; четвертый и пятый масштабные резисторы 20-24, первый, второй и третий дополнительные масштабные резисторы 25, 26 и 27, первый к второй дополнительные запоминающие конденсаторы 28 и 29, первый, второй, третий. чствертьой, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый дополнительные ключи 30-41, первый и второй дополнительные источники 42 и 43 опорного напряжения , шина 44 нулевого потенциала, разр.ядный выход 45 преобразователя. Блок 5 управления содержит генератор 46 тактовых импульсов, трехразрядный сдвиговый регистр 47, узел 48 последовательных приб1 1ижёний,первый,второй и третий формирователи 49, 50 и 51 импульса, первый, второй и третий элементы И 52, 53 и 54, первый, второй и третий D-триггеры 55, 56 и 57, узел 58 формирования управляющих сигналов, вход 59 запуска, вход 60 блока управления. Логарифмический аналого-цифровой преобразователь работает следующим образом, В исходном состоянии ключи 10, 11, 14, 15, 30 и 40 замкнуты, а остальные разомкнуты. При поступлении сигнала Запуск ключ 8 замыкается, преобразуемый сигнал через операционный усилитель 2 с единичным коэффициентом передачи поступает на вход компаратора 4, сигнал с выхода которого через блок 5 управления размыкает ключ 11 и замыкает ключ 12, если преобразуемый сигнал не превышает по абсолютной величине напряжение первого дополнительного источника 42 опорного напряжения, или замыкает ключи 32 и 33, если превышает опорное на-, пряжение. Напряжение первого дополИительного источника 52 опорного напряжения выбирается равным минимальное напряжение преобразуемого сигнала; коэффициент абсорбции конденсаторов. Если минимальное напряжение преобразуемого сигнала составляет 100 мкВ, то на первом запоминающем конденсаторе 6 запоминаются напряжения от О о -100 мВ, а на первом дополнительном запоминающем конденсаторе 28 запоминаются напряжения от - 100 мВ до -5 В. Ка одном из этих конденсаторов запоминается напряжение (28) V UcMнапряжение преобразуемого сигнала; напряжение смещения операционного усилителя 2. После запоминания напряжения размыкаются ключи 8, 40 и 30, а ключи 39 и 17 замыкаются. Одновременно размыкаются ключи 10 и 12 и замыкаютс ключи 9 и 11, если преобразуемый си нал не превышает напряжение первого дополнительного источника, опорного напряжения, или размыкаются ключи 3 и 33 и замыкаются ключи 31 и 34, ее ли преобразуемый сигнал превышает указанное опорное напряжение. В обоих случаях KdHfleHcaTop, на котором запоминалось напряжение, пе реключается так, что к неинвертирую щему входу операционного усилителя через первый масштабный резистор 20 подключается напряжение, определяем выражением (2), отрицательного знака. Первый дополнительный масштабный резистор 25 и третий масштабный резистор 22 выбираются из условия R, к :и;25;р1/2 (,, i 22 22 25 р. р i j, D TO-- o/i- o-f (1 где 20 сопротивления COOT 22 I ветственно первого, второго, третьего масштабных резисторов 20, 21 и 22, первого дополнительного масштабного резистора 25; D - динамический диапа зон преобразователя На выходе операционного усилите ля 2 устанавливается напряжение -U;xD /2 . . (5) В момент этого установления компаратором 4 сравниваются напряжения (5) .и напряжение источника 3 опорного напряжения. Если выходное напряжение опера- ционного усилителя 2 не повышает наг пряжение источника 2 опорного напряжения, то блок 5 управления размыкает ключ 39 и замыкает ключ 41, а напряжение на выходе операционного усилителя 2 остается неизменным. Если выходное напряжение операционного усилителя 2 больше напряжения источника 3 опорного напряжения, то блок 5 управления размыкает ключи 39, 17 и замыкает ключи 41,30.В результате операционный усили тель 2 работает в режиме повторителя, выходное напряжение которого равно пре образуемому с отрицательным знаком. Для двух рассмотренных случаев ,D 2 , (Ь, где п - число разрядов. После установления напряжения в соответствии с (6) блок 5 управления в третий раз в первом такте преобразования проверяет состояние компаратора 4, сравнивающего выходное напряжение операционного усилителя 2 с напряжением второго дополнительного источника 43 опорного напряжения. Если выходное напряжение операционного усилителя 2 не превы1иает это опорное напряжение, то блок 5 управления размыкает ключи 15, 41 и замыкает ключи 16, 39 и начинается . заряд второго запоминающего конденсатора 7, на котором запоминаются напряжения от О до 100 мВ до напряжения d, .D 2 ,7f29)2 f Если выходное напряжение операционного усилителя 2 больше напряжения второго дополнительного источника 43 опорного напряжения, то блок 5 управления размыкает ключ 41, замыкает ключи 36, 37 и 39, и начинается заряд второго дополнительного запоминающего конденсатора 29,работающего с напряжениями от 100 мВ до 5 В. После окончания переходного п1роцесса запоминания начинается второй такт преобразования с размыкания ключа 17 и замыкания ключа 30. Одновременно с этим происходит размыкание ключей 9, 11, 14, 1б и замыкание ключей 10, 12, 13 и 15, если выходное напряжение операционного усилителя 2 не больше напряжения второго дополнительного источника 43 опорного напряжения, или размыкание ключей 9, 31, 34, 36, 37 и замыкание ключей 10, 32, 33, 35 и 38, если выходное напряжение операционного усилителя 2 больше опорного i В обоих случаях конденсатор, на котором запомнилось напряжение , переключается так, что к неинвертирующему входу операционного усилителя 2, работающему в это время в качестве повторителя, подключается запомненное напряжение с .отрицательным знаком. Сопротивления четвертого масштабного резистора 23 и второго дополнительного масштабного резистог ра 26 выбираются из условия .х(2 , гь.г)111 (8) . о 23 2Ь 2Ъ 2Ь RT, - сопротивления четвертьтого масштабного резистора 23 и второго дополнительного масштабного резистора 26 . Послезапоминания происходит разыкание ключей 10, 12, 13, 17 и заыкание ключей 9, 11, 14 и 18, если выходное напряжение операционного усилителя 2 не превышает напряжение второго дополнительного источника опорного напряжения, или размыкан ключей 31, 33, 35, -38 и замыкание ключей 32, 34 и 18, если выходное напряжение операционного усилител больше опорного. Аналогично первому такту, выхо ное напряжение операционного усилителя 2 равно г ,D . (101 Сравнивая это напряжение с опо ным, компаратор 4 вырабатывает вто разряд, который запоминается в бло ке 5 управления, т.е. на втором до полнительном запоминающем конденса торе 29 запоминается напряжение,, о сываемое выражением (10). В следующих тактах преобразования обеспечивается равенство суммарных сопротивлений, включенных в целях инвертирующего и неиИверти рующего входов операционного усили ля 2. После h тактов выходное напряжение операционного усилителя 2 равно .-u,D (), М максимальное значение выходйого кода блока 5 упра ления;, N - текущее значение выходного кода 5 управления. С другой стороны, после каждого такта преобразования выходное напр жение операционного усилителя 2 возрастает и стремится к максималь ному значению. После п тактов оно TV . motx :() ., где относительная погрешность. ,(12), и(13)слевыражений(14сЛ)-|-| . (1) Первый и второй запоминающие конденсаторы 6 и 7 участвуют только в первом и втором тактах работы при преобразовании входных напряжений, меньших по абсолютной величине максимального запоминаемого на этих конденсаторах, В нерабочем состоянии указанные конденсаторы замкнуты на шину нулевого потенциала. Поэтому остаточное напряжение, возникающее на них вследствие диэлектрической абсорбции, меньше минимального преобразуемого сигнала. Первый и второй дополнительные запоминающие конденсаторы 28 и 29 работают при больших преобразуемых напряжениях. Величина ошибки, вызванная диэлектрической абсорбцией, не превышает дополнительной погрешности . Узел 48 последовательных приближений представляет собой микросхему К155 ИР17 ГЗЗ. Узел 58 формирования управляющих сигналов представляет собой логическую схему (фиг.2), на выходах которой формируются следующие сигналы: Кб Т1-А,,; К9 (Т2+ТЗ) : (Af,.-Б1 + -f-An-2 ,B2j, KlO ь К12-ЬА 1 -Bl+Ap i; n-Эп-3. 2+.; (-А„ В1-1-Ап 2 , f 0 ,(An-i- В2 К13 Т1-А В2; К17 (Т2-г 1-тЯ) К18 (Т2+ТЗсО A.yi.j/ 19 (T2+T3-,ot)Ao; ,ct; 31 (T2+T3)Bl«B2; .-В1.-В2; ЗЗ К17; К34 KlB,- - ,-B2/ Зб ТЗ-В2; K37 K22; K38 K21; rt-2l 39 , K40 ТЬ.А,; ,4i T3 A f,.. Указанные сигналы подаются на правляющие входы соответствующих о номеру ключей. По сравнению с устройством-проотипом предложенный преобразоваель обладает повышенной точностью реобразования и более широким иапазоном преобразуемого сигнала.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логарифмический аналого-цифровой преобразователь | 1978 |

|

SU675598A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 756628, кл.-Н 03 К 13/17, 1980 (прототип). | |||

| , 3 | |||

| Электронная промышленность, 1978, it 8, с.14-18. | |||

Авторы

Даты

1983-09-15—Публикация

1982-02-22—Подача