1

Изобретение относится к вычислительной технике и может быть использовано при разработке специализированных вычислительных устройств.

Известны устройства для вычислен корредяционной функци.и, в котором для хранения аргументов используются каскады регистров сдвига, входы и выходы которых коммутируются в определенном порядке на входы блока умножения 1,

Это устройство содержит блок выделения модуля, делители напряжения блок адреса и другие нестандартные, блоки, что приводит к большим аппаратурным затратам.

Наиболее близким к предлагаемому является устройство для вычислениякорреляционной функции, содержащее синхронизатор, соединенный с управ ляющими входами коммутатора и блока умножения, информационный вход которого соединен с выходом блока умножения, а выходы - со входами накапливающих сумматоров, многокаскадный сдвиговый регистр, выходы всех каскадов которого переключаютс дополнительным коммутатором 2,

Построение такого устройства требует также больших аппаратурныхзатрат, а большое число связей не дает возможности использовать для его построения многоразрядные сдвиговые динамические регистры с ограниченным числом внешних выводов.

Цель изобретения - упрощение коррелометра.

Указанная цель-достигается тем, что в коррелометр, содержащий

0 регистры сдвига, коммутатор, информационный вход которого подключен к информационному выходу блока умножения, выходы соединены со входгми соответствующих накапливающих сумма5торов, введены блок управления, семь- элементов И, два элемента ИЛИ и маркерный регистр,первые входы первого и второго элементов И являются соответственно первым и вторым

0 -информационным входами коррелометра, входом синхронизации которого является первый вход блока управления, второй и третий входы которого соединены соответственно с управляющим

5 выходом блока умножения и с выходом маркерного регистра, первые входы .третьего и четвертого элементов И соединены .соответственно с выходам; второго и первого регистров сдвига,

0 первые входы пятого и шестого

элементов И подключены соответственно к выходам первого и второго регистров сдвига, входы которых соединены с выход-ами соответствующих Элементов ИЛИ, входы первого элемента ИЛИ подключены соответственно к выходам первого, второго и третьего элементов И, а входы второго элемента ИЛИ , соединены соответственно с выходами четвертого, пятого и шестого элементов И, выход седьмого элемента И соединен с управляющим входом маркерного регистра выход которого объединен с его входом, первый и второй информационные входы блока умножения подключены соответственно к выходам третьего и шестого элементов И, уп завляющий вход блока умножения подключен к первому выходу блока управления, второй выход которогосоединен с управляющим входом коммутатора, третий выход блока управления подключен ко вторым входам второго, третьего, пятого, шестого элементов Ник первому входу седьмого элемента И, четвертый выход блока управления соединен со вторыми входами первого четвертого и,седьмого элементов И, с .третьими входами второго и пятого элементов И, третий вход седьмого элемента И соединен со входом синхронизации коррелометра.

Кроме того, б.лок управления содержит три триггера, счетчик, дешифратор, четыре элемента задержки:, шесть элементов И и два элемента ИЛИ первый вход первого элемента И объединен со входом первого элемента задержки и является первым входом блока управления, второй вход которого соединен с первыми входами второго и третьего элементов И, четвертый вход блока управления соединен с первыми входами четвертого и пятого элементов И, первым, вторым третьим и четвертым выходам блока управления являются соответственно выход второго элементу задержки, выходы дешифратора, выход первого триггера и выход второго триггера являются соответственно первым, вторым, третьим и четвертым выходами блока управления, С и D - входы второго триггера соединены соответт ственнр с выходом четвертого элемента И и с первым выходом дешифратора, выход второго триггера подключен к nepBOfv входу шестого элемента И, второй вход которого через третий элемент задержки подключен к выходу четвертого элемента И, выход шестого элемента И оединен с первыми входами элементов ИЛИ, вторые входы которых подключены к выходу второго элемента И, второй вход которого объединен со вторым входом третьего элемента И и подключен к последнему зыходу дешифратора, вторые входы

четвертого и пятого элементов И соединены с выходами первого элемента задержки, вход второго элемента задержки подключен к выходу первого элемента И, входы дешифратора подключены соответст венно к разрядным выходам счетчика, выход первого элемента ИЛИ соединен со счетным входом счетчика, вход уста1новки нуля которого подключен к выходу третьего элемента И, входы С и D первого тригге за подк лючены соответственно к выходу пятого элемента И и к выходу третьего триггера, единичный вход которого подключен к выходу второго элемента ИЛИ а нулевой - к выходу четвертого элемента задержки, вход которого соединен с. выходом пятого элемента И, выход первого триггера соединен со вторым входом первого элемента И.

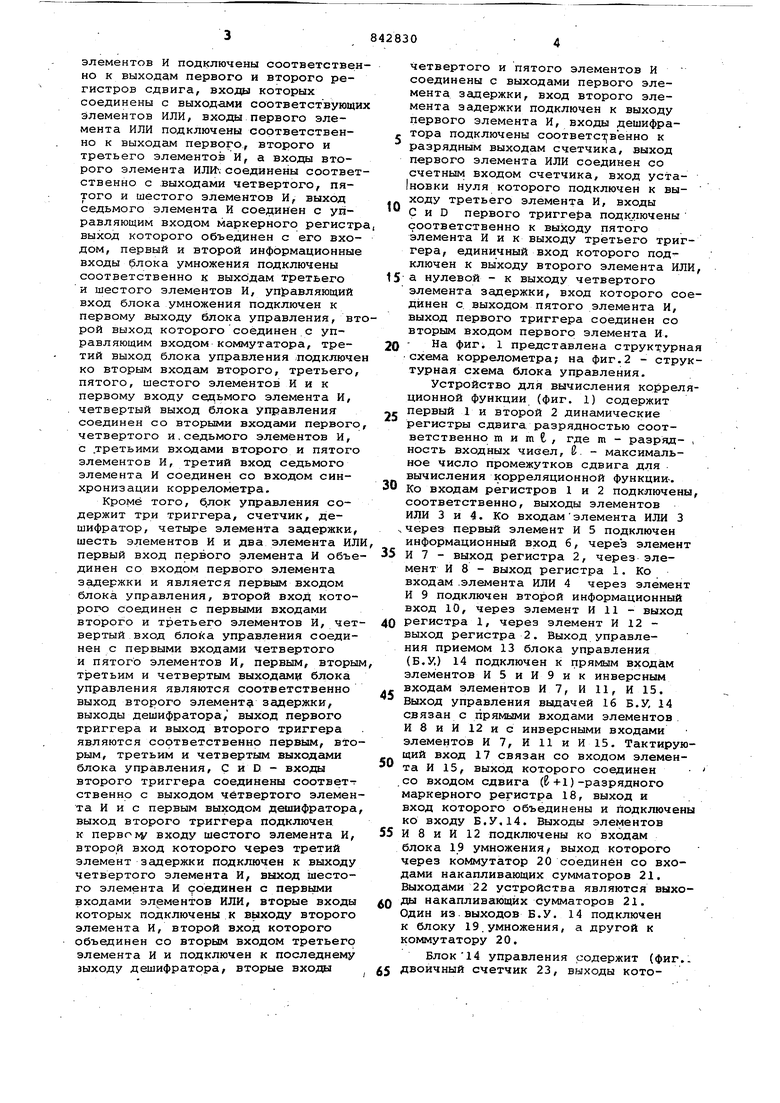

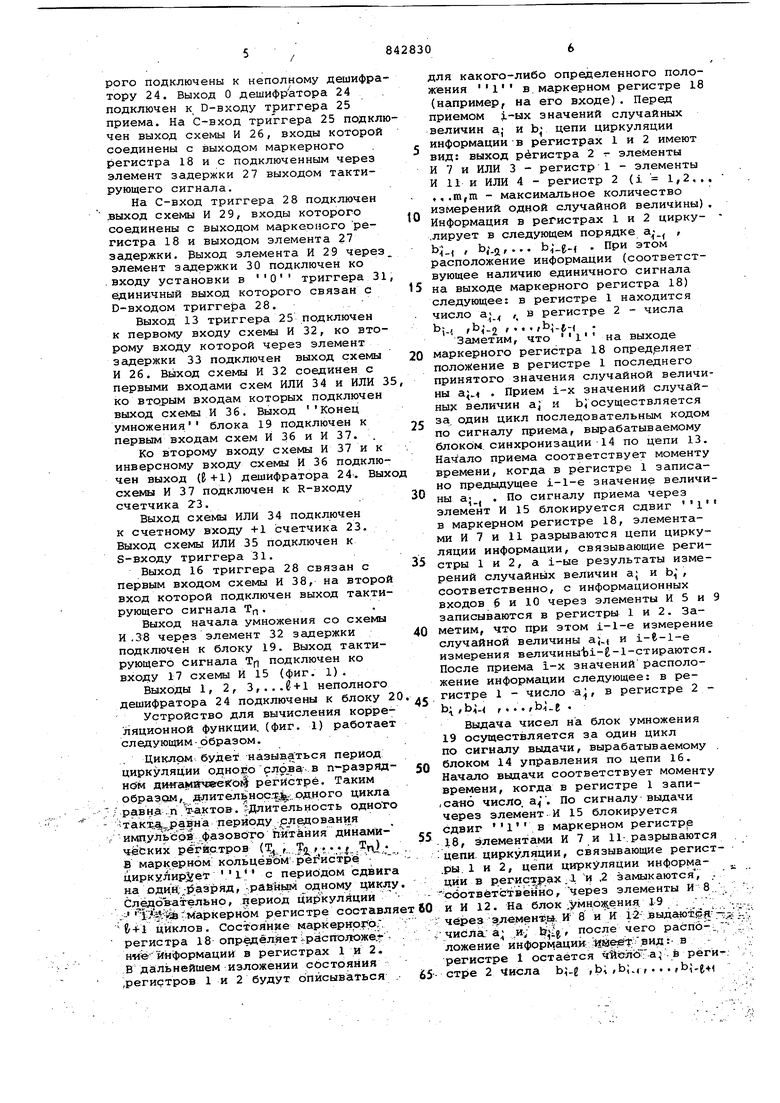

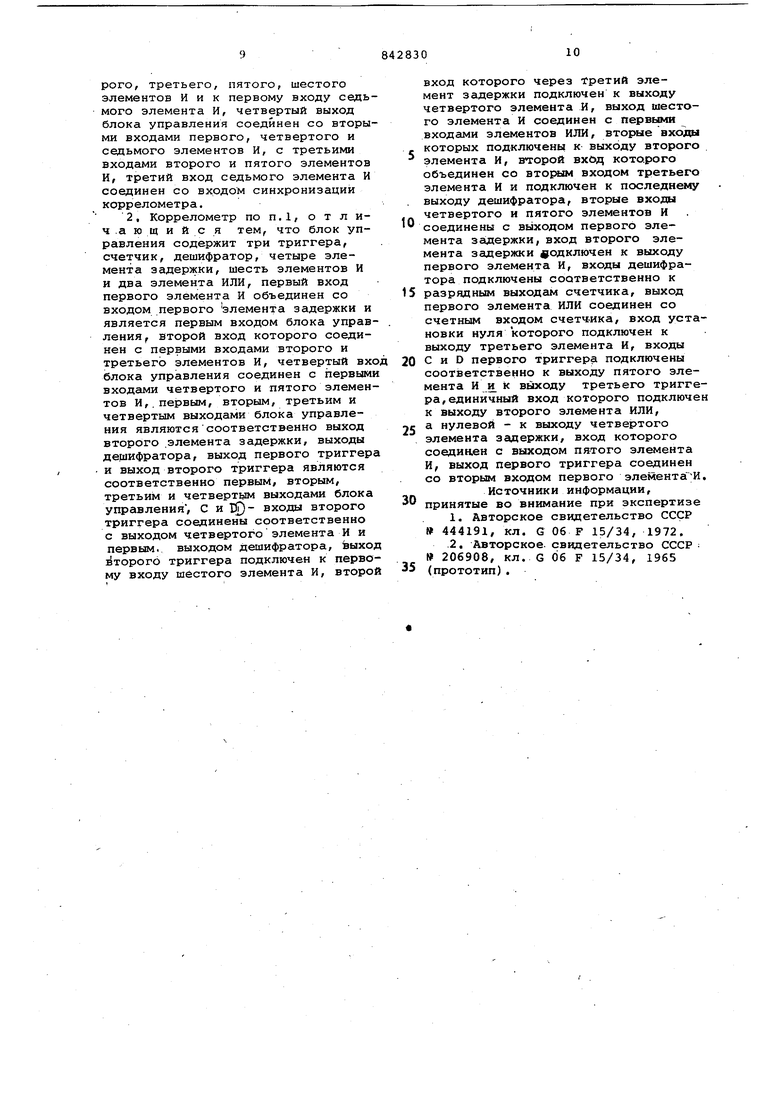

На фиг; 1 представлена структурна схема коррелометра; на фиг.2 - структурная схема блока управления.

Устройство для вычисления корреляционной функции (фиг. 1) содержит первый 1 и второй 2 динамические регистры сдвига разрядностью соответственно m и m . , где m - разрядность входных чисел, С. - максимальное число промежутков сдвига для вычисления корреляционной функции-. Ко входам регистров 1 и 2 подключены соответственно, выходы элементов ИЛИ 3 и 4. Ко входамэлемента ИЛИ 3

,через первый элемент И 5 подключен информационный вход 6, через элемент И 7 - выход регистра 2, через элемент И 8 - выход регистра 1. Ко входам .элемента ИЛИ 4 через элемент И 9 подключен второй информационный вход 10, через элемент И 11 - выход регистра 1, через элемент И 12 выход регистра 2. Выход управления приемом 13 блока управления (Б,У,) 14 подключен к прямым входам элементов И 5 и И 9 и к инверсным входам элементов И 7, И 11, И 15, Выход управления выдачей 16 Б.У, 14 связан с прямыми входами элементов. И 8 и И 12 и с инверсными входами элементов И 7, И 11 и И 15. Тактирующий вход 17 связан со входом элемента И 15, выход которого соединен

,со входом сдвига (К+1)-разрядного маркерного регистра 18, выход и вход которого объединены и подключен ко входу Б.У.14. Выходы элементов И 8 и И 12 подключены ко входам блока 19 умножения/ выход которого через коммутатор 20 соединён со входами накапливающих сумматоров 21. Выходами 22 устройства являются выхода накапливающих сумматоров 21. Один из выходов Б.У. 14 подключен к блоку 19.умножения, а другой к коммутатору 20.

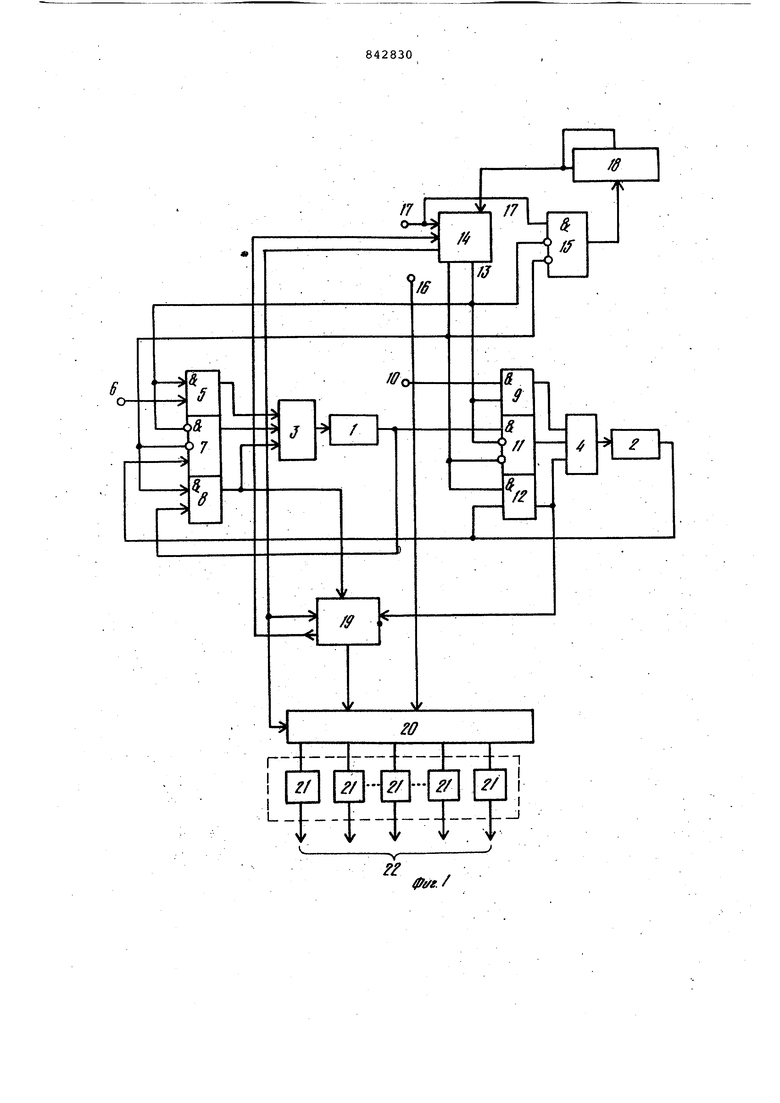

Блок14 управления содержит (фиг. двоичный счетчик 23, выходы которого подключены к неполному дешифр тору 24. Выход О дешифратора 24 подключен к D-входу триггера 25 приема. На С-вход триггера 25 подк чен выход схемы И 26, входы которо соединены с выходом маркерного регистра 18 и с подключенным через элемент задержки 27 выходом тактирующего сигнала. На С-вход триггера 28 подключен выход схемы И 29, входы которого соединены с выходом маркерного регистра 18 и выходом элемента 21 задержки. Выход элемента И 29 чере элемент задержки 30 подключен ко триггера 3 входу установки в единичный выход которого связан с D-входом триггера 28. Выход 13 триггера 25 подключен к первому входу схемы И 32, ко вто рому входу которой через элемент задержки 33 подключен выход схемы И 26. Выход схемы И 32 соединен с первыми входами схем ИЛИ 34 и ИЛИ ко вторым входам которых подключен выход схемы И 36. Выход Конец умножения блока 19 подключен к первым входам схем И 36 и И 37. Ко второму входу схемы И 37 и к инверсному входу схемы И 36 подклю чен выход (E+l) дешифратора 24. Вы схемы И 37 подключен к R-входу счетчика . Выход схемы ИЛИ 34 подключен к счетному входу +1 счетчика 23. Выход схемы ИЛИ 35 подключен к S-входу триггера 31. Выход 16 триггера 28 связан с первым входом схемы И 38, на второ вход которой подключен выход такти рующего сигнала Т,. Выход начала умножения со схемы И .38 через элемент 32 задержки подключен к блоку 19. Выход тактирующего сигнала Тр подключен ко входу 17 схемы И 15 (фиг. 1). Выходы 1, 2, 3,...С+1 неполного дешифратора 24 подключены к блоку Устройство для вычисления корре ляционной функции, (фиг. 1) работае следующим-образом. . Циклом будет называться период циркуляции одно)|о слова-..в п-разряд ном ди амйвеёк;оЙ регистре. Таким образом,, ялительнос..-;.одного цикла равца .п /%-актов. гДлительность одного -такз а равгна периоду с/1едования имп.уЛьсов .фазовото питания динамических регйс.тров (Т , т,,..., TnjJ . в маркерном кольцевом регистре циркулирует с периодом сдвига на один;;15азряд, -равным одному циклу Следбватвльно, ериод циркулйции .- 1М:ш:Маркерном регистре составля f + l Циклов. Состояние маркеркргЪ;. регистра 18 определяет расположе.г H«feинформации в регистрах 1 и 2. В да:Л15нейшем изложении состояния (Регистров 1 и 2 будут описываться для какого-либо определенного положения 1 в. маркерном регистре 18 (например, на его входе). Перед приемом JL-ых значений случайных величин а; и цепи циркуляции информацииВ регистрах 1 и 2 имеют вид: выход регистра 2 - элементы И 7 и ИЛИ 3 - регистр 1 - элементы И 11 и ИЛИ 4 - регистр 2 (i 1,2... ,,.m,m - максимальное количество измерений одной случайной величины). Информация в регистрах 1 и 2 циркулирует в следующем порядке . , Ц, , Ь/.д,... . При этом расположение информации (соответствующее наличию единичного сигнала на выходе маркерного регистра 18) следующее: в регистре 1 находится число aj , в регистре 2 - числа t Заметим, что на выходе маркерного регистра 18 опред,еляет положение в регистре 1 последнего принятого значения случайной величины а. . Прием i-x значений случайных величин а; и Ь осуществляется за, один цикл последовательным кодом по сигнсшу приема, вырабатываемому блокЬм. синхронизации 14 по цепи 13. Начало приема соответствует моменту времени, когда в регистре 1 записано предыдущее i-1-e значение величины . По сигналу приема через элемент И 15 блокируется сдвиг i в маркерном регистре 18, элементами И 7 и 11 разрываются цепи циркуляции информации, связывающие регистры 1 и 2, а i-ые результаты измерений случайных величин а; и Ь, , соответственно, с информационных входов 6 и 10 через элементы И 5 и 9 записываются в регистры 1 и 2. Заметим, что при этом i-1-e измерение случайной величины а;.( и i-i-1-e измерения величиныЬ1- -1-стираются. После приема i-x значений расположение информации следующее: в регистре 1 - число -а, в регистре 2 Ь /Ь;. ,. .. ,bi.g , Выдача чисел на блок умножения 19 осуществляется за один цикл по сигналу выдачи, вырабатываемому блоком 14 управления по цепи 16. Начало выдачи соответствует моменту времени, когда в регистре 1 записа-н6 число, а. По сигналу выдачи через элемент.И 15 блокируется в маркерном регистру 18, элементами И 7 и 11-.разрываются . цепи, циркуляции, связывающие регистры. 1 и 2, цепи циркуляции информа- ,. ци в регистрах.i и ,2 замыкаются , .сботвётствённо, через элементы И 8.. и И 12. На блок :,умнржени. .1.9 : ..... чёреэ эдемен ь1. И 8 и И Г2-: овыдаютёЗ- д: J числа а .И-; fer,4j г после чего расп6-,;7 ; ложение информации-Шеет.вид : в регистре 1 остаётся ч11ел Га в рёги-. стре 2 числа bi-g b; ,b;., , .. . ,b;,j. Т.е. произошла подготовка к выдаче следующей пары чисел а;и Ь.. После ВБщачи на блок умножения 19 всех I пар чисел aj и Ь( i -, i t+l, ,, , i) расположение информации в регистрах 1 и 2 примет перво начальный вид: в регистре 1 - числ а в регистре 2 - числа Ь,Ь;., ,,. .. ., . Устройство готово к приему следующих i+1-x результатов измерений. Произведение всех пар чисел А и Ь через коммутатор 20 за сится в соответствующий накапливающий сумматор 21 k(,2, . ,,е) . Блок управления (фиг.2) работае следующим образом. В начале работы при нулевом сос тоянии счетчика 23 (на выходе 0) . дешифратора - логическая единица) при появлении на входе элемента И сигнала МР с выхода маркериого регистра 18 по сигйалу начала цикла ТТ (задержанный на элементе 27 на один сигнал Тр) , CD-триггер 2 устанавливается в единичное состоя ние. На его выходе 13 формируется сигнал управления приемом (Прием По сигналу с выхода элемента И 26, задержанному на 2-3 элементом задержки 33, при наличии сигнала Прием к счетчику 23 через элемент И 32 и 34 прибавляется , SR-триггер 31 через элемент ШШ 35 устанавливается в единичное состоя ние. На выходе О дешифратора 24 ус навливается нулевой сигнгш, на вых |де 1 - единичный. Следующим сигналом ТТ CD-тригге 25 устанавливается в нулевое состо ние, а CD-триггер 28 через элемент И 29 - в единичное состояние, так как сдвиг маркерной единицы блокируется сигналом Прием (элемент И 15 фиг. 1). Таким образом, на выходе 13 CD-триггера 25 формируется сигнал Прием длительностью один цикл. Задержанным на 2 такта на элеме те 30 сигналом с выхода элемента И 29 SR-триггер 31 сбрасывается в ноль. На выходе 16 CD-триггера 28 форм руется единичный сигнал Вьщача По сигналу Tf, через элемент задержки 39 на блок умножения 19 выдается Начало умножения сигнал следующему сигналу ТТ с выхода элеиента И 29 (на выходе триггера 31нулевсй сигнал) CD-триггер 28 сбрасывается в ноль . При выполнении цикла умножения на выходах 13 и 16 - сигнал и маркерная единица-в каждом цикле по сигналу Т сдвигается на один разряд. По сигналу Конец умножения с блока 19 при состояниях 1,2,3,... счетчика 23 (на инверсном входе эле мента И 36 единичный сигнал) через элемент ИЛИ 34 к содержимому счетчика 23 прибавляется единица. RS-триггер 31 устанавливается вновь в единицу, а значит последующий единичный сигнал с выхода схемы И 29 вновь установит С|1-триггер 28 в единицу, а по сигналу Т через элемент И 38 и элемент задержки 39 вьщается очередной сигнал Начало умножения , после циклов умножения счетчик 23 установится в состояние +1. Сигналом Конец умножения (на выходе (&+1) дешифратора 24,единица) счетчик 23 через элемент И 37 сбрасывается в О затем цикл работы устройства повто Ряется.. Формула изобретения 1. Коррелометр, содержащий регистры сдвига, коммутатор, информационный вход которого подключен к информационному выходу блока умножения, а выходы соединены со входами соответствующих накапливающих сумма- . торов, отличающийся тем, что, с целью упрощения, в коррелометр введены блок управления, семь элементов И, два элемента ИЛИ и в маркерный регистр, первые входы первого и второго элементов И являются соответственно первым и вторым информационными входами коррелометра, входом синхронизации которого является первый вход блока умножения, второй и третий входы которого соединены соответственно с управляющим выходом блока умножения и с выходом маркерного регистра, первые входы третьего и четвертого элементов И соединены соответственно .с выходами второго и первого регистров сдвига, первые входы пятого и шестого элементов И подключены соответственно к выходам первого и второго регистров сдвига, входы которых соединены с выходами соответствующих элементов ИЛИ, входы первого элемента ИЛИ подключены соответственно к выходам первого, второго и третьего элементов и, а входы второго элемента ИЛИ соединены соответственно с выходами четвертого, пятого и шестого элементов И, выход седьмого элемента И соединен с , управляющим входом маркерного регистра, выход которого объединен с его входом, первый и второй информационный входал блока умножения подключены соответственно к выходам третьего и шестого элементов И, управляющий вход блока умножения подключен к первому выходу блока управления, второй выход которого соединен с управляющим входом коммутатора, третий-выход блока управления подключен ко вторым входам второго, третьего, пятого, шестого элементов И и к первому входу седьмого элемента И, четвертый выход блока управления соединен со вторыми входами первого, четвертого и седьмого элементов И, с третьими входами второго и пятого элементов И, третий вход седьмого элемента И соединен со входом синхронизации коррелометра.

2, Коррелометр по п.1, о т л ич .а ю щ и и с я тем, что блок управления содержит три триггера, счетчик, дешифратор, четыре элемента задержки, шесть элементов И и два элемента ИЛИ, первый вход первого элемента И объединен со входом первого элемента задержки и является первым входом блока управления, второй вход которого соединен с первыми входами второго и третьего элементов И, четвертый вхо блока управления соединен с первыми входами четвертого и пятого элементов И,.первым, вторым, третьим и четвертым выходами блока управления являютсясоответственно выход второго .элемента задержки, выходы дешифратора, выход первого триггера и выход второго триггера являются соответственно первым, вторым, третьим и четвертым выходами блока управления , С и ТЗГ)- входы второго триггера соединены соответственно с выходом четвертогоэлемента И и первым, выходом дешифратора, ыход второго триггера подключен к первому входу шестого элемента И, второй

вход которого через третий элемент задержки подключен к выходу четвертого элемента И, выход шестого элемента И соединен с первь1ми входами элементов ИЛИ, вторые которых подключены к- выходу второго элемента И, второй вхдд которого объединен со вторам входом третьего элемента И и подключен к последнему выходу дешифратора, вторые входы четвертого и пятого элементов И

0 соединены с выходом первого элемента задержки, вход второго элемента задержки одключен к выходу первого элемента И, входы дешифратора подключены соответственно к

5 разрядным выходам счетчика, выход первого элемента ИЛИ соединен со счетным входом счетч-ика, вход установки нуля которого подключен к выходу третьего элемента И, входы

0 С и D первого триггера подключены соответственно к выходу пятого элемента И 1 к выходу третьего триггера, единичный вход которого подключен к выходу второго элемента ИЛИ, а нулевой - к выходу четвертого

5 элемента задержки, вход которого соединен с выходом пятого элемента И, выход первого триггера соединен со вторым входом первого элемента И,

Источники информации,

0 принятые во внимание при экспертизе

1. Авторское свидетельство СССР 444191, кл. G Об Р 15/34, 1972.

.2. Авторское, свидетельство СССР 206908, кл. G Об F 15/34, 1965

5 (прототип).

фф фУ . У

ф1/е./ fKlf iffiwjfef/ifjr От ff/fffxa /У

0fff.f ffff/fffjff vjf /ffyffjfy

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1981 |

|

SU1057954A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Вероятностный коррелометр | 1979 |

|

SU1023338A1 |

| Однородный спектро-коррелометр | 1981 |

|

SU970382A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Коррелометр | 1979 |

|

SU783799A1 |

| Вероятностный коррелометр | 1981 |

|

SU1049921A1 |

| Многоканальный многомерный цифровой коррелометр | 1985 |

|

SU1305714A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

Авторы

Даты

1981-06-30—Публикация

1979-08-13—Подача