Изобретение относится к цифровой измерительной технике, предназначено для вычисления корреляционных .функций при исследовании случайных процессов во временной области и может быть использовано, например, в системах технологического контроля, автоматического управления, диагностики и т.д.

Целью изобретения является повьше ние точности вычисления корреляционной функции при ограниченной длине выборки путем уменьшения методической погрешности нормирования.

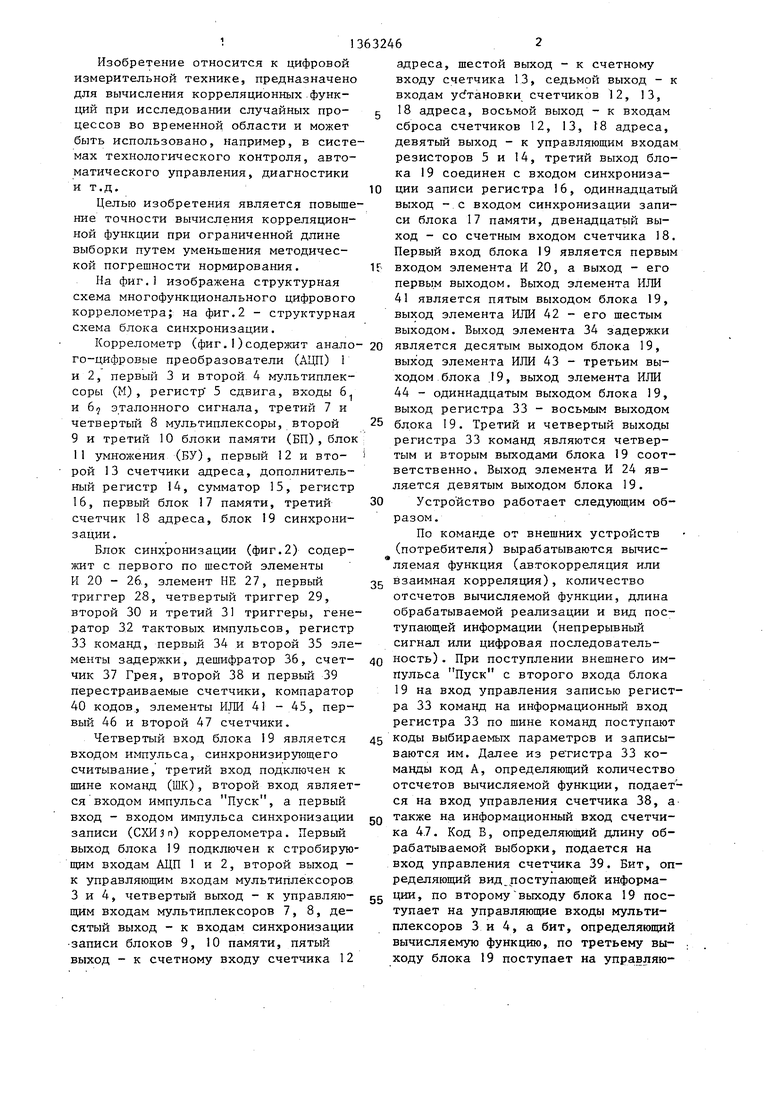

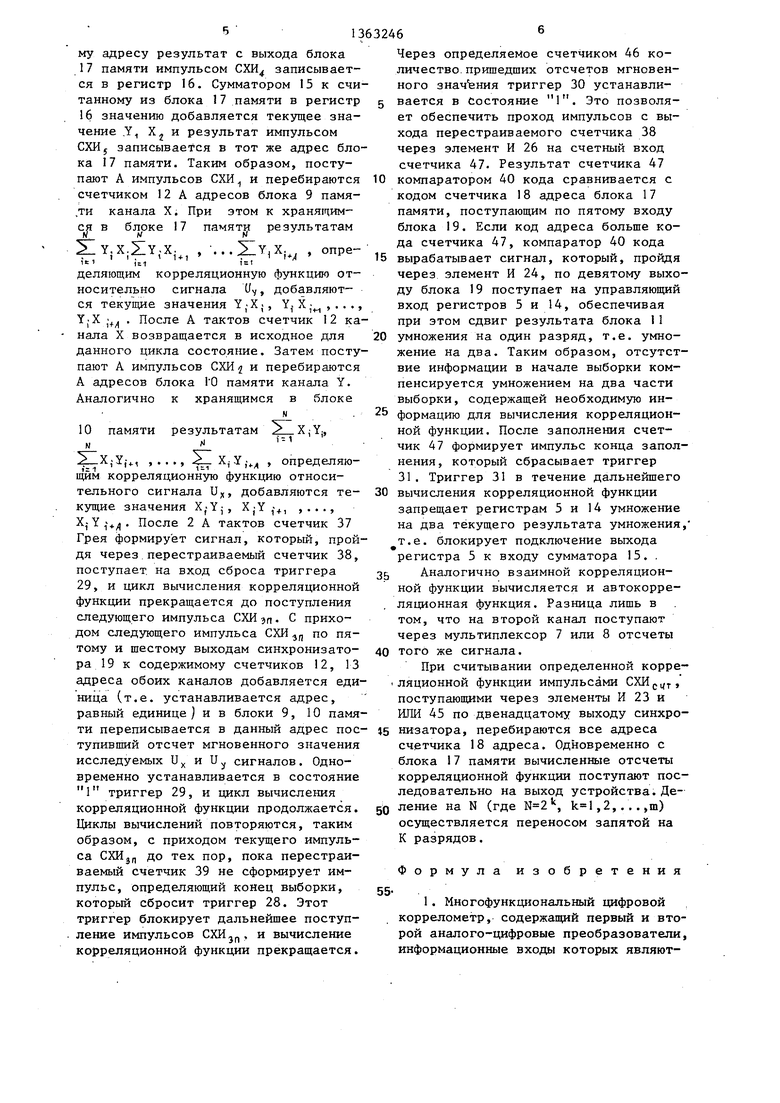

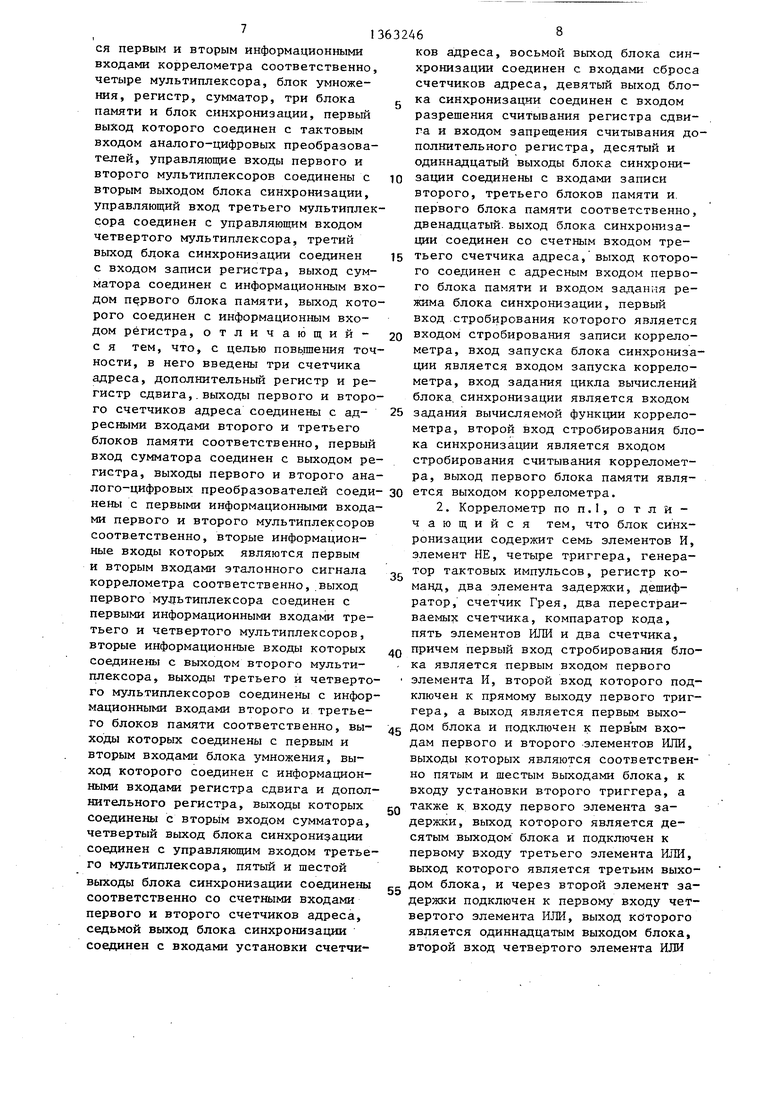

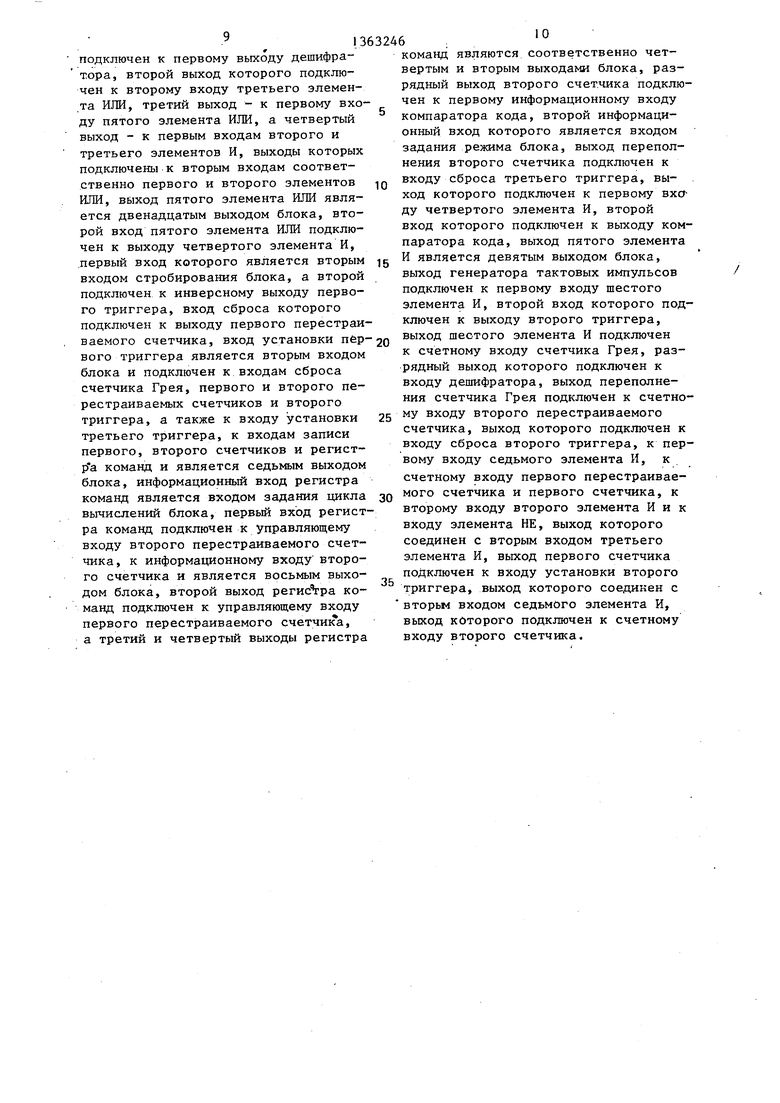

На фиг.1 изображена структурная схема многофункционального цифрового коррелометра; на фиг.2 - структурная схема блока синхронизации.

Коррелометр (фиг.1)содержит анало го-цифровые преобразователи (АЦП) 1 и 2, первый 3 и второй 4 мультиплексоры (М) , регистр 5 сдвига, входы 6 и 65 эталонного сигнала, третий 7 и четвертьш 8 мультиплексоры, второй 9 и третий 10 блоки памяти (БП), блок 11 умножения (БУ), первый 12 и второй 13 счетчики адреса, дополнительный регистр 14, сумматор 15, регистр 16, первый блок 17 памяти, третий

счетчик 18 адреса, блок 19 синхронизации.

Блок синхронизации (фиг.2) содержит с первого по шестой элементы И 20 - 26, элемент НЕ 27, первый триггер 28, четвертый триггер 29, второй 30 и третий 31 триггеры, генератор 32 тактовых импульсов, регистр 33 команд, первый 34 и второй 35 элементы задержки, дешифратор 36, счетчик 37 Грея, второй 38 и первый 39 перестраиваемые счетчики, компаратор 40 кодов., элементы ИЛИ 41 - 45, первый 46 и второй 47 счетчики.

Четвертый вход блока 19 является входом импульса, синхронизирзтощего считывание, третий вход подключен к шине команд (ШК), второй вход является входом импульса Пуск, а первый вход - входом импульса синхронизации записи (СХИзп) коррелометра. Первьш выход блока 19 подключен к стробирую- щим входам АЦП 1 и 2, второй выход - к управляющим входам мультиплексоров 3 и 4, четвертьш выход - к управляющим входам мультиплексоров 7, 8, десятый выход - к входам синхронизации записи блоков 9, 10 памяти, пятый выход - к счетному входу счетчика 12

f

0

5

0

адреса, шестой выход - к счетному входу счетчика 13, седьмой выход - к входам усГтановки счетчиков 12, 13,

18адреса, восьмой выход - к входам сброса счетчиков 12, 13, 18 адреса, девятый выход - к управляющим входам резисторов 5 и 14, третий выход блока I9 соединен с входом синхронизации записи регистра 16, одиннадцатый выход - с входом синхронизации записи блока 17 памяти, двенадцатый выход - со счетным входом счетчика 18. Первый вход блока 19 является первым входом элемента И 20, а выход - его первым выходом. Выход элемента ИЛИ 41 является пятым выходом блока 19, выход элемента ИЛИ 42 - его шестым выходом. Выход элемента 34 задержки является десятым выходом блока 19, выход элемента ИЛИ 43 - третьим выходом блока .19, выход элемента ИЛИ 44 - одиннадцатым выходом блока 19, выход регистра 33 - восьмым выходом блока 19. Третий и четвертый выходы регистра 33 команд являются четвертым и вторым выходами блока 19 соответственно. Выход элемента И 24 является девятым выходом блока 19.

Устройство работает следующим образом. .

По команде от внешних устройств (потребителя) вырабатываются вычисляемая функция (автокорреляция или g взаимная корреляция), количество отсчетов вычисляемой функции, длина обрабатываемой реализации и вид поступающей информации (непрерывный сигнал или цифровая последовательность) . При поступлении внешнего импульса Пуск с второго входа блока

19на вход управления записью регистра 33 команд на информационный вход регистра 33 по шине команд поступают коды выбираемых параметров и записываются им. Далее из регистра 33 команды код А, определяющий количество отсчетов вычисляемой функции, подается на вход управления счетчика 38, а также на информационный вход счетчика 4.7. Код В, определяющий длину обрабатываемой выборки, подается на вход управления счетчика 39. Бит, определяющий вид поступающей информации, по второму выходу блока 19 поступает на управляющие входы мультиплексоров 3 и 4, а бит, определяющий вычисляемую функцию, по третьему вы- ; ходу блока 19 поступает на управляю0

5

0

5

щие входы мультиплексоров 7 и 8. Импульсом Пуск устанавливаются в состояние 1 триггеры 28, 31, в состояние О - триггер 30 и осуществляется разрешение записи в счетчик 47 кода А из регистра 33 команд. Этим же импульсом в исходное состояние устанавливаются следующие блоки: счетчик 37 Грея, перестраиваемые счетчики 38, 39 и счетчик 46 устанавливаются в нулевое состояние; код, соответствующий нулю, записывается во всех ячейках блоков 9, 10 памяти каналов X и Y; устанавливаются в состояние 1 счетчики 12, 13 адреса каналов X и Y; записывается код, соответст- взтощий нулю, во всех ячейках блока 17 памяти; устанавливается в состояние нуля счетчик 18 адреса. После импульса Пуск по первому.входу блока 19 через элемент И 20 поступает импульс синхронизации записи (СХИ, который устанавливает в состоя1ше логической единицы триггер 29 и через первый выход блока 19 поступает на стробирующие входы аналого-цифровых преобразователей 1 и 2, с помощью которых непрерывные сигналы U и Uy одновременно преобразуются в их цифровые мгновенные значения.-Импульсом СХИзп добавляется единица через элементы ИЛИ 41, 42 к содержанию счетчиков 12, 13 адреса X и Y каналов. С задержкой, задаваемой элементом 34 задержки, импульс СХИ подается на входы синхронизации записи блоков 9, 10 памяти. Триггер 29 позволяет проход импульсов тактовой частоты, формируемых генератором 32 тактовых импульсов, через элемент И 25 на счетный вход счетчика 37 Грея. В течение одного цикла счетчика 37 Грея дешифратор 36 формирует четыре разнесенных во времени синхроимпульса. В течение 2 А циклов счетчика 37 Грея дешифратором 36 вырабатываются четыре независимые последовательности импульсов. Первая последовательность импульсов с первого выхода дешифратора 36 поступает на первые входы элементов И 21, 22 и делится посредством перестраиваемого счетчика 38 и элемента НЕ 27 на две разнесенные во времени и равные по длительности группы импульсов, которые через элементы И 21 и 22, элементы ИЛИ 41 и 42 по пятому и шестому выходам блока 19 поступают соответственно на входы счетчиков 12 и 13 адреса. Таким образом, в течение 2 А циклов счетчика 37 Грея на счетный вход g счетчика 12 адреса X канала по пятому выходу блока 19 поступает первая последовательность в А импульсов СХИ , а затем по шестому выходу блока 19 поступает вторая последователь0 ность в А импульсов СХИх на счетный вход счетчика 13 адреса канала Y.-Одновременно с группами импульсов СХИ и С.ХИ по двенадцатому, третьему и одиннадцатому выходам блока 19 про5 ходят последовательности .в 2 А импульсов СХИз, СХИ4, СХИ5 на счетный вход счетчика 18 адреса, на вход синхронизации записи регистра 16 и вход синхронизации записи блока 17 памяти

0 соответственно. Таким образом, цифровые отсчеты входных сигналов U, и и у, поступившие от аналого-цифровых преобразователей 1 и 2, или цифровые отсчеты, поступившие от внешнего за5 дающего устройства по шинам данных 6,, 6, импульсом СХИ эд записьшаются в адрес, равный нулю, блоков 9, 10 памяти обоих каналов. Далее отсчеты Х и Y, записанные в блоках,9t Ю

0 памяти обоих каналов, поступают на входы блока I1 умножения, а результат умножения поступает через регистры 5 и 14 на один вход сумматора 15, на другой вход сумматора 15 подается

с через регистр 16 код, записанный в нулевом адресе блока 17 памяти. При поступлении с третьего выхода блока 19 импульса СХИ 4, который является СХИ зд, прошедшим через элемент ИЛИ

0 43, в регистр 16 записывается код нулевого адреса блока 17. Затем полученная сумматором 15 сумма записывается в тот же нулевой адрес блока 17 памяти при поступлении с одиннадцато45 го выхода блока 19 импульса СХИ, который, является импульсом , прошедшим через элемент 35 задержки. После этого импульсом СХИ, поступающим по пятому выходу блока 19, к

0 содержанию счетчика 12 адреса канала X добавляется единица (устанавливается адрес, равный единице) и блоком 11 умножения перемножаются соответствующие адреса счетчиков 13, 12

g адреса Y и X каналов значения Y., Xj. Следующим импульсом СХИз, поступающим по двенадцатому выходу блока 19, прибавляется единица к содержанию счетчика 18 адреса; считанный по этому адресу результат с выхода блока 17 памяти импульсом СХИ записывается в регистр 16. Сумматором 15 к считанному из блока 17 памяти в регистр 16 значению добавляется текущее значение .Y, Х и результат импульсом CXHj записывается в тот же адрес блока 17 памяти. Таким образом, поступают А импульсов СХИ и перебираются счетчиком 12 А адресов блока 9 памя- ,ти канала X. При этом к хранящим- 17 памяти результатам

с в

блоке

и

памяти

N

Y.X;XY-X.

U1

опре U1

деляющим корреляционную функцию относительно сигнала (, добавляются текущие значения Y;Xj, Y,. Х;,..., Т;Х ; . После А тактов счетчик 12 канала X возвращается в исходное для данного цикла состояние. Затем поступают А импульсов СХИ2 и перебираются А адресов блока 10 памяти канала Y. Аналогично к хранящимся в блоке

N

10

ы

памяти результатам

.-X;Y,4, ,..., Л- XjY,v , определяющим корреляционную функцию относительного сигнала U, добавляются текущие значения X,.Yj , X;Y,- + , ,..., . После 2 А тактов счетчик 37 Грея формирует сигнал, который, пройдя через перестраиваемый счетчик 38,

поступает, на вход сброса триггера 29, и цикл вычисления корреляционной функции прекращается до поступления следующего импульса СХИзп- С приходом следующего импульса СХИ п по пятому и шестому выходам синхронизатора 19 к содержимому счетчиков 12, 13 адреса обоих каналов добавляется единица (т.е. устанавливается адрес, равный единице) и в блоки 9, 10 памяти переписывается в данный адрес поступивший отсчет мгновенного значения исследуемых U и U, сигналов. Одновременно устанавливается в состояние 1 триггер 29, и цикл вычисления корреляционной функции продолжается. Циклы вычислений повторяются, таким образом, с приходом текущего импульса СХИ,

ijn ДО тех пор, пока перестраиваемый счетчик 39 не сформирует импульс, определяющий конец выборки, который сбросит триггер 28. Этот триггер блокирует дальнейшее поступление импульсов СХИ, и вычисление корреляционной функции прекращается.

20

63246

Через определяемое счетчиком 46 количество, пришедших отсчетов мгновенного значения триггер 30 устанавли5 вается в Состояние 1. Это позволяет обеспечить проход импульсов с выхода перестраиваемого счетчика 38 через элемент И 26 на счетный вход счетчика 47. Результат счетчика 47

10 компаратором 40 кода сравнивается с кодом счетчика 18 адреса блока 17 памяти, поступающим по пятому входу блока 19. Если код адреса больше кода счетчика 47, компаратор 40 кода

15 вырабатывает сигнал, который, пройдя через элемент И 24, по девятому выходу блока 19 поступает на управляющий вход регистров 5 и 14, обеспечивая при этом сдвиг результата блока I1 умножения на один разряд, т.е. умножение на два. Таким образом, отсутствие информации в начале выборки компенсируется умножением на два части выборки, содержащей необходимую ин-

25 формацию для вычисления корреляционной функции. После заполнения счетчик 47 формирует импульс конца заполнения, который сбрасывает триггер 31. Триггер 31 в течение дальнейшего

30 вычисления корреляционной функции запрещает регистрам 5 и 14 умножение на два текущего результата умножения, т.е. блокирует подключение выхода регистра 5 к входу сумматора 15. .

35 Аналогично взаимной корреляционной функции вычисляется и автокорреляционная функция. Разница лишь в том, что на второй канал поступают через мультиплексор 7 или 8 отсчеты

40 того же сигнала.

При считывании определенной корре- ляционной функции импульсами поступающими через элементы И 23 к ИЛИ 45 по двенадцатому выходу синхро 5 низатора, перебираются все адреса счетчика 18 адреса. Одновременно с блока 17 памяти вычисленные отсчеты корреляционной функции поступают последовательно на выход устройства. Деление на N (где , ,2,...,m) осуществляется переносом запятой на К разрядов.

50

55Формула изобретения

1. Многофункциональный цифровой коррелометр, содержащий первый и второй аналого-цифровые преобразователи, информационные входы которых являют

ся первым и вторым информационными входами коррелометра соответственно, четыре мультиплексора, блок умножения, регистр, сумматор, три блока памяти и блок синхронизации, первый выход которого соединен с тактовым входом аналого-цифровых преобразователей, управляющие входы первого и второго мультиплексоров соединены с вторым выходом блока синхронизации, управляющий вход третьего мультиплексора соединен с управляющим входом четвертого мультиплексора, третий выход блока синхронизации соединен с входом записи регистра, выход сумматора соединен с информационным входом первого блока памяти, выход которого соединен с информационным входом регистра, отличающий- с я тем, что, с целью повышения точности, в него введены три счетчика адреса, дополнительный регистр и регистр сдвига,. выходы первого и второго счетчиков адреса соединены с адресными входами второго и третьего блоков памяти соответственно, первый вход сумматора соединен с выходом регистра, выходы первого и второго ана

лого-цифровых преобразователей соеди- ЗО ется выходом коррелометра.

нены с первыми информационными входами первого и второго мультиплексоров соответственно, вторые информационные входы которых являются первым и вторым входами эталонного сигнала коррелометра соответственно,.выход первого мультиплексора соединен с первыми информационными входами третьего и четвертого мультиплексоров, вторые информационные входы которых соединены с выходом второго мультиплексора, выходы третьего и четвертого мультиплексоров соединены с информационными входами второго и третьего блоков памяти соответственно, выходы которых соединены с первым и вторым входами блока умножения, выход которого соединен с информационными входами регистра сдвига и дополнительного регистра, выходы которых соединены с вторым входом сумматора, четвертый выход блока синхронизации соединен с управляющим входом третьего мультиплексора, пятый и шестой выходы блока синхронизации соединены соответственно со счетными входами первого и второго счетчиков адреса, седьмой выход блока синхронизации соединен с входами установки счетчи

5

0

ков адреса, восьмой выход блока синхронизации соединен с входами сброса счетчиков адреса, девятый выход блока синхронизации соединен с входом разрешения считывания регистра сдвига и входом запрещения считывания дополнительного регистра, десятый и одиннадцатый выходы блока синхронизации соединены с входами записи второго, третьего блоков памяти и. первого блока памяти соответственно, двенадцатый, выход блока синхронизации соединен со счетным входом третьего счетчика адреса, выход которого соединен с адресным входом первого блока памяти и входом задания режима блока синхронизации, первый вход стробирования которого является входом стробирования записи коррелометра, вход запуска блока синхронизации является входом запуска коррелометра, вход задания цикла вычислений блока, синхронизации является входом 5 задания вычисляемой функции коррелометра, второй вход стробирования блока синхронизации является входом стробирования считывания коррелометра, выход первого блока памяти явля5

0

2. Коррелометр по п.1, о т л и - чающийся тем, что блок синхронизации содержит семь элементов И, элемент НЕ, четыре триггера, генератор тактовых импульсов, регистр команд, два элемента задержки, дешифратор, счетчик Грея, два перестраиваемых счетчика, компаратор кода, пять элементов ИЛИ и два счетчика, причем первый вход стробирования бло- . ка является первым входом первого элемента И, второй вход которого подключен к прямому выходу первого триггера, а выход является первым выхо- g дом блока и подключен к перв ым входам первого и второго элементов ИЛИ, выходы которых являются соответственно пятым и шестым выходами блока, к входу установки второго триггера, а также к входу первого элемента задержки, выход которого является десятым выходом блока и подключен к первому входу третьего элемента ИЛИ, вьпсод которого является третьим выходом блока, и через второй элемент задержки подключен к первому входу четвертого элемента ИЛИ, выход которого является одиннадцатым выходом блока, второй вход четвертого элемента ИЛИ

0

5

подключен к первому выходу дешифратора, второй выход которого подключен к второму входу третьего элемента ИЛИ, третий выход - к первому входу пятого элемента ИЛИ, а четвертый выход - к первым входам второго и третьего элементов И, выходы которых подключены к вторым входам соответственно первого и второго элементов ИЛИ, выход пятого элемента ИЛИ является двенадцатым выходом блока, второй вход пятого элемента ИЛИ подключен к выходу четвертого элемента И, .первый вход которого является вторым входом стробирования блока, а второй подключен к инверсному выходу первого триггера, вход сброса которого подключен к выходу первого перестраи10

15

команд являются соответственно четвертым и вторым выходами блока, раз рядный выход второго счетчика подкл чен к первому информационному входу компаратора кода, второй информационный вход которого является входом задания режима блока, выход перепол нения второго счетчика подключен к входу сброса третьего триггера, выход которого подключен к первому вх ду четвертого элемента И, второй вход которого подключен к выходу ко паратора кода, выход пятого элемент И является девятым выходом блока, выход генератора тактовых импульсов подключен к первому входу шестого элемента И, второй вход которого по ключен к выходу второго триггера.

ваемого счетчика, вход установки пёр-20 шестого элемента И подключен

к счетному входу счетчика Грея, раз рядный выход которого подключен к входу дешифратора, выход переполнения счетчика Грея подключен к счетн му входу второго перестраиваемого счетчика, выход которого подключен входу сброса второго триггера, к пе вому входу седьмого элемента И, к счетному входу первого перестраивае мого счетчика и первого счетчика, к второму входу второго элемента Ин входу элемента НЕ, выход которого соединен с вторым входом третьего элемента И, выход первого счетчика подключен к входу установки второго триггера, выход которого соединен с вторьм входом седьмого элемента И, выход которого подключен к счетному входу второго счетчика.

вого триггера является вторым входом блока и подключен к входам сброса счетчика Грея, первого и второго перестраиваемых счетчиков и второго триггера, а также к входу установки третьего триггера, к входам записи первого, второго счетчиков и регист- команд и является седьмым выходом блока, информационный вход регистра команд является входом задания цикла вычислений блока, первый вход регистра команд подключен к управляющему входу второго перестраиваемого счетчика, к информационному входу второго счетчика и является восьмым выходом блока, второй выход регис гра команд подключен к управляющему входу первого перестраиваемого счетчика, а третий и четвертый выходы регистра

5

команд являются соответственно четвертым и вторым выходами блока, разрядный выход второго счетчика подключен к первому информационному входу компаратора кода, второй информационный вход которого является входом задания режима блока, выход переполнения второго счетчика подключен к входу сброса третьего триггера, выход которого подключен к первому входу четвертого элемента И, второй вход которого подключен к выходу компаратора кода, выход пятого элемента И является девятым выходом блока, выход генератора тактовых импульсов подключен к первому входу шестого элемента И, второй вход которого подключен к выходу второго триггера.

шестого элемента И подключен

к счетному входу счетчика Грея, разрядный выход которого подключен к входу дешифратора, выход переполнения счетчика Грея подключен к счетному входу второго перестраиваемого счетчика, выход которого подключен к входу сброса второго триггера, к первому входу седьмого элемента И, к счетному входу первого перестраиваемого счетчика и первого счетчика, к второму входу второго элемента Инк входу элемента НЕ, выход которого соединен с вторым входом третьего элемента И, выход первого счетчика подключен к входу установки второго триггера, выход которого соединен с вторьм входом седьмого элемента И, выход которого подключен к счетному входу второго счетчика.

fCXUtn

3 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Многоканальный многомерный цифровой коррелометр | 1985 |

|

SU1305714A1 |

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| Имитатор биосигналов | 1984 |

|

SU1289451A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Вероятностный коррелометр | 1981 |

|

SU1049921A1 |

Изобретение относится к цифровой измерительной технике, предназначено для вычисления корреляционных функций при исследовании случайных йроцессов во временной области и может быть использовано, например, в системах технологического контроля. автоматического управления, диагностики. Изобретение позволяет повысить точность вычисления корреляционной функции при ограниченной длине выборки путем уменьшения методической погрешности нормирования за счет увеличения до N 2 (N - объем выборки, k - любое число, кроме нуля) количества операций умножения - суммирования для каждого отсчета корреляционной функции с использованием при зтом повторения цифровых отсчетов исследуемого сигнала. Коррелометр содержит два аналого-цифровых преобразователя 1 и 2, четыре мультиплексора 3, 4, 7, 8, блок I1 умножения, регистр 16, сумматор 15, блоки 9, 10, .17 памяти, счетчики 12, 13, 18 адреса, регистр 5 сдвига, дополнительный регистр 14, блок 19 синхронизации. 1 3 . п. ф-лы, 2 ил. с (Л CMcfr Раг.1

Редактор А.Маковская

Составитель Е.Ефимова

Техред М.ДидыкКорректор М.Максимишинец.

Заказ 6364/42

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений -и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Многофункциональный цифровой коррелометр | 1979 |

|

SU826361A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-22—Подача