ных блоков соединены соответственн с пятым и шестым выходами блока управления, второй вход которого подключен к выходу блока фиксации среднего значения м®дуля,

2, Коррелометр по -дт, 1, отличающийся тем, что блок управления содержит генератор импульсов, формирователь двух непересекающихся последовательностей импульсов, делитель частоты, счетчик адреса, счетчик вывода, триггер цикла, триггер вывода/ триггер сброса памяти, группу элементов неравнозначности, элемент ИЛИ-НЕ, семь элементов И, элемент ИЛИ и элемент НЕ, причем выход генератора импульсов подключен к входу формирователя двух непересекаквдихся последовательностей импульсов, первый выход которого связан с. первым входом первого элемента И, а второй выход - с первым входом второго элемента И, счетнЕлм входом счетчика адреса и входом делителя частоты, подсоединенного свои выходом к единичному входу триггера цикла, единичный выход кото- , рого соединен с вторыми входами первого и второго элементов И, а нулевой выход - с входом сброса счетчика адреса, связанного выходом каждого разряда с первым входом соответствующего элемента группы элементов неравнозначности и с соответствующим входом элемента ИЛИ-НЕ, а выходом старшего разряда также с нулевым входом триггера цикла, единичным входом триггера

сброса памяти, первым входом седьмого элемента И и счетным входом счетчика вывода, под соединенного своим выходом переполнения к нулевму входу триггера сброса памяти и нулевому входу триггера вывода, единичный выход которого соединен с первым входом элемента ИЛИ, а нулевой выход - с вхбдом сброса счетчика вывода, вторыми входами всех элементов группы элементов не|равнозначности и вторым входом третьего элемента И, выход первого элемента И подключен к первьм входам четвертого и пятого элементов И, а также к четвертому выходу блока, выход второго элемента И связан с первыми входами третьего и шестого элементов И, единичный выход триггера сброса памяти подсоединен к второму входу четвертого элемента И, выход элемента ИЛИ-НЕ соединен с вторьвии входами пятого и шестого элементов И, третий вход четвертого .элемента И подключен к первому входу блока, с которым через элемент НЕ связаны также вторые входы седьмого элемента И и элемента ИЛИ, а к второму входу блока подсоединен единичный вход триггера вывода, выходы пятого, шестого и седьмого элементов И соединены соответственно с пятам первым и вторым выходами блока, выход элемента ИЛИ- с третьим выходом блока, а выходы всех элементов группы элементов неравнознаности и выходы третьего и четвертого элементов И образуют шестой выход блок.а,

| название | год | авторы | номер документа |

|---|---|---|---|

| Знаковый коррелометр | 1979 |

|

SU832564A1 |

| Вероятностный коррелометр | 1979 |

|

SU1023338A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Коррелометр | 1981 |

|

SU1057954A1 |

| Цифровой знаковый коррелометр | 1980 |

|

SU962975A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| Коррелометр | 1979 |

|

SU842830A1 |

1. КОРРЕЛС ЕТР, содержащий связанные через переключатель входных шин первую и вторую входные шины, блок сравнения, аналого-цифровой преобразователь, блок управления, блок начальной записи, блок фиксации среднего значения модуля и вычислительный блок, включакиций сдвиговый регистр задержки знака и сумматор, при этом первый,второй и третий информационные входы вычислительного блока связаны соответственно с выходом блока сравнения,знаковым выходом аналого-цифррвого преобразователя и его выходом модуля, подсоединенного также к информационному входу блока фиксации среднего значения модуля, первый выход блока управления соединен с управляющими входами блока сравнения и аналого-цйфрового преобра 3 ова тел я, вход и выход блока- начальной записи подключены соответственно к второму выходу и первому входу блока управления, третий выход которого связан с управляющим входом блока фиксации среднего значения модуля, а четвертый выход - с первьм управляюпцш входом вычислительного блока, которым является управляющий вход сдвигового регистра задержки знака, отличающийся тем, что, с целью упрощения коррелометра, в него введены/7Z- 1 дополнительных вычислительных блоков, каждый вычислительный блок содержит также коммутатор, элемент неравнозначности, преобразователь кода, блок памяти и регистр памяти, причем выход коммутатора подсоеди нен к последовательному входу сдвигового регистра задержки знака, последовательный выход которого соединен с одним из входов элемента неравнозначности и с вторым информационнь 4 входом коммутатора, подключенного своим первым i информационным входом к первомуинформационному входу вычислитель(Л ного блока, а управляющим входом к второму управлянщему входу вычислительного блока, второй и третий информационные входы которого связаны соответственно с вторым входом элемента неравнозначности и с информационным входом преобразователя кода, подсоединенного своим управляющим входом к выхо05 ду элемента неравнозначности, а выходом - к одному из входов сумматора, второй вход которого соединен с выходом регистра памяти, а выход - с информационным входом блока памяти, выход которого подключен к входу регистра памяти, а управляющий вход - к третьему управляющему входу вычислительного блока, первые управлякадие входы и вторые и третьи информационные входил всех вычислительных блоков включены параллельно, первый информационный вход каждого вычислительного блока, кроме первого, связан с последовательньлм выходом сдвигового регистра зещержки знака предьадущего вычислительного блока, а вторые и третьи управляющие входы всех вычислитель

Изобретение относится к специализированным средствам вычислительной техники, предназначенньвл для аппаратурного определения характеристик случайных процессор.

Известен многоканальный коррелометр типа значение - знак, содержащий аналого-цифровой njieoCpasoBaтель, блок сравнения, блок эЫделения модуля дискриминатор знака, блок задержки знака, логические блоки умножения и реверсивные счетчикн ,l .

Недостатком этого коррелсмлетра является отсутствие возможности получения прямой оценки нормированной корреляционной функции.

Известен также коррелометр, работанвций по алгоритму значение знак, содержащий аналого-цифровой преобразователь, группу элементов ИЛИ, блок сравнения, блок управления ,сумматоры, блок фиксации среднего

значения модуля, блок задержки знака и блок перемножения знака 2.

Недостатком этого коррелометра является низкое йлстродействие, обусловленное последовательным

ислением ординат корреляционной функцид в

Наиболее близким к изобретению по технической сущности и достигаемому результату является коррелометр, содержащий связанные через переключатель входных шин первую и вторую входные шины, блок сравнения, аналого-цифровой преобразователь, блок управления, блок началь;

ной записи, блок фиксации среднего значения модуля и вычислительный блок, включающий сдвиговый регистр задержки знака и 3J.

Недостаток этого коррелометра заключается в больших аппаратурных затратах, так как каждый из каналов вычисления, число которых равно числу ординат корреляционной фуикдии, содержит накапливакщий cy мaтop и дополнительную аппаратуру.

Целью изобретения является упрощение коррел м4етрд 9 . Поставленная цель достигается тем, что в коррелометр, содержащий связанные через переключатель входных initH первую и вторую входные шины, блок сравнения, аналого-цифровой преобразователь, блок управления, блок начальной записи, блок фиксаций среднего значения модуля и вычислительный блок, включающий сдвиговый регистр задержки знака И сумматор, при этом первый, второ и третий информационные входы вычислительного блока связаны соответственно с выходом блока сравнения, знаков выходом аналого-цифрового преобразователя и его выходом модуля, подсоединенного также к информационному входу блока фиксации среднего значения модуля, Ьервый выход блока управления соединен с управлякяцими входами .блока сравнения и аналого-цифрового преобразователя, вход и выход блока начальной записи подключены соответственно к второму выходу и первому входу блока управления, третий выход которого связан с управляющим входом блока фиксации среднего значения модуля, а четвертый выход - с первым управляющим входом вычислительного блока, которым является управляющий вход сдвигового регистра задержки знака, введены m-l дополнительных вычислительных блоков , каждый вычислительный блок содержит также коммутатор, элемент неравнозначности, преобразователь кода, блок памяти и регистр памяти, причем выход коммутатора подсоединен к последовательному входу сдвигового регистра задержки знака, последовательный выход которого соединен с одним из входов элемента неравнозначност и с вторым информационньм входом коммутатора, подключенного своим первьм информационным входе к первому входу вычислительного блока, а управляющим входом - к второму управляющему входу вычислительного блока, второй и третий информационные входы которого связаны соостветственно с вторьм входом элемента неравнозначности и с инфомационным входом преобразователя кода, подсоединенного своим управляющим входом к выходу элемента неравнозначности, а выходом к однсму из входов сумматора, вто5 рой вход j OTOporo соединен с выходом регистра памяти, а выход - с информационным входом блока памяти, выход которого подключен к входу регистра памяти, а управляющий вход 0 к третьему управлякяцему входу вы числительного блока, первые управляющие входы и вторые и третьи информационные входы всех вычислительных блоков включены параллельно, первый

5 информационный вход каждого вычисли-тельного блока, кроме первого, связан с последовательным выходом сдвигового регистра задержки знака предыдущего вычислительного блока,

Q а вторые и третьи управляющие входы всех, вычислительных блоков соединены соответственно с пятьи и шест1Л « выходами блока управления, второй вход которого подключен к

5 выходу блока фиксации среднего значения модудЯс

При этом входяогий в состав коррелометра блок управления содержит генератор импульсов, формирователь двух непересекающихся последова-

0 тельностей импульсов, делитель частоты, счетчик Адреса, счетчик вывода, триггер цикла, триггер вывода, триггер сброса памяти, группу элементов неравнозначности, элемент

5 ИЛИ-НЕ, семь элементов И, элемент ИЛИ и элемент НЕ, причем выход генератора импульсов подключен к входу формирователя двух непересекающихся последовательностей импульсов,0 первый выход которого связан с первьм входом первого элемента И, а второй выход - с первьм входом второго элемента И, счетньм входом счетчика адреса и входом делителя

5 частоты, подсоединенного своим выходом к единичнс(у входу триггера Ш1кла, единичный выход которого соединен с вторыми входами первого и второго эл@«1ентов И, а -нулевой

Q выход - с входом сброса счетчика адреса, связанного выходом каждого разряда с первым входом соответствующего элемента группы элементов неравнозначности и с соответJ ствующим входом элемента ИПИ-НЕ, а выходом старшего разряда - также с нулевым входом триггера цикла, единичным входом триггера сброса памяти, первьм входом седьмого эле мента И и счетнкш вхоДом счетчика

О вывода, подсоединенного своим выходом переполнения к нулевому входу триггера сброса памяти и нулевому входу триггера вывода, единичный выход которого соединен с

5 первьм входсм элемента ИЛИ, а нулевой выход - с входом сброса счетчика.вьгоода, вторыми входами всех элементов группы элементов неравнозначности и вторым входом4 третьего элемента И, выход первогоэлемета И подключен к первым входам четвертого и пятого элементов И, а также к четвертому выходу блока, выход второго элемента И связан с первыми входами третьего и шестого элементов И, единичный выход триггера сброса памяти подсоединен к второму входу четвертого элемента И, выход элемента ИЛИ-НЕ соединен с вторыми входами пятого и шестого элементов И, третий вход четвертого элемента И подключен к перёому входу блока, с которым через элемент НЕ связаны также вторые входы седьмого элемента И и элемента ИЛИ, а к второму входу блока подсоединен единичный вход триггера вывода, выходы пятого, шестого и седьмого элементов И соединены соответственно с пятым, первым и вторым выходами блока, выход элемента ИЛИ - с третьим выходом блока, а выходы всех элементов группы элементов неравнозначности и выходы третьего и четвертого элементов И образуют шестой выход блока,

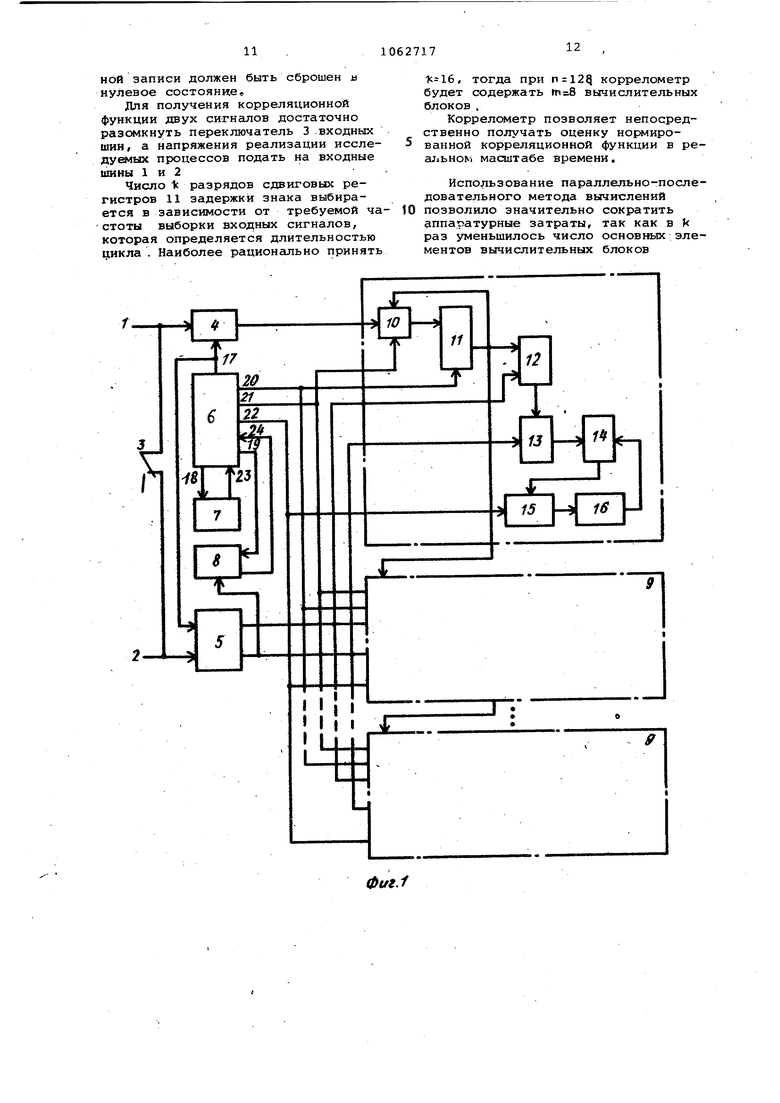

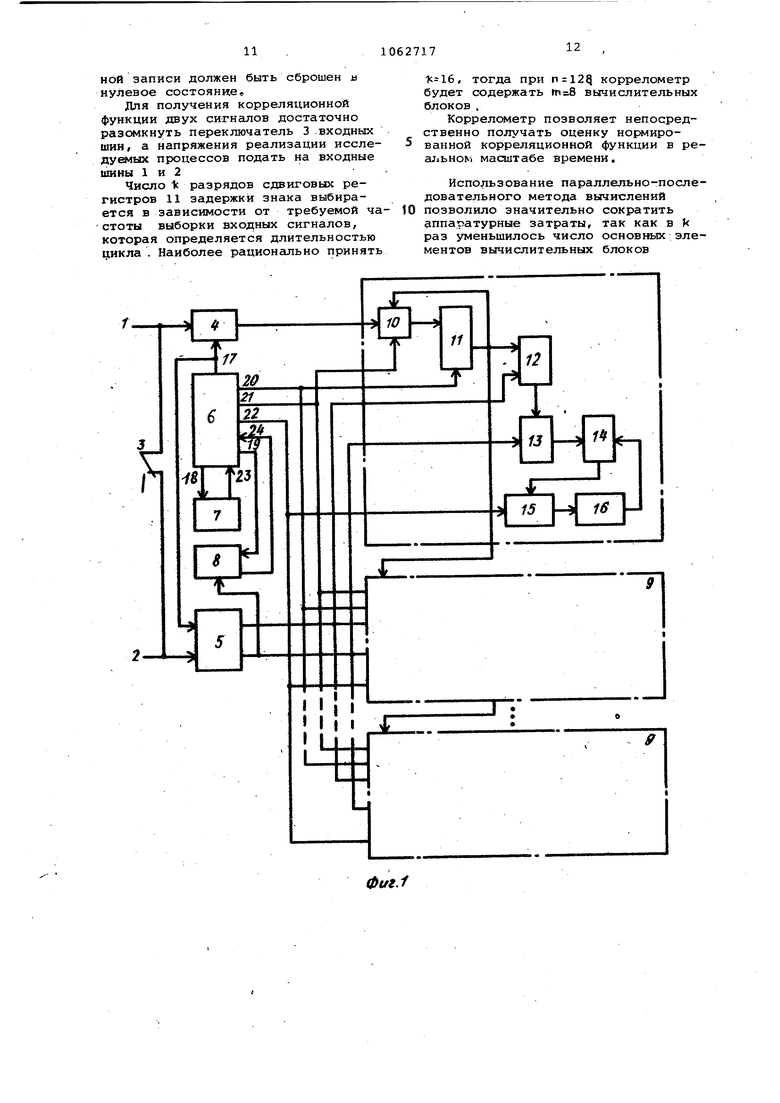

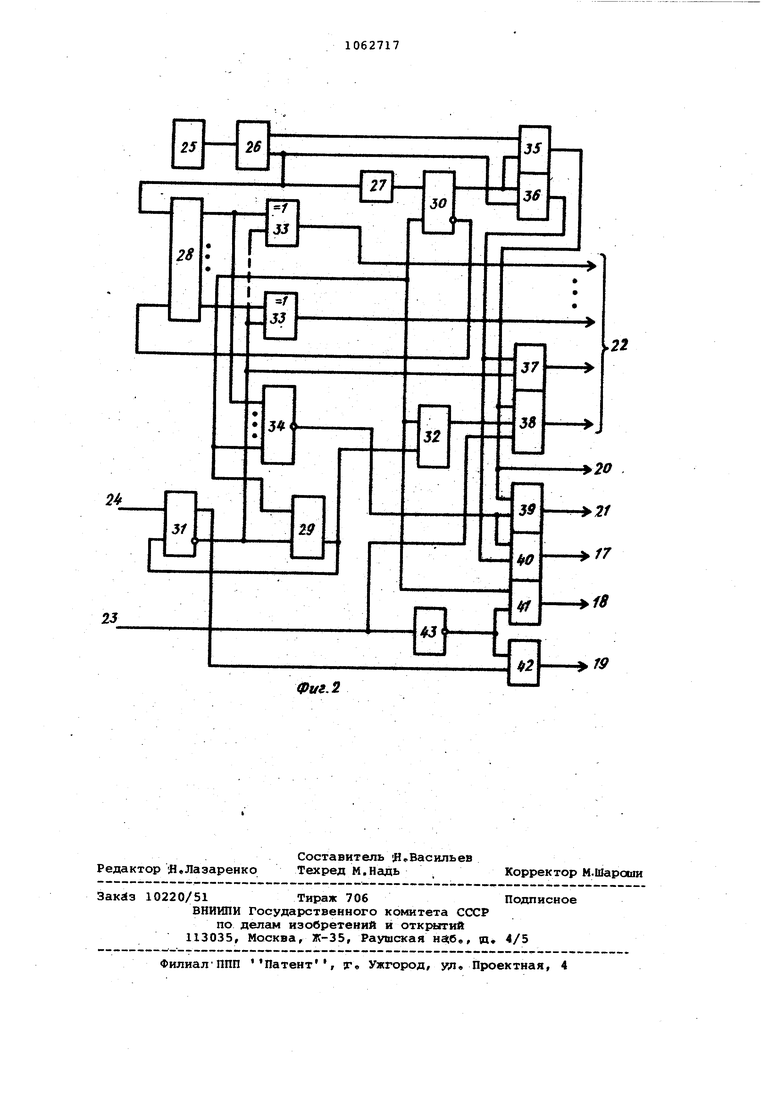

На фи.г, 1 приведена структурная схема коррелометра; на фиг. 2 функциональная схема блока управления .

Коррелометр содержит первую и вторую входные шины 1 и 2, переключатель 3 входных шин 1 и 2, блок 4 сравнения, аналого-цифровой преобразователь 5, блок б управления, блок 7 начальной записи, блок 8 фиксации среднего значения модуля и вычислительные блоки 9, каждый из которых содержит коммутатор 10, сдвиговый регистр 11 задержки знака, элемент 12 неравнозначности, преобразователь 13 кода, сумматор 14, блок 15 памяти и ре гистр 16 памятл. Блок 6 управления имеет первый 17, вторюй 18, третий 19, четвертый 20, пятый 21 и шестой 22 выходы, а также первый 23 и второй 24 входы,

В состав блока 6 управления (фиг 2) входят генератор 25 им. пульсов, формирователь 6 двух непересекающихся последовательностей импульсов, делитель 27 частоты, счетчик 28 адреса, счетчик 29 вывода, триггер 30 цикла, триггер 31 вывода, триггер 32 сброса памяти, группа элементов 33 неравнозначности, элемент ИЛИ-НЕ 34, первый 35, второй 36, третий 37, четвертый 38, пятый 39, шестой 40 и седьмой 41 элементы И, элемент ИЛИ 42 и элемент НЕ 43

Работа устройства осуществляется по алгоритму вычисления оценки корреляционной функции

а Г.., «

)

( ,

j

е « to {itn-tfJ4t ;

5 - ig - момент начала измерения корреляционной функции; At - интервал следования выборок

сигналов;

j - номер ординаты корреляцион0 ной функции;

п- ойцее количество ординат; x(il- центрированная реализация

исследуемого процесса; N - общее число выборок

Число выборок N задается таким образом, что выполняется условие , где f- целое число. Это условие реализуется с помощью

блока 8 фиксации среднего значения

модуля, поэтому р (}&i} - а 10 а прибор является прямопоказывающим.

Коррелометр в режиме измерения автокорреляционной функции (пере5 ключатель 3 входных шин замкнут) работает следующим образом,,

Напряжение центрированной реализации (t1 с входной шины 1 (или 2) поступает на информационный вход

0 блока 4 сравнения и на вход аналого-цифрового преобразователя 5 через переключатель 3 Импульс выборки входного сигнала с первого выхода 1,7 блока 6 управления пода5 ется на управляющие входы блока 4 сравнения и аналого-цифрового преобразователя 5.

В блоке 4 сравнения в момент появления импульса .выборки осущестQ вляется -сравнение напряжения входного исгнала с нулевым урвнем При положительном результате сравнения на выходе блока 4 сравнения возникает потенциал, соответст вующий логической единице, который подается на первый информационный вход коммутатора 10 первого вычислительного блока 9.

В аналого-цифровом преобразователе 5, который запускается им0 пульсом с выхода 17 блока 6 управле ния, напряжение входного сигнала преобразуется в двоичное число п-. Знак числа поступает на второй вход элементов 12 неравнозначности

5 вычислительных блоков 9, а модуль числа в прямом параллельном коде подается на информационный вход бл ка 8 фиксации среднего значения модуля, который может быть выполнен в виде накапливающего сумматора, и на информационные входы преобразователей 13 кода вычислительных блоков 9. На управляющий вход преобразователя 13 кода, выполненного, например, в виде группы элементов неравнозначности, поступает потенциал с выхода элемента 12 неравнозначности. Каждаай цикл вычислений содержит k тактов ( 1( - число разрядов сдвигового регистра 11 задержки знака) В каждом такте на управляки вход сдвиговых регистров 11 задержки знака подается импульс сдвига с четвертого выхода 20 блока 6 управления. По этому импульсу прои ходит сдвиг- информации в регистрах 11 задержки знака. Во время прихода первого тактового импульса каждо го цикла вычислений на управляющий вход коммутатора 10 приходит импульс записи знака с пятого выхо4 да 21 блока 6 управления, Поэтому в первом такте в первый разряд сдви гового регистра 11 задержки знака первого вьмислительного блока 9 через коммутатор 10 запишется результат сравнения напряжения входного Сигнала с нулевым уровнем с выхода блока 4 сравнения, В первый разряд сдвигового регистра 11 за держки знака {i+l)-ro вычислительн о блока 9 через коммутатор 10 этого блока в первом такте запишется зна чение знака с выхода старшего k-го ,разряда сдвигового регистра 11 задержки знака i-го вычислительного блока 9. Одновременно на управляющие входы блоков 15 памяти вычисл тельных блоков 9 с шестого выхода 22 блока б управления подается импульс считывания и адресЛ-й ячейки памяти, с которой информация через регистр 16 памяти подается на вторые входы разрядов сумматора 14, На первые входы разрядов су матора 14 с выходов преобразователя 13 кода поступает текущее j-e значение произведения fj , ко торое представляет собой число h.j в прямом или коде в зависимости от произведения знаков 8, г- Произведение знаков получается ka выходе элемента 12 неравнозн ности, который управляет работой п образователя 13 кода При совпаде НИИ знаков преобразователе 13 кода выдает в сумматор 14 число bj в пря мом коде, а при несовпадении - в обратном, Результат суммирования с выходов разрядов сумматора 14 заносится в ту же 1с-ю ячейку блока 15 памяти при наличии импульра записи на шестом выходе 22 блока б управления. , Во втором такте цикла вычисления в первый разряд сдвигового регистра 11 задержки знака через коммутатор 10 записывается значение знака с выхода- старшего -го разряда этого же регистра, а в разряд поступает значение знака из (1t-l)-ro разряда На управляющие входы блоков 15 памяти с шестого выхода 22 блока б управления подается адрес (К-1)-й ячейки памяти и производится суммирование предыдущего значения суммы с очередным произведением модуля на произведение знаков и запись текущей оценки очередной ординаты корреляционной функции в (1-1)-ю ячейку блока 15 памяти. Длительность такта определяется временем обращения к памяти и суммирования сч Х зс(пТаким образом за вреМя одного цикла в m вычислительных блоках 9 вычисляются текущие значения оценок п т.1 ординат корреляционной функции . За это время в аналого-цифровом ni eo6разователе 5 образуется число lijn соответствующее новой выборке входного сигнала , Работа коррелометра синхронизируется импульсами бдока 6 управ,ления (фкг,2) Генератор 25 импульсов генерирует тактовые импульсы, из которых формирователь 26 двух непере сек акяцнхся последовательностей импульсов вырабатывает два сдвинутых во времени импульса TJ, и Т. Так как период выборки (длительность дискретного шага задержки at ) входных сигналов может быть больше длительности цикла вычисления корреляционной функции, то импульсы т и Ti проходят через элементы И 35 и 36 только при наличии разрешающего потенциала- на прямом выходе триггера 30 цикла, который устанавливается в еди1ничное состояние импульсом Tg с выхода делителя 27 частоты с частотой выборки входного сигнала, а в нулевое состояние сбрасывается импульсом с выхода старшего It-го разряда счетчика 28 адреса, который в каждом цикле выдает такт за тактом через группу элементов 33 неравнозначности на шестой выход 22 блока 6 управления адрес ячейки памяти блоков 15 памяти вычислительных блоков 9 коррелометраС выходов третьего и четвертого элементов И 37 и 38 в блоки 15 вычислительных блоков 9 коррелометра поступают управляющие сигналы соответственно записи и считывания информации. Одновременно с четвертого выхода 20 блока б управления на сдвиговые регистры 11 задержки знака поступают управляющие импульсы Т, являющиеся импувьсами сдвига., В первом такте каждого цикла, когда все разряды счетчика 28 адреса находятся в нулевом состоянии, с выхода элемен-. та ИЛИ-НВ 34 снимается единичный потенциал, который разрешает передачу на первый 17 и пятый 21 выходы блока 6 управления управляющих импульсов Т и Т, с выходов пер вого и второго элементов И 35, и 36 через пятый и шестой элементы И 39 и 40 Управляющие импульсы Т H Ti:поступают соответственно на коммутатор 10 и на объединенные управляющие входи блока 4 сравнения и аналого-цифрового преобразователя 5 , .

:Длительность цикла задается счетчиком 28 адреса, на счетный вход которого поступают управляющие импульсы Tg. с соответствующего выхода формирователя 26.. По окончании цикла импульс с выхода старшего разряда счетчика 28 адреса перебрасывает триггер 30 цикла в нулевое состояние, а потенциал с нулевого выхода этого триггера запрещает работу счетчика 28 адреса до приход следующего импульса с выхода делителя 27 частоты на единичный вход триггера 30 цикла.

Количество циклов вычисления определяется блоком 8 фиксации среднего значения модуля, который суммирует поступающие значения модуля числа ti: в каждом цикле вычисления оценки корреляционной функции При переполнении блока 8 фиксации среднего значения модуля, которое наступает при ЪrloT, с его выхода на второй вход 24 блока 6 управлени поступает илшульс Этот импульс устнавливает в елиничное состояние триггер 31 вывода, с прямого выхода которого через элемент ИЛИ 42 на тртий выход 19 блока 6 управления подается сигнал сброса блока В фиксации среднего значения модуля.. Hek вторые входы группы элементов 33 неравнозначности поступает нулевой потенциал с нулевого выхода триггера 31 вывода, в результате чего на шестой выход 22 блока 6 управления будут переданы в прямом коде адреса ячеек блоков 15 памяти вычислите ных блоков 9. Одновременно начинает работать счетчик 29 вывода, которъОИ определяет длительность режима вывода кор1&елометр а,

В этом режиме работа коррелометра аналогична работе его в режиме вычисления оценок корреляционной функций, только на выход 22 блока 6 управления, и, соответственно, в блоки 15 памяти не передются через третий элемент И 37 .импульсы записи. Длительность составляет ri тактсда.

По окончании режима вывода сигнал с выхода старшего разряда счетчика 29 вывода устанавливает в нулевое состояние триггер 31 вывода и триггер 32 сброса памятл. Коррелометр начинает работать в режиме вычисления новых оценок корреляционной функции

Для стирания предыдущих значений оценок из ячеек блоков 15 памяти вычислительных блоков 9 в течени первого цикла работы коррелометра в блоки 15 памяти не передаются импульсы считывания через четвертый элемент И 38, так как триггер 32 сброса памяти находится в нулевом состоянии. Этот триггер переводится в единичное состояние импульсом с выхода старшего разряда счетчика 28 адреска. Таким образсзм, на вторые входы сумматоров 14 в первом цикле плступает нулевая информация с блоков 15 Псцляти через регист 16 памяти, .

Для исключения ошибки, вызванной постепенным заполнением сдвиговых регистров 11 задержки знака, в начале работы коррелометра устанавливается в нулевое состояние блок 7 начальной запиои, С выхода этого блока на первый вход 23 блока 6 управления поступает нулевой потенциал, который запрещает прохождение импульсов считывания на шестой выход 22 блока 6 управления через элемент И 3:8, Этот же сигнал, инвертированный элементом НЕ 43, поступает на третий выход 19 блока 6. управления и запрещает работу блока 8 фиксации среднего значения модуля, а также разрешает прохождение сигналов со старшего разряда счетчика 2 8 адреса на второй выход 18 блока I6 управления через седьмой И 4.1, Сигналы с второго выхода 18 блока 6 управления поступают на вход блока 7 начальной записи. После п циклов все разряды всех регисров 11 задержки знака будут содержать значения знаков исследуемой; реализации, В начале (п+1)-го цикла вычисления снимается зашреп аюций сигнал с первого входа 23 блока 6 управления, и коррелсметр начинает вычисление оценки корреляционной функции

По окончании режима вывода, если реализация входшого сигнала остается прежней, первый цикл вычисления аналогичен (п+1)-му циклу начала работы ко1 елсметр а. Вели же на входы коррелометра подана новая реализация, то блок 7 начальНОЙ записи должен быть сброшен и нулевое состояние.

Для получения корреляционной функции двух сигналов достаточно разомкнуть переключатель 3 .входных шин, а напряжения реализации исследуемых процессов подать на входные шины 1 и 2

Число 1с разрядов сдвиговых регистров 11 задержки знака выбирается в зависимости от требуемой частоты выборки входных сигналов, которая определяется длительностью цикла . Наиболее рационально принять

И-16, тогда при коррелометр будет содержать вычислительных блоков .

Коррелометр позволяет непосредственно получать оценку нормированной корреляционной функции в реajibHONi масштабе времени.

Использование параллельно-последовательного метода вычислений позволило значительно сократить аппаратурные затраты, так как в раз уменьшилось число основных элементов вычислительных блоков

Фuг.f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М., Энергия, 1974, с.138 2 | |||

| 1972 |

|

SU422010A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-12-23—Публикация

1980-09-19—Подача