(54) ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО С АНАЛОГОВОЙ ПАМЯТЬЮ

соединен к управляющему входу четвертого ключа, а инверсный выход через второй ждущий мультивибратор управляющему входу пятого ключа, выход которого подсоединен ко входу считывания магнитного аналогового регул.ируюцего и запоминающего блока, выход логического элемента ИЛИ, входами подключенного ко входу устройства, соединен со входом расширителя импульсов, прямой выход которого подсоединен к управляющим входам первого и третьего ключей, а инверсный выход - к управляющему входу второго ключа.

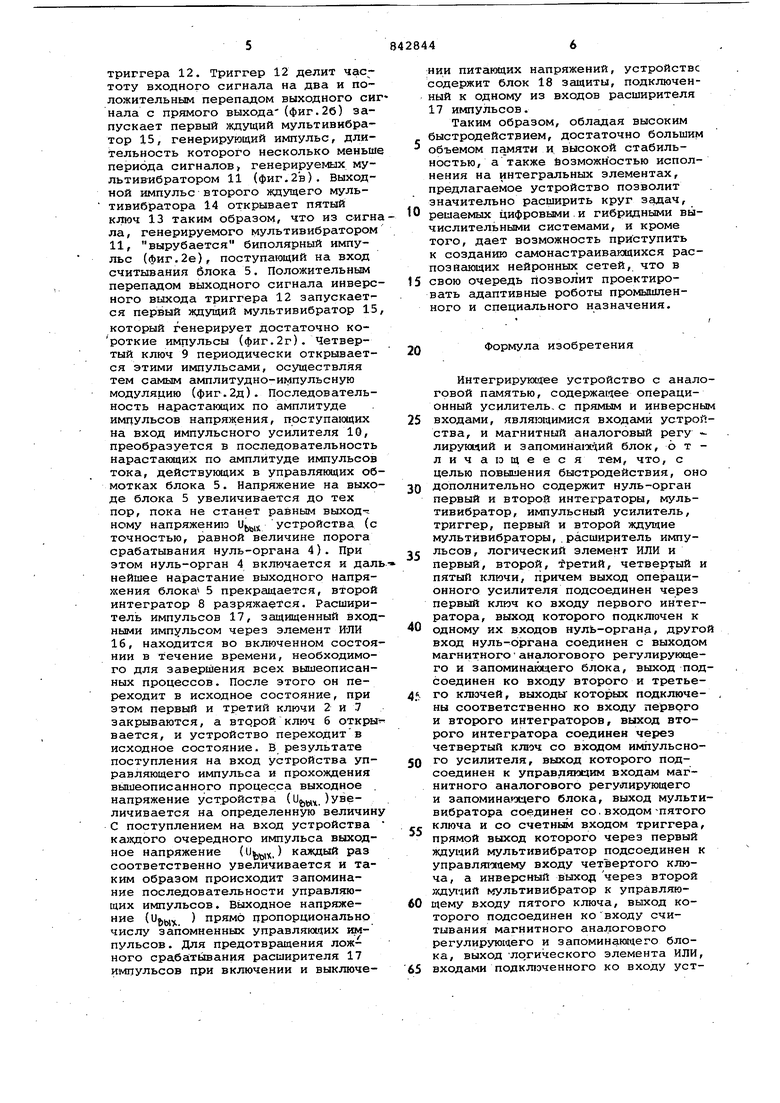

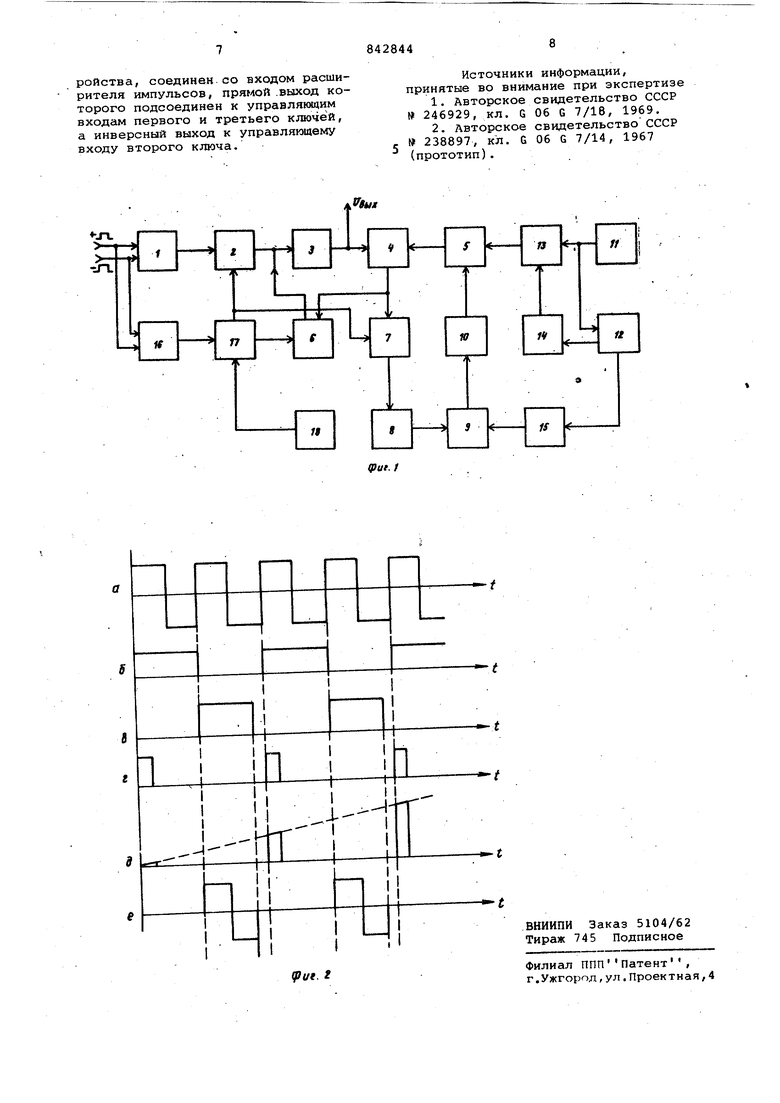

На фиг.1 изображена блок-схема предлагаемого устройства, фиг.2, иллюстрирует временное разделение процессов записи и считывания с магнитного аналогового регулирующего и запоминающего блока.

Устройство содержит операционный усилитель 1 с прямым и инверсныгл входами, соединенный через первый ключ 2 со входом первого интегратора 3, выход которого подсоедине к одному из входов нуль-органа 4 и одновременно является выходом интегрирующего устройства с аналоговой памятью. На другой вход нульоргана 4 подается сигнал с магнитного аналогового регулирующего и запоминающего блока 5, выход нульоргана 4 через второй ключ б соединен со входом первого интегратора 3 и через третий ключ 7 со входом второго интегратора 8. Выход второго интегратора 8 через четвертый ключ 9 и импульсный усилитель 10 подсоединен к управляющим входам блка 5. Для разделения во времени процессов записи и считывания с блока 5 в устройстве используется мультивибратор 11, выход которого соединен со счетным входом триггера 12 и через пятый ключ 13 со входом считывания блока 5. Сигнал с инверсного выхода триггера 12 запускает второй ждущий, мультивибратор 14, с помощью которогоосуществляется управление пятым ключом 13. Сигнал с прямого выхода триггера 12 запускает первый ждущий мультивибратор 15, управляющий четвертым ключом 9. Импульсы управления, поступающие на прямой и инверсный вхо-. ды операционного усилителя 1, подаются на вход логического элемента ИЛИ 16, с выхода которого осуществляется запуск схемы расширителя импульсов 17. Инверсный выход расширителя импульсов 17 управляет вторым ключом 6, а прямой выход первым и третьим ключами 2 и 7. В устройстве используется, схема 18 защиты, подключенная к расширителю 17 импульсов. Предлагаемое устройство полностью реализуется на интегральных элементах за исключением навесных деталей-конденсаторов и ячейки памяти блока 5.

Устройство работает следующим образом.

В исходном состоянии (при отсут- ствии сигналов на прямом и инверсном входах операционного усилителя 1 на инверсном выходе расширителя 17 импульсов имеется отрицательное напряжение, а на прямом - положительное так,.что первый и третий ключи

2 и 7 закрыты, а второй ключ 6 открыт, при этом выход нуль-органа 4 оказывается подключенным через второй ключ 6 ко входу первого интегратора 3. На один из входов нуль-орга5 на 4 поступает напряжение с первого интегратора 3/ а на другой напряжение, записанное в блоке 5 При этом первый интегратор 3 оказывается включенным в цепь следящей обратной связи таким образом, что на его выходе поддерживается напряжение, равное напряжению, снимаемого с выхода блока 5 с точностью, равной величине порога

5 срабатывания нуль-органа 4.

При поступлении на прямой вход операционного усилителя 1 управлякяцего импульса последний усиливается. Одновременно этот же импульс

Q через логический элемент ИЛИ 16

запускает расширитель 17 импульсов. При этом знаки напряжений на выходах расширителя импульсов 17 изменяются, первый и третий ключи 2

и 7 открываются, а второй ключ 6 закрывается, причем выход операционного усилителя 1 оказывается подключенным через первый ключ 2 ко входу первого интегратора 3, а выход нуль-органа 4 через третий

0 ключ 7 оказывается подсоединенным ко входу второго интегратора 8. Первый интегратор 3 интегрирует поступивший на его вход с выхо-. да операционного усилителя 1 импульс, и напряжение на его выходе и на выходе всего устройства ( ) увеличивается. Возникшая на входах нуль-органа 4 разность напряжений приводит кего срабатывап нию (если величина этого рассогласования превышает напряжение порога нуль-органа 4) и на выходе нульоргана 4 появляется достаточно высокое напряжение того или иного знака в зависимости от знака напряжения рассогласования. Выходное напряжение нуль-органа 4 интегрируется вторым интегратором 8 и через четвертый ключ 9 постугГает на импульсный усилитель 10 и затем на упО равляющие входы блока 5. Временное разделение процессов записи и считывания с блока 5 осуществляется следующим образом: мультивибратор 11 генерирует меаЕ1др (Лиг.2а), который поступает на счетн.1й вход

триггера 12. Триггер 12 делит частоту входного сигнала на два и положительным перепадом выходного си нала с прямого выхода (фиг.26) запускает первый ждущий мультивибратор 15, генерирующий импульс, длительность которого несколько меньш периода сигналов, генерируемых мультивибратором 11 (фиг.2в). Выходной импульс второго идцущего мультивибратора 14 открывает пятый ключ 13 таким образом, что из с-игнла, генерируемого мультивибратором 11, вырубается биполярный импульс (фиг.2е), поступающий на вход считывания блока 5. Положительным перепадом выходного сигнала инверсного выхода триггера 12 запускает ся первый ждущий мультивибратор 15

который генерирует достаточно короткие импульсы (фиг.2г). Четвертый ключ 9 периодически открывается этими импульсами, осуществляя тем самым амплитудно-иг.1пулъсную модуляцию (фиг.2д). Последовательность нарастающих по амплитуде имцульсов напряжения, поступающих на вход импульсного усилителя 10, преобразуется в последовательность нарастающих по амплитуде импульсов тока, действующих в управлякяцих обмотках блока 5. Напряжение на выходе блока 5 увеличивается до тех пор, пока не станет равным выход ному напряжению и, устройства (с точностью, равной величине порога срабатывания нуль-органа 4). При этом нуль-орган 4 включается и дал нейшее нарастание выходного напряжения блока 5 прекращается, второй интегратор 8 разряжается. Расширитель импульсов 17, защищенный входными импульсом через элемент ИЛИ 16, находится во включенном состоянии в т ечение времени, необходимого для завершения всех вышеописанных процессов. После этого он переходит в исходное состояние, при этом первый и третий ключи 2 и 7 закрываются, а втррой ключ б откры вается, и устройство переходитв исходное состояние. В результате поступления на вход устройства управляющего импульса и прохождения вышеописанного процесса выходное напряжение устройства (Ujj.. ) увеличивается на определенную величину С поступлением на вход устройства каждого очередного импульса выходное напряжение (.) каждый раз соответственно увеличивается и таким образом происходит запоминание последовательности управляющих импульсов. Выходное напряжение ( ) прямо цропорционально числу запомненных управляющих 1Шпульсов. Для предотвращения ложного сраба;тьшания расширителя 17 импульсов при включении и выключении питающих напряжений, устройстве содержит блок 18 защиты, подключенный к одному из входов расширителя 17 импульсов.

Таким образом, обладая высоким быстродействием, достаточно большим объемом памяти и, высокой стабильностью, а также Ёозможностью исполнения на интегральных элементах, предлагаемое устройство позволит значительно расширить круг задач,

10 решаемых цифровыми и гибридными вычислительными системами, и кроме того, дает возможность приступить к созданию самонастраивающихся распознающих нейронных сетей, что в

15 свою очередь позволит проектировать адаптивные роботы промышленного и специального назначения.

Формула изобретения

20

Интегрирующее устройство с аналоговой памятью, содержащее операционный усилитель, с прямым и инверсным

входами, являющимися входами устро :ства, и магнитный аналоговый регу лируюций и запоминающий блок, о т лич ающе ее я тем, что, с целью повышения быстродействия, оно

дополнительно содержит нуль-орган первый и второй интеграторы, мультивибратор, импульсный усилитель, триггер, первый и второй ждущие мультивибраторы,.расширитель импульсов, логический элемент ИЛИ и

первый, второй, третий, четвертый и пятый ключи, причем выход операционного усилителя подсоединен через первый ключ ко входу первого интегратора, выход которого подключен к

одному их входов нуль-органа, другой вход нуль-органа соединен с выходом магнитногоаналогового регулирующего и запоминающего блока, выход подсоединен ко входу второго и третьего ключей, выходы которых подключе- , ны соответственно ко входу первого и второго интеграторов, выход второго интегратора соединен через четвертый ключ со входом импульсно-° усилителя, выход которого подсоединен к управляющим входам магнитного аналогового регулирующего и запоминатощего блока, выход мультивибратора соединен со.входом -пятого ключа и со счетным входом триггера, прямой выход которого через первый ждущий мультивибратор подсоединен к управляюсцему входу четвертого ключа, а инверсный выход через второй )кду1дип мультивибратор к управляющему входу пятого ключа, выход которого подсоединен ковходу считывания магнитного аналогового регулирующего и запоминающего блока, выход логического элемента ИЛИ,

входами подключенного ко входу устройства, соединен со входом расширителя импульсов, прямой .вьоход которого подсоединен к управляющим входам первого и третьего ключей, а инверсный выход к управляющему входу второго ключа.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 246929, кл. G 06 G 7/18, 1969.

2.Авторское свидетельство СССР 238897, кл. G 06 G 7/14, 1967

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для измерения импульсных напряжений | 1975 |

|

SU676933A1 |

| Устройство для измерения пикового значения ударного импульса | 1983 |

|

SU1132241A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Дозатор непрерывного действия | 1987 |

|

SU1506286A1 |

| Устройство для испытания изоляции на электрическую прочность | 1988 |

|

SU1575140A1 |

| Устройство для контроля ферромагнитных изделий | 1988 |

|

SU1583825A1 |

| Устройство для считывания информации с магнитного носителя | 1990 |

|

SU1739385A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ ОБЪЕКТОВ | 1992 |

|

RU2065569C1 |

| Устройство для регулирования температуры | 1986 |

|

SU1379776A2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ АНАЛОГОВОГО СИГНАЛА ОПТИЧЕСКОГО ДАТЧИКА В ЦИФРОВОЙ КОД | 1995 |

|

RU2097915C1 |

Авторы

Даты

1981-06-30—Публикация

1976-06-10—Подача