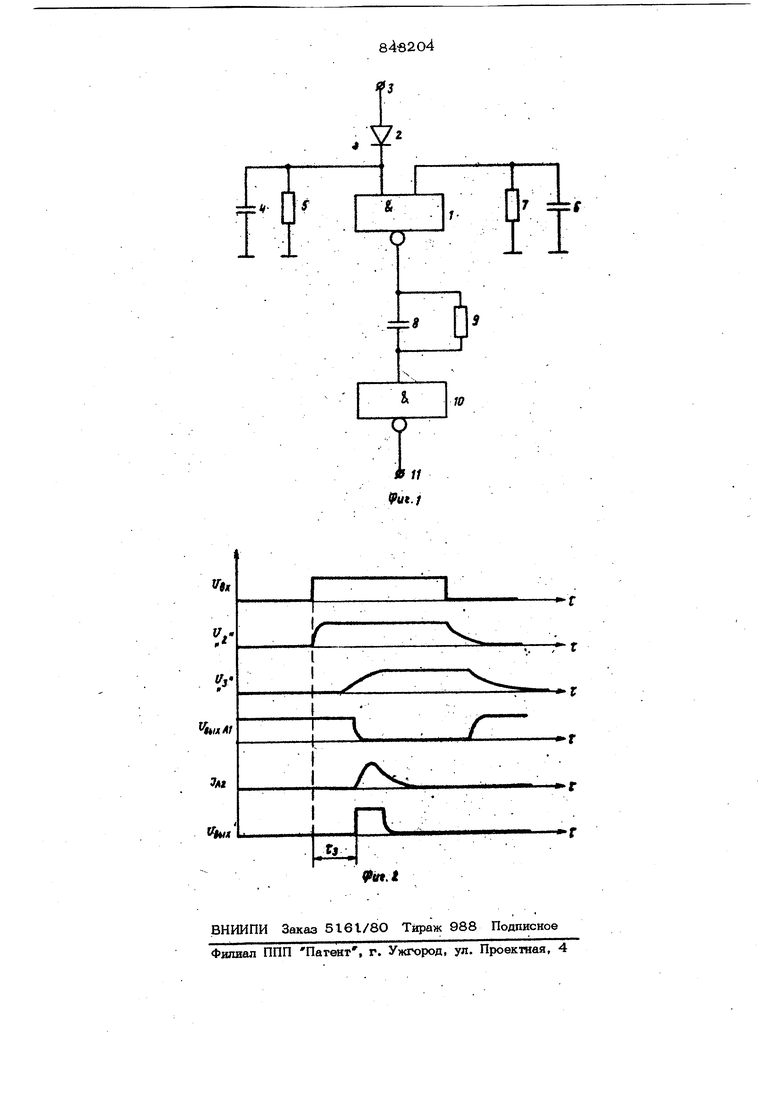

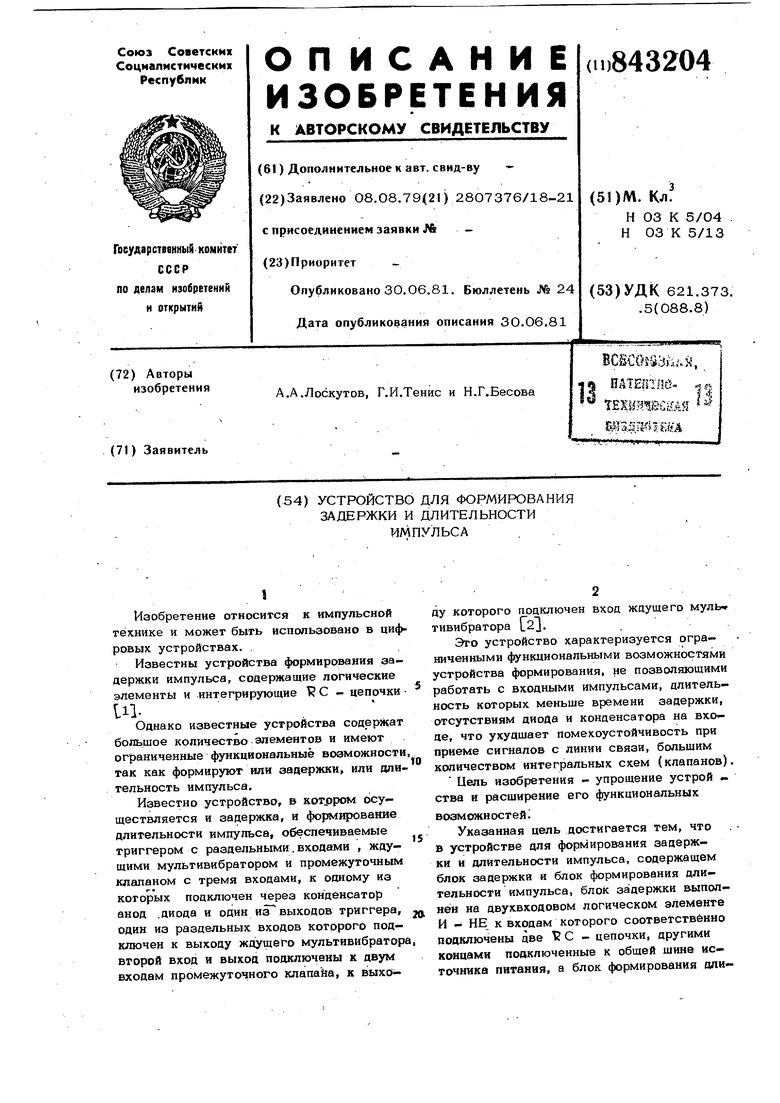

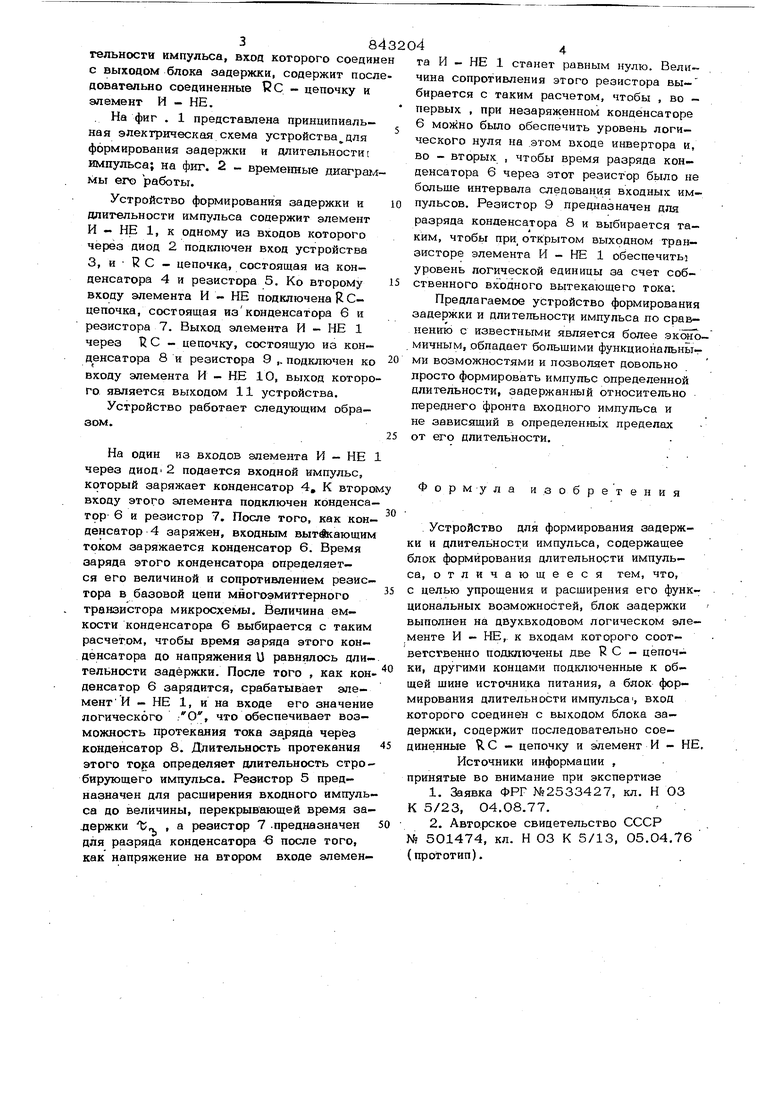

IИзобретение относится к импульсной технике и может быть использовано в ровых устройствах, , Известны устройства формирования задержки импульса, содержащие логические элементы и интегрирующие Т С - цепочки Однако известные устройства содержат большое количество элементов и имеют ограниченные функциональные возможности так как формируют или задержки, или олн тельность импульса. Известно устройство, в котрром осуществляется и задержка, и формирование длительности импульса, обеспечиваемые триггером с раздельными. входами , ждущими мультивибратором и промежуточным клапаном с тремя входами, к одному из которых подключен через конденсатор анод .диода и один иаГ выходов триггера, один из раздельных входов которого подключен к выходу ждущего мультивибратор второй вход и выход подключены к двум входам промежуточного клапана, к выхо ду которого подключен вход ждущего мулы тивибратора L2j, Это устройство характеризуется ограниченными функциональными возможностями устройства формирования, не позволяющими работать с входными импульсами, длительность которых меньше времени задержки, отсутствиям диода и конденсатора на входе, что ухудщает помехоустойчивость при приеме сигналов с линии связи, большим количеством интегральных схем (клапанов). Цель изобретения - упрощение устрой ства и расширение его функциональных возможн остеит Указанная цель достигается тем, что в устройстве для формирования задержки и длительности импульса, содержащем блок задержки и блок формирования длительности импульса, блок задержки выполнен на двухвходовом логическом элементе И - НЕ к входам которого соответственно подключены две Т С - цепочки, другими концами подключенные к общей шине источника питания, а блок формирования дли38гельносгн импульса, вход которого соедин с выходом блока аадерискн, содержит посл довательно соединенные RC - цепочку и элемент И - НЕ. . На фиг . 1 представлена принципиальная электрическая схема устройства для формирования задержки и длительности импульса; на фиг. 2 времеггаые диагршл мы его работы. Устройство формирования задержки и длительности импульса содержит элемент И - НЕ 1, к одному из входов которого через диод 2 подключен вход устройства 3, и R С - цепочка, состоящая иа конденсатора 4 и резистора 5. Ко второму входу элемента И - НЕ подключена R Сцепочка, состоящая изконденсатора 6 и резистора 7. Выход элемента И - НЕ 1 через R С цепочку, состоящую из конденсатора 8 и резистора 9 ,. подключен ко входу элемента И - НЕ 10, выход которо го является выходом 11 устройства. Устройство работает следующим образом. На один из входов элемента И - НЕ 1 через диод-2 подается входной импульс, который заряжает конденсатор 4, К второ входу этого элемента подключен конденсатор 6 и резистор 7. После того, как конденсатор 4 заряжен, входным вытекающим током заряжается конденсатор 6. Время заряда этого конденсатора определяется его величиной и сопротивлением резистора в базовой цепи многоэмиттерного транзистора микросхемы. Величина емкости конденсатора 6 выбирается с таким расчетом, чтобы время заряда этого конденсатора до напряжения U равнялось длительности задержки. После того , как конденсатор 6 зарядится, срабатывает элемент И - НЕ 1, и на входе его значение логического .О, что обеспечивает возможность протекания тока заряда через конденсатор 8. Длительность протекания этого Tofca определяет длительность стробирующего импульса. Резистор 5 предназначен для расширения входного импульса до величины, перекрывающей время задержки t/ , а резистор 7 .предназначен для разряда конденсатора 6 после того, как напряжение на втором входе элемен4та И - НЕ 1 станет равным нулю. Величина сопротивления этого резистора вы- бирается с таким расчетом, чтобы , во первых , при незаряженном конденсаторе 6 можно было обеспечить уровень логического нуля на этом входе инвертора и, во - вторых , чтобы время разряда конденсатора 6 через этот резистор было не больще интервала следования входных импульсов. Резистор 9 предназначен для разряда конденсатора 8 и выбирается таким, чтобьг при открытом выходном транзисторе элемента И - НЕ 1 обеспечить уровень логической единицы за счет собственного входного вытекающего тока; Предлагаемое устройство формирования задержки и длительности импульса по сравнению с известными является более экшомичным, обладает бопьщими функциональными возможностями и позволяет довольно просто формировать импульс определенной длительности, задержанный относительно переднего фронта входного импульса и не зависящий в определенных пределах от его длительности. Формула изобретения Устройство для формирования задержки и длительности импульса, содержащее блок формирования длительности импульса, отличающееся тем, что, с целью упрощения и расширения его функциональных возможностей, блок задержки выполнен на двухвходовом логическом элементе И - НЕ, к входам которого соответственно подключены две R С - цепочки, другими концами подключенные к общей щине источника питания, а блок формирования длительности импульса , вход которого соединен с выходом блока задержки, содержит последовательно соединенные Я С - цепочку и элемент И - НЕ. Источники информации , принятые во внимание при экспертизе 1.Заявка ФРГ №2533427, кл. Н ОЗ К 5/23, 04.08.77. 2.Авторское свидетельство СССР N 501474, кл. Н 03 К 5/13, 05.04.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый ступенчатый преобразователь | 1981 |

|

SU1051668A1 |

| Релаксационный формирователь импульсов | 1977 |

|

SU734871A1 |

| Стабилизированный преобразователь постоянного напряжения с защитой | 1986 |

|

SU1317597A2 |

| Ждущий мультивибратор | 1978 |

|

SU782134A1 |

| Импульсный зонд для контроля цифровых схем | 1978 |

|

SU788054A1 |

| Устройство для зарядки накопительного конденсатора | 1988 |

|

SU1684913A1 |

| Устройство для контроля электромагнита | 1985 |

|

SU1290266A1 |

| Многоканальное устройство согласования коммутационной цепи переменного тока с интегральной микросхемой | 1984 |

|

SU1307552A1 |

| Ждущий мультивибратор | 1986 |

|

SU1354396A1 |

| Регулятор напряжения | 1972 |

|

SU477513A1 |

tf,

ttixM

I /.

УМ

Авторы

Даты

1981-06-30—Публикация

1979-08-08—Подача