(54) ДЕКОДИРУЮЩИЙ НАКОПИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Декадирующий накопитель | 1978 |

|

SU790288A1 |

| Декодирующее устройство | 1979 |

|

SU809550A1 |

| Статистический анализатор | 1981 |

|

SU962979A1 |

| Анализатор импульсных последовательностей | 1989 |

|

SU1711089A1 |

| Декодирующее устройство | 1979 |

|

SU864543A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ В УСЛОВИЯХ ПОМЕХ | 1991 |

|

RU2030757C1 |

| Декодирующее устройство для систем телемеханики | 1978 |

|

SU748871A1 |

| Декодирующее устройство | 1979 |

|

SU826560A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ СИГНАЛА | 2008 |

|

RU2357372C1 |

1

Изобретение относится к импульсной технике и может найти применение в ycTpoiicTBax повышения достоверности передаваемой информации.

Известны устройства для мажоритарного декодирования двоичных кодов при трехкратном повторении сообщений которые содержат регистры сдвига и логические элементы ООднако эти устройства имеют огранченные функциональные возможности.

Известен также декодирующий накопитель, содержащий ключ, т-разрядный сумматор и счетчик повторений, соединенный с управляющим входом ключа, выход которого соединен с накопителем, и анализатор 12.

Недостаток накопителл - сложность и как следствие - низкая надежность.

Цель изобретения - повьппение надежности функционирования.

Указанная цель достигается тем, что в декодирующий накопитель, содержащий ключ, счетчик повторений.

.входы которых объединены и подключены к входной шине, выход счетчика поторений соединен с управляющим входом ключа, выход которого через последовательно соединенные накопитель и т-разрядный сумматор подключен ко входу анализатора, введены дискриминатор. Пороговый элемент и переключатель, при этом первые входы дискриминатора и переключателя соединены с входной шиной, а вторые входы подключены соответственно к выходу накопителя и выходу дискриминатора, выход переключателя соединен со входом гг-разрядного сумматора, вход и выход порогового элемента соединены соответственно с выходом т-разрядного сумматора и входом ключа.

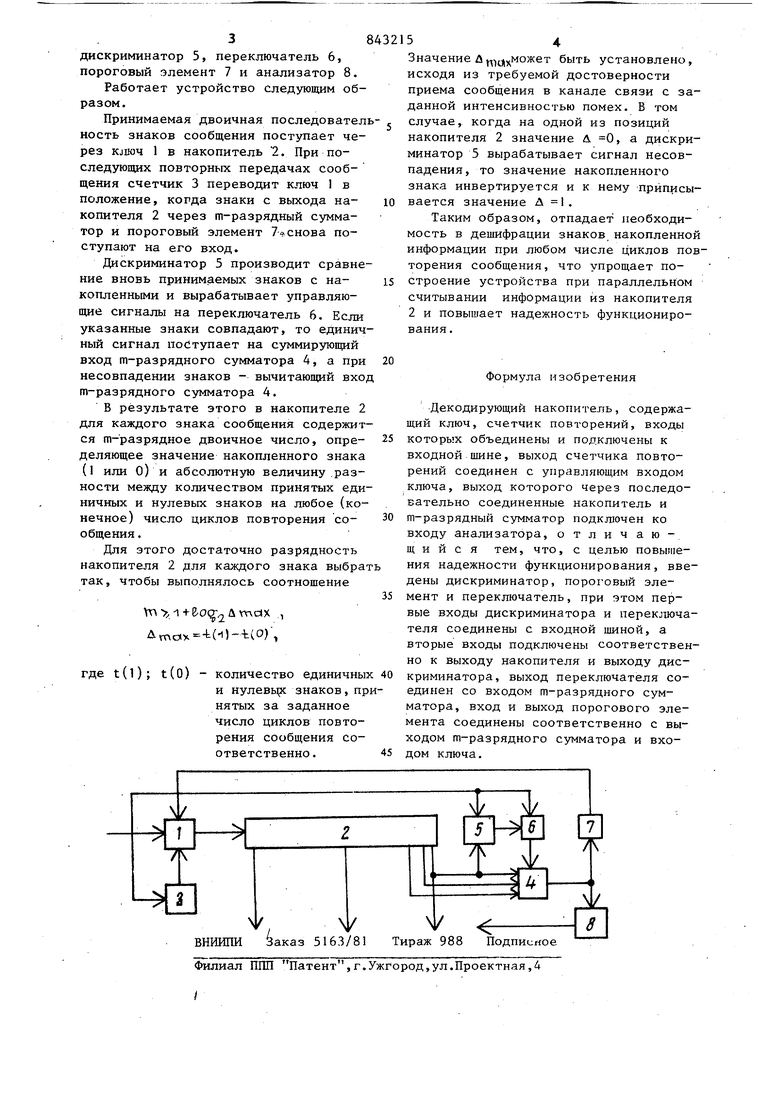

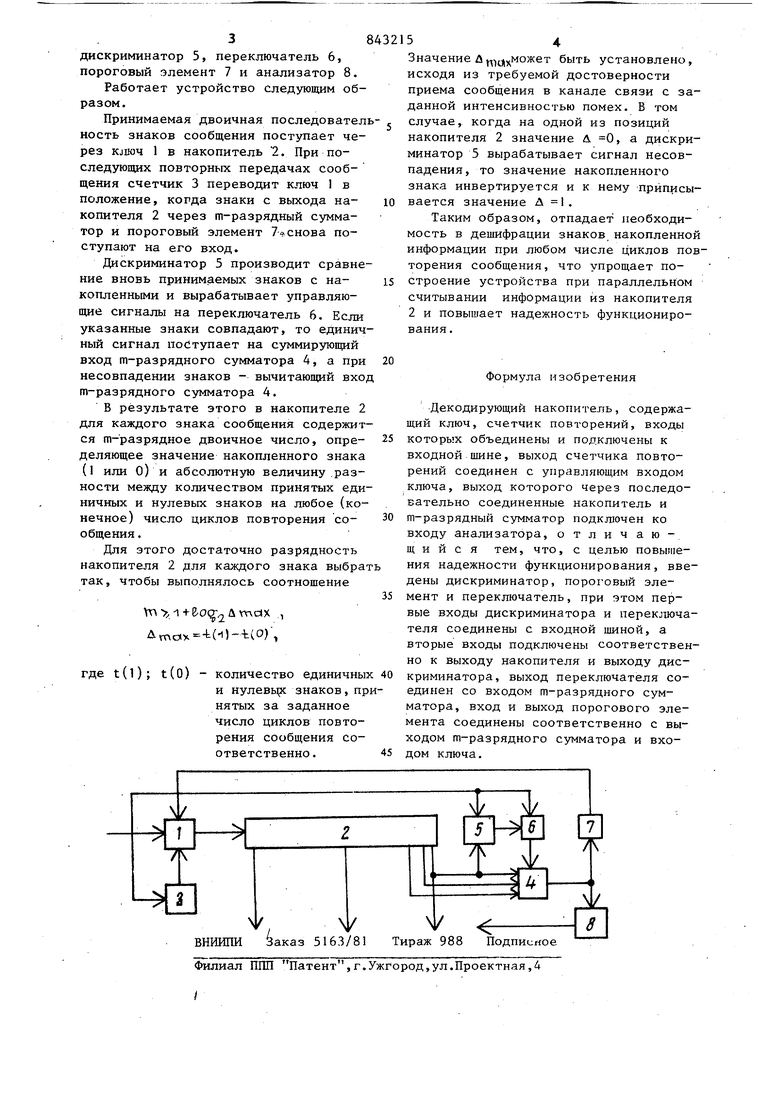

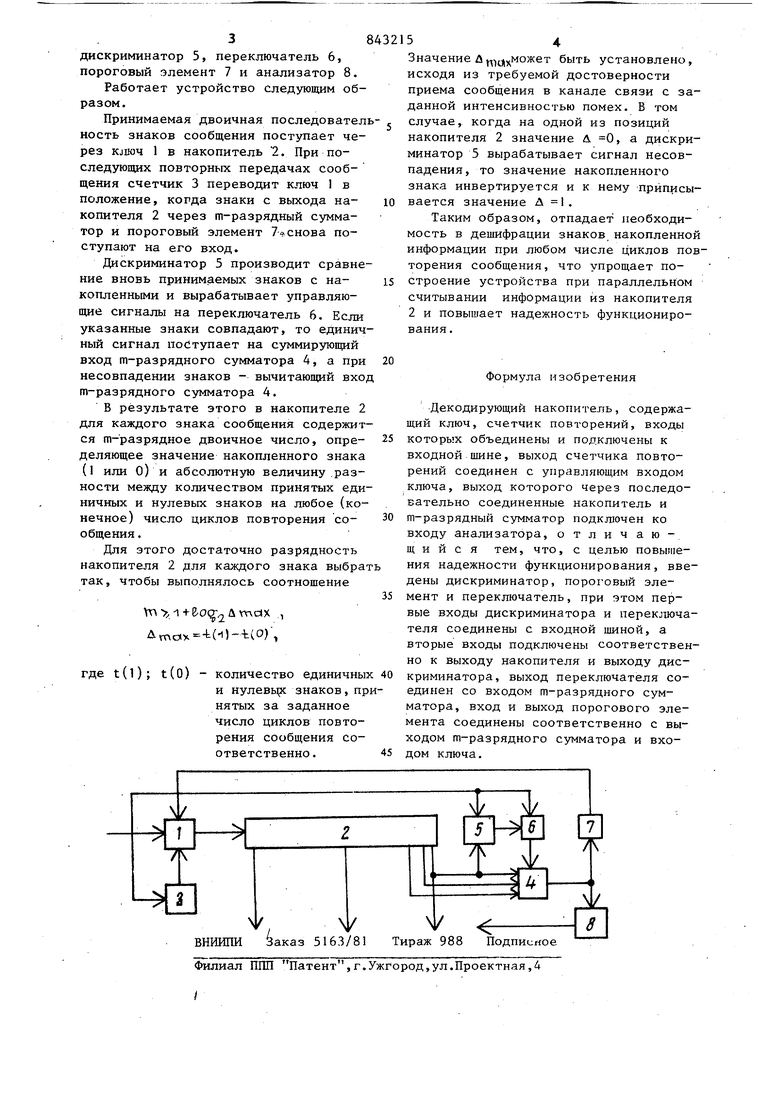

На чертеже приведена структурная схема декодирующего накопителя.

Устройство содержит входной ключ 1., накопитель 2, имеющий m разрядов на каждый принимаемый знак, счетчик 3 повторений, т-разрядный сумматор 4 3 дискриминатор 5, переключатель 6, пороговый элемент 7 и анализатор 8. Работает устройство следующим об разом. Принимаемая двоичная последовател ность знаков сообщения поступает через KjLo4 1 в накопитель 2. При последующих повторных передачах сообщения счетчик 3 переводит ключ 1 в положение, когда знаки с выхода накопителя 2 через т-разрядный сумматор и пороговый элемент 7 снова поступают на его вход. Дискриминатор 5 производит сравне ние вновь принимаемых знаков с накопленными и вырабатывает управляющие сигналы на переключатель 6. Если указанные знаки совпадают, то единич ный сигнал поступает на суммирующий вход т разрядного сумматора 4, а при несовпадении знаков - вычитающий вхо т-разрядного сумматора 4. В результате этого в накопителе 2 для каждого знака сообщения содержит ся т-разрядное двоичное число, определяющее значение накопленного знака (1 или о) и абсолютную величину .разности между количеством принятых еди ничных и нулевых знаков на любое (конечное) число циклов повторения сообщения. Для этого достаточно разрядность накопителя 2 для каждого знака выбра так, чтобы выполнялось соотношение Vr ./1 + &0(, д vrvctx , Amotx -t(-i)--t(0) где t(l); t(0) количество единичны и нулевьрс знаков, пр нятых за заданное число циклов повторения сообщения соответственно. 1 54 Значение ,может быть установлено, исходя из требуемой достоверности приема сообщения в канале связи с заданной интенсивностью помех. В том случае, когда на одной из позиций накопителя 2 значение д 0, а дискриминатор 5 вырабатывает сигнал несовпадения, то значение накопленного знака инвертируется и к нему приписывается значение Д 1. Таким образом, отпадает необходимость в дешифрации знаков накопленной информации при любом числе циклов повторения сообщения, что упрощает построение устройства при параллельном считывании информации из накопителя 2 и повышает надежность функционирования. Формула изобретения Декодирующий накопитель, содержащий ключ, счетчик повторений, входы которых объединены и подключены к входной шине, выход счетчика повторений соединен с управляющим входом ключа, выход которого через последовательно соединенные накопитель и т-разрядный сумматор подключен ко входу анализатора, отличающийся тем, что, с целью повышения надежности функционирования, введены дискриминатор, пороговый элемент и переключатель, при этом первые входы дискриминатора и переключателя соединены с входной шиной, а вторые входы подключены соответственно к выходу накопителя и выходу дискриминатора, выход переключателя соединен со входом т-разрядного сумматора, вход и выход порогового элемента соединены соответственно с выодом т-разрядного сумматора и вхоом ключа.

Авторы

Даты

1981-06-30—Публикация

1979-10-29—Подача