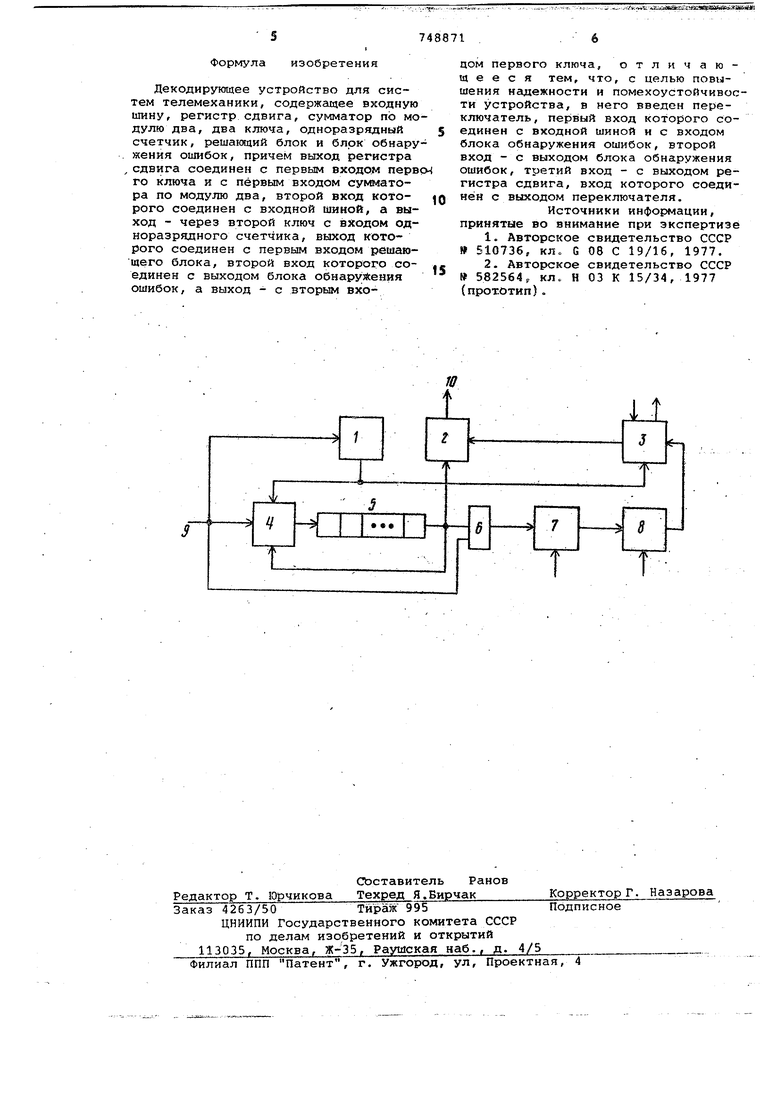

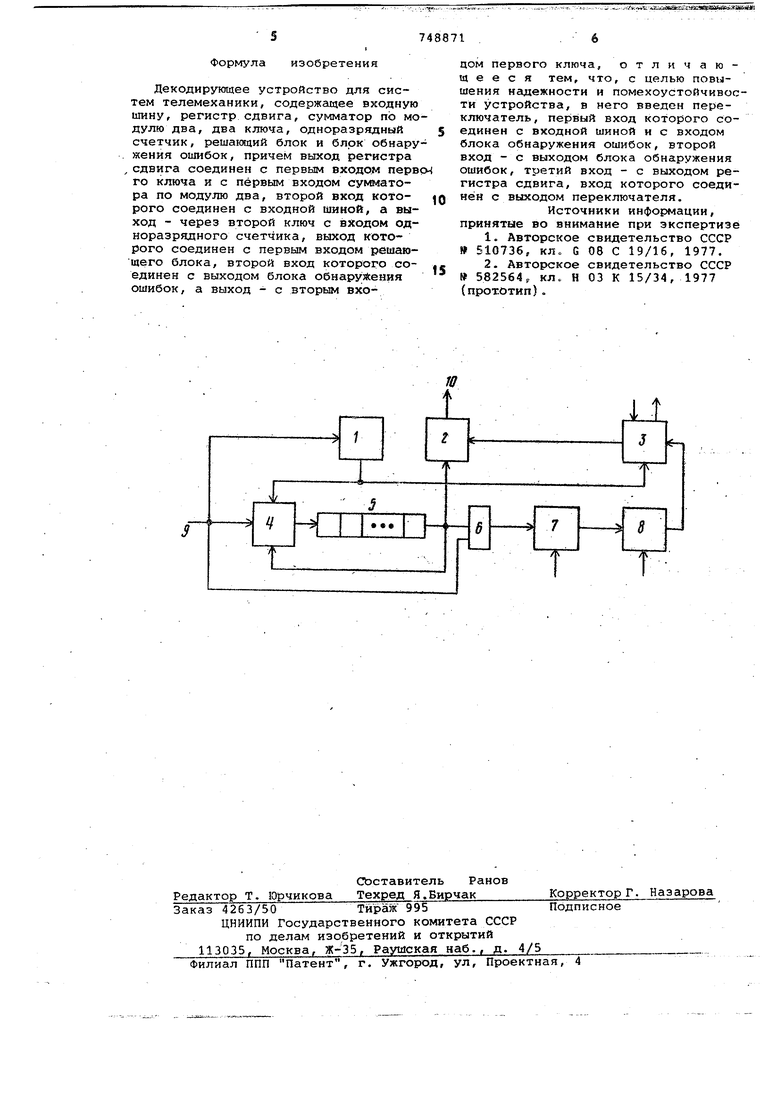

Изобретение относится к области вычислительной техники и телемеханики и может быть использовано в системах передачи и обработки дискретной информации. Известно декодирующее устройство, использующее для повышения достоверности метод многократного повторения информации ГЦ . Недостатком известного устроЯства является его сложность. Известно также декодирующее устройство для исправления одиночных ошибок в кодовых комбинациях, содержащее входную шину, регистр сдвига, два сумматора по модулю два, три клю ча, два счетчика, решающий блок и блок обнару/1;ения ошибок. Причем выход регистра сдвига соединен с первы входом первого сумматора по модулю два и с первым входом первого ключа, второй вход первого сумматора соединен с входной шиной и с входом регис ра сдвига, а выход соединен через вт рой ключ с входом первого счетчика, выход которого подключен к первому входу решающего блока, второй вход решающего блока соединен с выходом блока обнаружения ошибок,вход которо го соединен с выходом регистра сдвига, выход первого ключа соединен с первым входом второгосумматора, второй вход которого подключен к выходу второго счетчика, первый и второй входы второго счетчика соединены соответственно с первым 1-ходом третьего ключа, с третьим входом решающего блока и с выходом третьего ключа, второй вход которого соединен с выходом второго ключа f2j. Недостатками такого устройства являются его сложность (и, как следствие, низкая надежность) и низкая помехоустойчивость для определенного класса систем, использующих многократную передачу повторений (в частности для односторонн1 х систем и систем с решающей обратной связью).Уменьшение помехоустойчивости обуславливается наличием потерь информации в результате поражения многократными ошибками серии повторений, в то время как в каждой паре сравниваемых коМ бинаций одна оказывается неискаженной- Целью изобретения является повышение надежности и помехоустойчивости устройства. Для достижения поставленной цели в декодирующее устройство для систем телемеханики, содержащее входную шину, регистгр сдвига, сумматор rto модулго два, два ключа, одноразрядный счетчик, решающий блок и блок обнаружения ошибок, причем выход регистра сдвига соединен с первым входом первого ключа и с первым входЬм сумматора по мсгцулю два, второй вход ко торого соединен с входной шиной,а вы ход - через второй ключ с входом од оразрядного счетчика, выходом соеди ненного с первым входом решающего бл ка, второй вход которого подключен к выходу блока обнаружения ошибок , а выход - к второму входу первого ключа, введен переключатель, первый вхо которого соединен с входной и с входом блока обнаружения ошибок, второй вход - с выходом блока обнару жения ошибок, третий вход - с выходо регистра сдвига, вход которого соеди нен с выходом переключателя. На чертеже изображена структурная блок-схема предлагаемого устройства. Устройство содерАкт блок 1 обнаружения ошибок, ключ 2, решающий блок 3, переключатель 4, регистр сдв га 5, сумматор по модулю два б,ключ 7 одноразрядный счетчик 8, входную шину 9 и выходную шину 10. Входная шина соединена с входом блока обнаружения ошибок и с одними входами переключателя 4 и сумматора; по модулю два 6, другие входы которы соединены с выходом регистра сдвига и с первым входом ключа 2. Выход сум матора по модулю два соединен через ключ 7 с входом одноразрядного счетчика 8, выход которого подключен к первому входу решающего блока 3. Второй вход решающего блока соединен с третьим входом переключателя 4 и с выходом блока 1 Обнаружения ошибок, выход решающего блока соединен с вто рым входом ключа 2. Блок обнаружения ошибок производит анализ принимаемой комбинации на отсутствие или наличие ошибок.Ключ обеспечивает вйвод комбинации из регистра сдвига на выход устройства. Решающий блок 3 ocSЩecтвляeт управление ключом 2 в зависимости от сигналов на его входах. Переключатель 4 переключает вход регистра сдвига 5 от входной шины 9 на свой выход. Регистр сдвига предназначен для записи и хранения поступающих комбинаций. Ключ 7 предназначен для подключения счетчика 8 к выходу сумматора по модулю два 6 по окончании ввода в регистр сдвига первого повторения сообщения. Одноразрядный счётчик 8 осуществляет подсчет числа несовпа денмй сравниваемых комбинаций. Работает устройство следунмаим образом. . поступающая по входной шине 9 ком бинация помехоустойчивого кода через переключатель 4 записывается в регистр сдвига 5. Одновременно с записью в регистр сдвига эта комбинация проверяется в блоке 1 на отсутствие или наличие ошибок. Если ошибка не обнаружена,блок 1 выдает сигнал-в решающий блок 3, ас помощью переключателя 4 регистра сдвига соединяет с его входом. Комбинация второго повторения подается на один из входов сумматора 6. При этом комбинация первого повторения одновременно с поступлением на другой вход сумматора перезаписывается в регистр сдвига 5. Таким образом, одновременно с перезаписью комбинации первого повторения происходит поэлементное сравнение обеих комбинаций. Если в результате поэлементного сравнения комбинаций окажется, что они идентичны или произошло лишь одно несовпадение (учитываемое одноразрядным счетчиком 8), то решающий блок 3, открывая ключ 2, производит вывод комбинации из регистра сдвига 5 ка выходную шину 10. В случав обна зужения ошибки в первом повторении в регистр сдвига через переключатель 4 вводится второе повторение. Комбинация второго повторения, поступающая в регистр 5,поразрядно сравнивается с первой на сумматоре 6. При этом учитывается результат анализа второго повторения, осуществляемого блоком 1 обнаружения ошибок. Если повторная комбинация окажется неискаженной и произойдет не более одного несовпадения, то на выходную шину 10 выдается второе повторение сообщения. Если для обоих вариантов, описанных выше, окажется, что произошло два и более несовпадений, импульс переполнения счетчика 8 поступает в решающий блок 3, исключая вьщачу комбинации на выходную шину 10, В случае обнаружения ошибок в обоих повторениях или при возникновении более Одного несовпадения в сравниваемых комбинациях, решающий блок формирует сигнал переспроса в системах с обратной связью. Использование предлагаемого технического решения в системах с решающей обратной связью позволяет уменьшить потери информации, а следовательно, повысить скорость передачи и оперативность. Это достигается за счет того, что в регистре сдвига сохраняется неискаженное повторение комбинации, которое принимает участие в проверках при поступлении запрашиваемого сообщения. В известном устройстве отсутствие искажений в первой комбинации и наличие двукратной ошибки во второй приводит к потере сообщения . изобретения Формула Декодирующее устройство для систем телемеханики, содержащее входную шину, регистр сдвига, сумматор по мо дулю два, два ключа, одноразрядный счетчик, решающий блок и блок обнару жения ошибок, причем выход регистра , сдвига соединен с первым входом neps го ключа и с первым входом су№«атора по модулю два, второй вход которого соединен с входной шиной, а выход - через второй ключ с входом одноразрядного счетчика, выход которого соединен с первым входом решгиощего блока, второй вход которого соединен с выходом блока обнару;лсеаия ошибок, а выход - с вторым вхоцом первого ключа, отличающееся тем, что, с целью повышения надежности и помехоустойчивости устройства, в него введен переключатель, первый вход которого соединен с входной шиной и с входом блока обнаружения ошибок, второй вход - с выходом блока обнаружения ошибок, третий вход - с выходом регистра сдвига, вход которого соединён с выходом переключателя. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР 510736, кл« G 08 С 19/16, 1977. 2.Авторское свидетельство СССР № 582564р кл Н 03 К 15/34, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Устройство для приема информации по двумпАРАллЕльНыМ КАНАлАМ СВязи B СиСТЕМЕ дляпЕРЕдАчи дАННыХ C РЕшАющЕй ОбРАТНОй СВязью | 1979 |

|

SU836806A2 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Декодирующее устройство | 1976 |

|

SU582564A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Декодирующее устройство | 1985 |

|

SU1349009A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1984 |

|

SU1202057A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

10

t

U

Авторы

Даты

1980-07-15—Публикация

1978-05-04—Подача