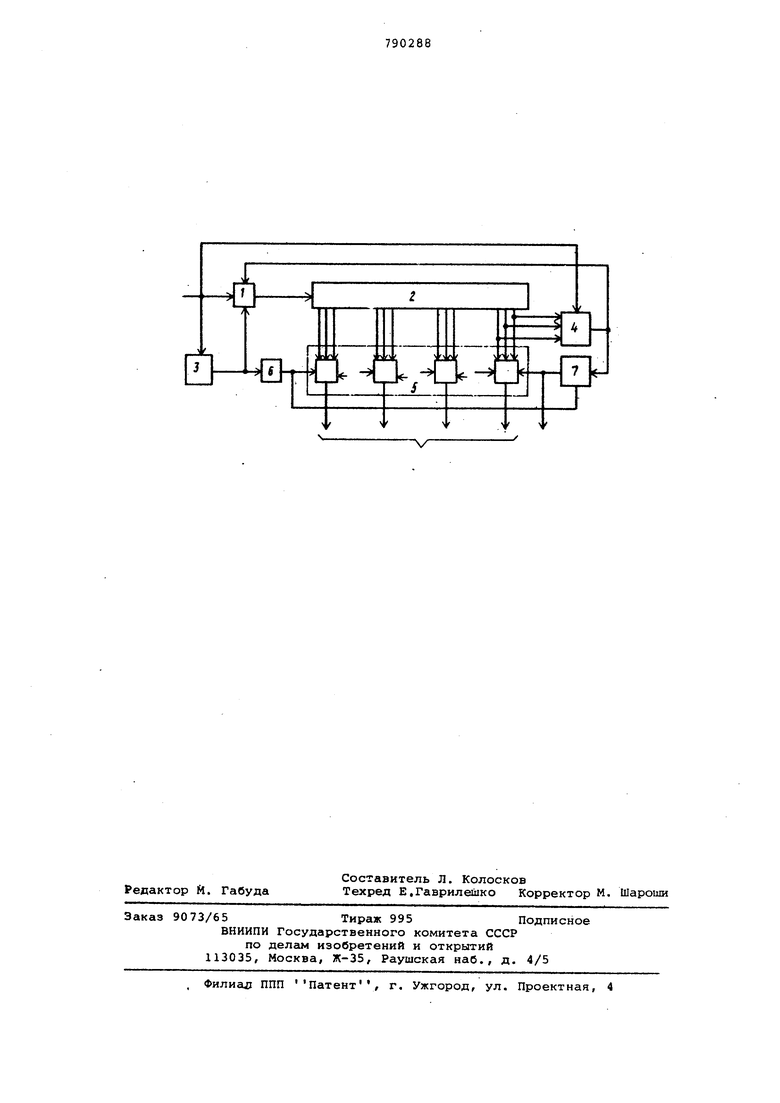

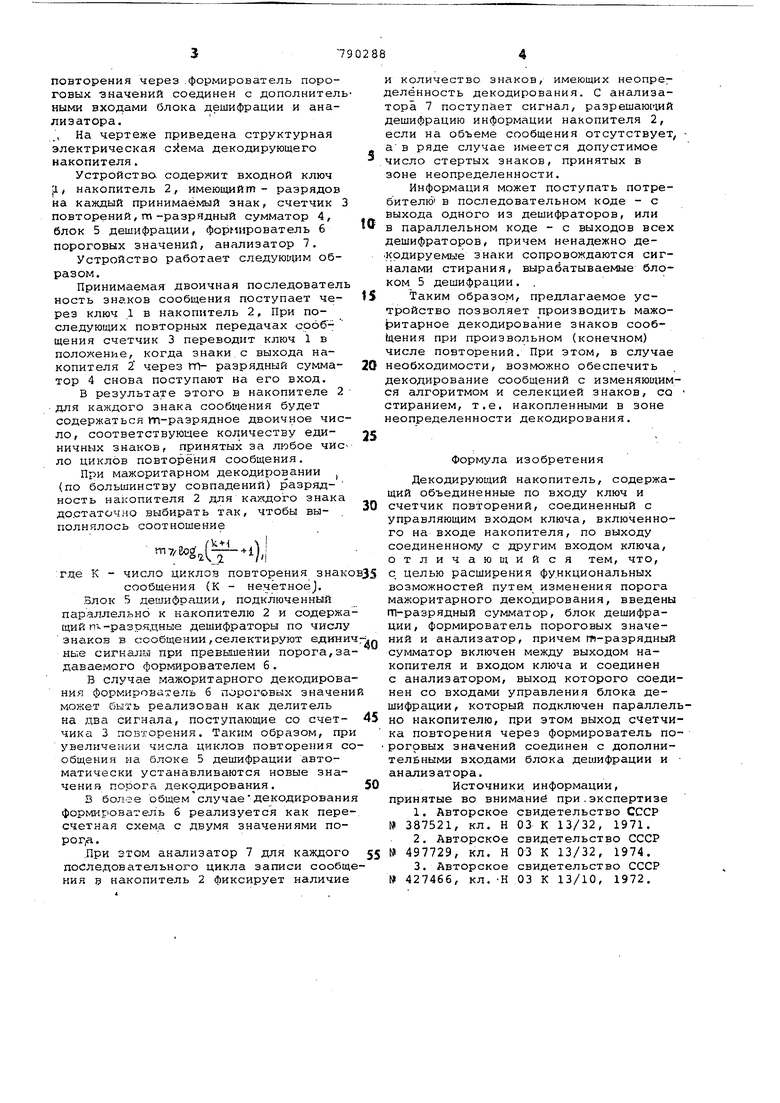

Изобретение относится к импульсной технике и может найти применение в устройствах повышения достоверност передаваемой информации. Известны устройства, предназначен ные для мажоритарного декодирования двоичных кодов при трехкратном дублировании (повторении).сообщений, ко торые содержат регистры сдвига и логические элементы 1 и 2J. Однако эти устройства имеют ограниченные функциональные возмол.мости. Известен также декодирующий накопитель, обеспечивакиций мажоритарное вынесение решенргя по принимаемым зна кам при трехкратном повторении кодовых комбинаций и являющийся наиболее близким к предлагаемому изобретению по технической сущности и по достига емому результату (3. Однако известный декодирующий накопите/1ь не обеспечивает мажоритарно декодирование при числе повторений кодовцх комбинаций большем трех. Это ограничивает функциональные возможности известного устройства, таккак, например, в дуплексных системах связи с решающей обратной связью для ;помехоустойчивого приема информации может потребоваться большее число повторений, изменяющихся в широких пределах. Кроме того, в известном устройстве нельзя изменять порог мажо ритарного декодирования,что требует ся при приеме сообщений в нестационарных каналах связи, где вероятность приема ошибочных знаков может значительно изменяться. Это также ограничивает функциональные возможности известного устройства. Цель изобретения - расширение функциональных возможностей путем изменения порога мажоритарного декодирования.. Указанная цель достигается тем, что в декодирующий накопитель, содержащий объединенные по входу ключ и счетчик, повторений соединенный с управляющим входом ключа, включенного на входе накопителя, по выходу соединенному с другим входом ключа, вйеденыт-разрядный сумматор, блок дешифрации, формирователь пороговых, значений и анализатор, причем,m -разрядный сумматор включен между выходом накопителя и входом ключа и соединен с анализатором/ выход которого соединен со входами управления блока дешифрации, который подключен параллельно накопителю. При этом выход счетчика повторения через .формирователь пороговых -значений соединен с дополнител ными входами блока дешифрации и анализатора. На чертеже приведена структурная электрическая декодирующего накопителя. Устройство содержит входной ключ PL, накопитель 2, имеющийm - разрядов на каждый принимаемый знак, счетчик повторений,га-разрядный сумматор 4, блок 5 дешифрации, формирователь 6 пороговых значений, анализатор 7. Устройство работает следующим образом. Принимаемая двоичная последовател ность знаков сообщения поступает через ключ 1 в накопитель 2, При последующих повторных передачах opoffщения счетчик 3 переводит ключ 1 в положение, когда знаки,с выхода накопителя 2 через т- разрядный сумматор 4 снова поступают на его вход. В результате этого в накопителе 2 для каждого знака сообщения будет содержаться т-разрядное двоичное чис ло, соответствующее количеству единичных знаков, принятых за любое чис ло циклов повторения сообщения. При мажоритарном декодировании (по большинству совпадений) разрядность накопителя 2 для каждого знака достаточно выбирать так, чтобы выполнилось соотношение Bcg(b±i..i) I :где К - число циклов повторения знак сообщения (К - нечетное}. Блок 5 дешифрации, подключенный параллельно к накопителю 2 и содерж щий т- -разрядные дешифраторы по числ знаков в сообщении, селектируют един ные сигналы при превышейии порога,з даваемого формирователем 6. В случае мажоритарного декодиров ния формирователь 6 пороговых значен может быть реализован как делитель на два сигнала, поступающие со счетчика 3 повторения. Таким образом, пр увеличении числа циклов повторения с общения на блоке 5 дешифрации автоматически устанавливаются новые значения порога декодирования. В более общем случаедекодирован формирователь б реализуется как пере счетная схема с двумя значениями поpor i. Лри этом анализатор 7 для каждого последовательного цикла записи сообщ ния 5 накопитель 2 фиксирует наличие и количество знаков, имеющих неопределённость декодирования. С анализатора 7 поступает сигнал, разрешающий дешифрацию информации накопителя 2, если на объеме сообщения отсутствует, ав ряде случае имеется допустимое число стертых знаков, принятых в зоне неопределенности. Информация может поступать потребителю в последовательном коде - с выхода одного из дешифраторов, или в параллельном коде - с выходов всех дешифраторов, причем ненадежно декрдируемые знаки сопровождаются сигналами стирания, вырабатываемые блоком 5 дешифрации. . Таким образом, предлагаемое устройство позволяет производить мажоритарное декодирование знаков сооб цения при произвольном (конечном) числе повторений. При этом, в случае необходимости, возможно обеспечить декодирование сообщений с изменяющимся алгоритмом и селекцией знаков, со стиранием, т.е. накопленными в зоне неопределенности декодирования. Формула изобретения Декодирующий накопитель, содержащий объединенные по входу ключ и счетчик повторений, соединенный с управляющим входом ключа, включенного на входе накопителя, по выходу соединенному с другим входом ключа, отличающийся тем, что, с. целью расширения функциональных возможностей путем изменения порога мажоритарного декодирования, введены гп-разрядный сумматор, блок дешифрации, формирователь пороговых значений и анализатор, причем т-разрядный сумматор включен между выходом накопителя и входом ключа и соединен с анализатором, выход которого соединен со входами управления блока дешифрации , который подключен параллельно накопителю, при этом выход счетчика повторения через формирователь пороговых значений соединен с дополнительными входами блока дешифрации и анализатора. Источники информации, принятые во внимание при .экспертизе 1.Авторское свидетельство СССР № 387521, кл. Н 03 К 13/32, 1971. 2.Авторское свидетельство СССР 497729, кл. Н 03 К 13/32, 1974. 3.Авторское свидетельство СССР W 427466, кл. Н 03 К 13/10, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующий накопитель | 1979 |

|

SU843215A1 |

| Декодирующее устройство | 1979 |

|

SU809550A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Декодирующее устройство | 1979 |

|

SU864543A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Мажоритарное декодирующее устройство | 1981 |

|

SU1005059A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2007866C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ ЦИКЛИЧЕСКИХ | 1970 |

|

SU261460A1 |

| Устройство для выделения сигналов фазового пуска | 1978 |

|

SU780215A1 |

Авторы

Даты

1980-12-23—Публикация

1978-12-07—Подача