(5А) ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ДВОИЧНЫЙ КОД И ОБРАТНО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство дискретной обработки информации | 1980 |

|

SU884140A1 |

| Устройство дискретной обработкииНфОРМАции | 1979 |

|

SU805494A1 |

| Преобразователь кода грея в двоичный код и обратно | 1978 |

|

SU750733A1 |

| Преобразователь кода грея в двоичный код | 1977 |

|

SU661790A1 |

| ВСЕСОЮЗНАЯ [iirti tillМ.Кл. G 06f 5/02УДК 681.332.65(088.8)Авторы | 1973 |

|

SU365702A1 |

| Формирователь огибающей | 1986 |

|

SU1709391A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| Устройство для предварительной проверки транзисторов | 1982 |

|

SU1101762A1 |

| Устройство для опроса объектов телеизмерения и телесигнализации | 1977 |

|

SU714459A1 |

| Устройство для опроса объектов телеизмерений и телесигнализации | 1983 |

|

SU1105925A1 |

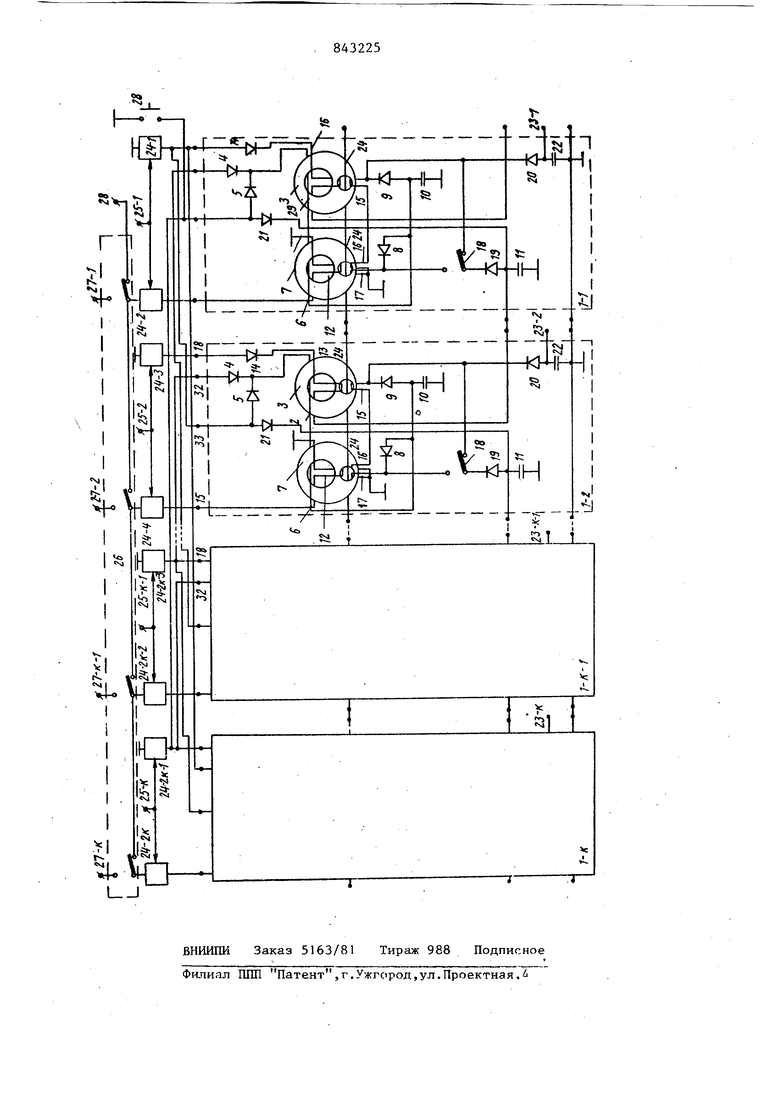

Изобретение относится к автомати и вычислительной технике и может быт использовано при ностроении цепей обратной связи цифровых следящих сис тем. Известно устройство, содержащее .блок неравнозначности и блок запоминания/ в каждом из которых обмотка считывания трансфлюксоров соединены последовательно, входная обмотка пер вого транфлюксора блока неравнозначности соединена с первой входной шин первый вход входной обмотки второго трансфлюксора блока неравнозначности соединен через первый диод с шиной первого тактового сигнала, а второй вывод через второй диод подключен к шине обнуляющего сигнала и через обмотку обнуления, подключен к первому выводу конденсатора и аноду первого диода блока запоминания П. Известно также устройство, содерж щее два блока неравнозначности, в ка дом из которых первый вывод обмотки обнуления первого трансфлюксора подключен к катодам первого и второго диодов, а второй вывод через обмотку обнуления второго трансфлюксора соединен с анодами третьего и четвертого диодов и с первой обкладкой первого конденсатора, вторая обкладка которого -соединена с общей шиной, с первой обкладкой второго конденсатора и с первым выводом входной обмотки второго трансформатора, первый вьтвод входной обмотки первого трансфлюксора соединен с катодом пятого диода, первый вывод выходной обмотки первого трансфлюксора соединен через первую выходную обмотку второго транафлюксора с общей шиной.и с первым выводом второй выход,ной обмотки второго трансфлюксора, второй вывод которой соединен с катодом третьего диода и с замыкающим контактом первого переключателя, переключающий контакт которого через шестой диод соединен со второй обкладкой второго кои;ич1сатора, а размыкаюпщй контакт соединен с катодом седьмого диода и со вторым выводом выходной обмотки второго транс-флюксора, анод первого диода соединен с анодом восьмого диода, в первом блоке неравнозначности анод седьмого диода соединен с первой шиной выходного сигнала и через третий конденсатор с общей шиной, анод шестого диода первого блока неравнозначности соединен со вторым выводом входной обмотки первого трансфлгоксора второго блока неравнозначности, аноды пятых Диодов первого и второго блоков неравнозначности соединены соответственно с выхо дами первого и второго ключей, входы которых соединены с общей шиной, а управляющие входы соединены соответственно с первой и второй шина{ и тактового сигнала, вторые выводы обмоток вторых трансфлюксоров первого и второго блоков неравнозначности соединены соответственно с выводами третьего и четвертого ключей, управляющие входы которых соединены соответственно с шинами первого и второго тактовых .сигналов, выход первого ключ соединен с анодом первого диода второго блока неравнозначности, в первом блоке неравнозначности .анод первого диода соединен через кнопку с общей шиной,анод второго диода первого бл ка неравнозначности соединен с выходом второго ключа, обмотки считывани всех трансфлюксоров первого и второг блоков неравнозначности соединены по следовательно С2} . Недостаток известных устройств низкая помехозащищенность. Цель изобретения - повышение поме хозащшценности. Поставленная цель достигается тем что, 3 устройство, содержащее два бл ка неравнозначности, в каждом из которых, первый вывод обмотки обнуления первого трансфлк ксора подключен к катодам первого и второго диодов, а второй вывод через обмотку обнуления второго трансфлюксора соединен с анодами третьего и четвертого диод и с первой обкладкой .первого конденсатора, вторая обкладка которого сое динена с общей шиной , с первой обкладкой второго конденсатора и с пер вым выводом входной обмотки второго трансфлюксора, первый вывод входной обмотки первого трансфлюксора соединен с катодом пятого диода, первый вывод выходной обмотки первого трансфлюксора соединен через первую выходную обмотку второго трансфлюксора с общей шиной и с первым выводом вто-рой выходной обмотки второго трансфлюксора, второй вывод которой соединен с катодом третьего диода и с замыкающим контактом первого переключателя, переключаю1ций контакт которого через шестой диод соединен со второй обкладкой второго конденсатора, а размыкающий контакт соединен с катодом седьмого диода и со вторым выводом выходной обмотки второго трансйшюксора, анод первого диода соединен с анодом восьмого диода, в первом блоке неравнозначности анод седьмого диода соединен с первой шиной выходного сигнала и через третий конденсатор с общей шиной, анод шестого диода первого блока неравнозначности соединен со вторым выводом входной обмотки первого трансфлюксора второго блока неравнозначности аноды пятых диодов первого и второго блоков неравнозначности соединены соответственно с выходами первого и второго ключей, входы которых соединены с общей шиной, а управляющие входы соединены соответственно с первой и второй шинами тактового сигнала, вторые выводы входных обмоток вторых трансфлюксоров первого и JBTOPOго блоков неравнозначности соединены соответсвенно с выходами третьего и четвертого ключей, управляющие входы кото1)ых соединены соответственно с шинами первого и второго тактовыхс сигналов, выход первого ключа соединен с анодом первого диода второго блока неравнозначности, в первом блоке неравнозначности анод первого диода соединен через кнопку с общей шиной, анод второго диода первого блока неравнозначности соединен с выходом второго ключа, обмотки считывания всех трансфлюксоров первого и второго блоков неравно значности соединены последовательно, введены К-2 (где К - число разрядов переобразуемого кода) блоков неравнозначности, коммутатор и 2К-4 ключей, причем во всё блоки неравнозначности, кроме первого, введены третьи конденсаторы, первая обкладка которых соединена с общей шиной, а вторая соединена с анодом седьмого диода и с шиной соответсвующе.го выходного сигнала, ВО всех блоках неравнозначности катод восьмого диода соединен с анодом шеетого диода, аноды пятых диодов введе ных блоков неравнозначности соедине с выходами соответствующих 2М-1 ключей (где М - номер блока неравнозна ности) , входы которых соединены с об щей шиной, а управляющие входы соединены с шиной М-го тактового сигнала, вторые выводы входных обмоток вт рых трансфлюксоров введенных блоков неравнозначности соединены соответственно с выходами 2М-ых ключей, упр ляющие входы которых соединены с Шинрй М-го тактового сигнала, входы 2М-ЫХ ключей соединены с М-ми переключающими контактами коммутатор, размыкающие контакты которого соединены с М-1 переключающим контактом а замыкающие контакты соедиены с ответствующими шинами параллельной входной информации, первый размыкающий 20 контакт переключателя сОедиен с шиной последовательной входной информации, анод второго диода К-го блока неравнозначности соединен с выходом первого ключа, аноды вторых диодов всех остальных М-ых блоков неравнозначности соединены с выходом 2М+1-го ключа, аноды первых диодов М-ых (кроме первого) блоков неравнозначности соединень с выходами 2М-3 ключей. На чертеже представлена схема преобразователя кода Грея в двоичный код и обратно. Преобразователь кода Грея в двоичный код и обратно содержит блоки 1 не равнозначности, в каждом из которых первый вывод обмотки 2 обнуления тран флюксора 3 подключен к катодам диодов 4 и 5, а второй вывод через обмотку 6 обнуления трансфлюксора .7 соединен с анодами диодов 8 и 9 и с первой обкладкой конденсатора 10, вторая обкладка которого соединена с общей ши ной, с первой обкладкой конденсатора П и с первым выводом входной обмотки 12 трансфлюксора 7, первый вывод вход ной обмотки 13 первого трансфлюксора соединен с катодом диода 14, первый с . , вывод выходной обмотки 1 Э ТраНСфЛЮКсора 3 соединен через выходную обмотк 16 трансфлюксора 7 с общей шиной и с первым выводом выходной обмотки 17трансфлюксора 7, второй вывод которой соединен с катодом диода 8 и с замыкающим контактом переключателя 18 переключающий контакт которого через диод 19 соединен со второй обкладкой конденсатора 11, а размыкающий контак 54 соединен с катодом диода 20 и со втО- рым выводом обмотки 15, анод диода 5 соединен с анодом диода 21, катод которого соединен с анодом диода 19, анод диода 20 соединен с первой обкладкой конденсатора 22 и с шиной 23 выходного сигнала, вторая обкладка конденсатора 22 соединена с общей шиной, анод диода 19 блока 1-М (где М - порядковый номер блока 1) соединен со вторым выводом обмотки 13 блока Ь-М+1, обмотки 24 считывания всех трансфлюксоров 3 и 7 всех блоков 1 соединены согласно и последовательно, аноды диодов 14 всех блоков 1 соединены соответственно с выходами ключей 24-2М-1, входы которых соединены с общей шиной, а управляющие входы соединены соответственно с шиной 25-М тактового сигнала, вторые выводы обмоток 6 соединены соответственно с выходами ключей 24-2М, управляющие входы которых соединены соответственно с шиной 25-М тактового сигнала, входы ключей 24-2М соединены С М-ми переключающими контактами коммутатора .26, размыкающие контакты которого соединены с М-1-ми переключающими контактами, а -замыкающие контакты соединены с соответствующими шинами 27 параллельной входной информации, первый размыкающий контакт коммутатора 26 соединен с шиной 28 последовательной входной информации, анод диода и блока 1-К соединен с выходом ключа 24-1, аноды диодов 4 остальных блоков 1 соединены с выходом ключа 24-2М+1, аноды диодов 7 всех блоков 1 ( кроме блока 1-1) соединены с выходами ключа 242М-3, анод диода 7 блок 1-1 соединен через кнопку 28 с общей шиной. Устройство может работать как в режиме преобразования кода Грея в двоичный код, так и в режиме обратного преобразования. I В оежиме Код Грея двоичный код контакты переключателей 18 находятся в положении, показанном на чертеже, В результате чего работа устройства подчиняетсй алгоритму , где Мцл - разряд двоичного кода; - разряд кода Грея; О -, знак сложения логической операции неравнозначность. В режиме Двоичный код- код Грея контакты переключателей 18 находятся 784 в обратном положении и работа устройства подчиняется алгоритму R-N,©N,-, , В обоих режимах перед началом работы устройства нажатием кнопки 28 осуществляется разряд конденсаторов 10 и 11 и производится блокировка трансфлюксоров 3 и 7 блока 1-1. Состояние же конденсаторов 10 и 11 и трансфлюксоров 3 и 7 остальных блоков 1 безразлично. Через шину 28 последовательной входной информации (старшими разряда ми вперед) или шины 27-1 - 27-К парал лельной входной информации на ключи 24- 2М поступают разря1ды переобразуемо го числа. Тактовыми сигналами с шины 25 обеспечивает последовательное открывание ключей 24, причем в первый момент открываются ключи 24, соединенные с бло ком 1-1, затем ключи 24 соединенные с блоком 1-2 и т.д. С открыванием ключа 24-2 сигнал, соответствующий старшему разряду преобразуемого кода R {или )jпоступает во входную обмотку 6 трансфлюксора 7 Если преобразуемый разряд равен 1, то указанный трансфлюксор разблокируется и заряжаются конденсаторы 10, 1 1 и 22 и на выходной шине 23-1 возникает отрицательный потенциал, соответствующий (или ). При этом ключ 24-1 с 24-2 обес печивает установку в исходное состо яние блока 1-2,.то есть разряд его конденсаторов 10 и 11 и блокировку его трансфлюксоров 3 и 7. С поступлением импульса на шину 25-2 открыва ются ключи 24-3 и 24-4. При этом разблокируется трансфлюксор 7 блока 1-2 если R. (или ), и разблокируетс трансфлюксор 3 блока 1-2, если был заряжен конденсатор И блока 1-1. На последовательно и встречно соединенных выходных обмотках 15 и 16 трансфлюксоров 3 и 7 блока 1-2 выполняется логическая операция Неравнозначность в результате чего заряжаются или не заряжаются конденсаторы 10, 11 и 22 блока 1-2 и потенциал на шине 23-2 определяет занчение N (или R , При этом обеспечивается установка блоков 2 1-3 блока 1-1 в исходное состояние При последующих тактах работа осталь ных блоков 1 аналогична. Результат преобразования фиксирует ся в виде заряда конденсаторов 22. В предлагаемом устро 1стве для гюьшения помехозащищенности боразорзания кодов чисел, поступающих друг за другом, предусмотрена возможность установки в исходное состояние блока 1(М+1) блока 1-(м-1) одновременно с преобразованием в блоке 1-М. Благоаря этому возможно преобразование последующего кода в устройстве без предварительной подачи на него обнуяющего сигнала и поскольку обнуление каждого разряда производится два раза в процессе преобразования, причем один раз непосре;г,сгвенно перед работойв каждом блоке 1 , зн чителыю повышена помехозащищенлость преобразователя,Формула изобретения Преобразователь кода Грея в двоичный код и обратно, содержащий два блока неравнозначности, в каждом из которых первый вывод обмотки обнуления первого трансфлюксорл под1а1Н)чен к катодам первого и второго диодов, а второй вывод через обмотку обнуления второго трансфлюксора соединен с анодани третьего и четвертого диодов и с первой обкладкой .первого конденсатора, вторая обкладка которого соединена с общей шиной с первой обютадкой второго конденсатора и с первым выводом входной .обмотки второго трансфлюксора, первый вывод входной обмотки первого трансфлюксора соединен с катодом пятого диода, первый вывод выходной o6MQTKn первого тра{;сфлюксора соединен через первую выходную об- . мотку второго трансфлюксора с общей шиной и с первым выводом второй выходной обмотки второго трансфлюксора, второй вывод которой соединен с катодом третьего диода и с замыкающим контактом первого переключателя, перекл1--чающий контакт которого через шестой диод соединен со второй обкладкой второго конденсатора, а размыкающий контакт соединен с. ка тодом седьмого диода и со вторым выводом выходной обмотки второго трансфлюксора, анод первого диода соединен с анодом восьмого диода, в первом блоке неравнозначности анод, седьмого диода соединен с первой шиной выходного сигнала и через третий конденсатор с общей шиной, анод шестого диода первого блока }геравноз11ачпосГи соединен со ВТОРЫМ вывел ом ну. (I.: ной обмотки первого трансфлюксора второго блока неравнозначности, аноды пятых диодов первого и второго блоков неравнозначности соединены соответстве но с выходами первого и второго ключей, входы которых соединены с общей шиной, а управляющие входы соединены соответственно с первой и второй шивходных обмоток вторых трансфлюксоро первого и второго блоков неравнознач ности соединены соответственно с выходами третьего и четвертого-ключей, управляющие входы которых соединены соответственно с шинами первого и вт рого тактовых сигналов, выход перво ключа соединен с анодом первого дио да второго блока неравнозначности, в первом блоке неравнозначности, анод первого диода соединен через кнопку общей шиной, анод второго диода первого блока неравнозначности соединен с выходом второго ключа, обмотки счи тывания всех трансфлюксоров первого и второго блоков неравнозначности соединены последовательно, отличающийся тем, что, с целью повьш1ения помехозащищенности, в него введены К-2 (где К - число разрядов преобразуемого кода) блоков неравнозначности коммутатор 2К-4 ключей, пр чем во все блоки неравнозначности, кроме первого, введены третьи конденсаторы, первая обкладка которых соединена с общей шиной, а вторая соединена с анодом седьмого диода и с шиной соответствующего выходного сигнала, во всех блоках неравнознач50. ности кода восьмого диода соединен с анодом шестого диода, аноды пятых диодов введенных блоком неравнозначности соединены с выходами соответствующих 2м-1 ключей (где М - номер блока неравнозначности), входы которых соединены с общей шиной, а управля ющие входы соединены с шиной М-го тактового сигнала, вторые выводы входных обмоток вторых трансфлюкторов введен- : ных блоков неравнозначности соединены соответственно с выходами 2М-ых ключей, управляющие входы которых соединены с шиной М-го тактового сигнала, входы 2М-ЫХ ключей соединены с М-ми переключающими контактами коммутатора размыкающие контакты которого соединены с М-1 переключающим контактом, а замыкающие контакты соединены с соответствующими шинами параллельной входное информации, первый размыкающий контакт переключателя соединен с шиной последовательно входной информации, анод второго диода К-го блока неравнозначности соединен с выходом первого ключа, аноды вторых диодов всех остальных М-ых блоков неравнознаности соединены с выходом 2М-1-го ключа, аноды первых диодов М-ых (кроме первого) блоков неравнозначности соединены с выходами 2М-3-ых ключей. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 661790, кл, Н 03 К 13/247, 16.02.77. 2,Авторское свидетельство СССР по заявке № 2607850 19.04.79.

Авторы

Даты

1981-06-30—Публикация

1979-04-09—Подача