первый, третий, второй и четвертый накопительные конденсаторы, а выходы пороговых.элементов соединены с соответствукмцими входами дешифратора .

2. Устройство по п.1, о т л ичающееся тем, что блок управления выполнен в виде формирователя импульса, вход которого соединен с кнопкой запуска, а выход .с первыми входами первого и второго триггеров, первым входом распределителя импульсов, входом обнуления регистра памяти и четвертым выходом блока управления, выход генератора тактовых импульсов подключен к первому входу элемента И, второй вход которого соединен с выходом первого триггера, а выход - с вторым входом распределителя импульсов, выходы с первого по шестой которого соединен с соответствукшщми входами шифратора, 1ыходы с первого по девятый которого соединены с соответствующшда входами регистра памяти и первой

01762

группы усилителей мощности, вторая группа усилителей мощности своими входами подключена к.первому по девятый выходам регистра памяти, I выходы усилителей мощности первой и второй групп подключены к шине второго выхода блока управления, выход переключателя амплитуды соединен с первым выходом блока управления, а выход переключателя типа транзистора соединен с третьим выходом блока управления, вход блока управления соединен с десятым входом регистра памяти, входом элемента НЕ, первым входом элемента ИЛИ и третьим входом распределителя импульсов, седьмой выход которого соединен с первым входом элемента И и вторым входом элемента ИЛИ. выход которого соединен с вторым входом первого триггера, второй вход элемента И соединен с выходом элемента НЕ, а выход - с вторым входом второго триггера, выход которого подключен к индикатору.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реакции на аварию в схеме управления потребителями электроэнергии | 1990 |

|

SU1795495A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| Многопостовое устройство для контроля параметров электронных схем | 1983 |

|

SU1108374A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Близостный переключатель | 1988 |

|

SU1539855A1 |

| УСТРОЙСТВО ПРИЕМА КОМАНД УПРАВЛЕНИЯ | 2002 |

|

RU2237287C2 |

| Устройство для сигнализации с индикацией местоположения аварийного объекта | 1982 |

|

SU1121689A1 |

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| ГЕНЕРАТОР ТЕСТОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2034399C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ | 2004 |

|

RU2282246C2 |

1. УСТРОЙСТВО ДЛЯ ПРЕДВАРИТЕЛЬНОЙ ПРОВЕРКИ ТРАНЗИСТОРОВ, содержащее коммутатор, три горизонталь ные шины которого соединены с блоком подключения транзистора, измеритель параметров, подключенный своими входами к первой, второй и третьей вертикальным шинам коммутатора, первый и второй накопительные конденсаторы, а также первый и второй диоды, причем катод первого диода соединен с анодом второго диода, от л ич а юще е ся тем, что, с целью расширения функциональных возможностей, в него введены генератор двухполярных импульсов, управляемый переключатель, два дополнительных диода и два дополнительных накопительных конденсатора, четьфе пороговых элемента, дешифратор, два триггера, два интегратора, блок сравнения,, элемент И и блок управления, при этом выход генератора двухполярных импульсов соединен с четвертой вертикальной шиной коммутатора, а его, вход - с первым выходом блока управления , шина второго выхода которого соединена с з равляющим входом коммутатора, пятая и шестая вертикальные шины которого соединены соответственно с первой и второй входными шинами управляемого переключателя, управляющий вход которого соединен с выходом первого триггера и первым входом элемента И, выход которого соединен с управляющим входом измерителя параметров и входом блока управления, третий выход котог рого соединен с управляющим входом дешифратора, первый, второй, третий и четвертый входы которого соединены с выходами соответственно первого, второго, третьего и четвертого пороговых элементов, а его выход с первым входом первого триггера, второй вход которого соединен с четвертым выходом блока управления и первым входом второго триггера, (Л выход которого соединен с вторым С входом элемента И, а второй вход с выходом блока сравнения, первый и второй входы которого соединены с выходами соответственно первого и второго интеграторов, входы которых подключены соответственно к первому и второму замыкающим выходным контактам управляемого переключателя, первый выходной размыкающий контакт которого соединен .с катодом третьего ч и анодом четвертого диодов, а вто35 рой выходной размыкающий контакт INO с катодом первого диода, анод которого подключен к входу первого порогового элемента, анод третьего диода подключен к входу второго порогового элемента, катоды второго и четвертого диодов подключены со- . ответственно к входам третьего и четвертого пороговых элементов, параллельно входам первого, второго, третьего и четвертого пороговых элементов подключены соответственно

Изобретение относится к измерению и контролю электрических параметров транзисторов и может быть использовано в установках, где возможны случаи неправильной ориентации транзисторов при включении их в измерительные позиции .

Известно устройство для классификации транзисторов, содержащее генератор импульсов,формкрователь импульсов, коммутатор, блок схем измерения, блок исполнителэншс устройств, пороговую схему, блок сопряжения, счётчик и схемы НЕ.

Данное устройГство осуществляет автоматическое подключение электродов испытуемого транзистора к схемам измерения и позволяет полностью автоматизировать процесс классификации транзисторов по коэффициенту усиления / О .

Однако в данном устройстве электроды испытуемого транзистора не определяются для однозначного под- ,

кЛючения его к блоку схем измерения остальных параметров транзистора. Кроме того, определение без однозначного подключения транзистора к блоку схем измерения может привести к ошибочному результату, так как у транзистора между коллекторным и эмиттерным переходами принципиальной разницы нет, поэтому он допускает инверсное включение. Для некоторых транзисторов, например II27 и П29, инверсньй коэффициент усиления входит в допуск прямого коэффициента усиления. Поэтому не исключена возможность классификации транзисторов по инверсному коэффициенту усиления, что снижает достоверность контроля. .

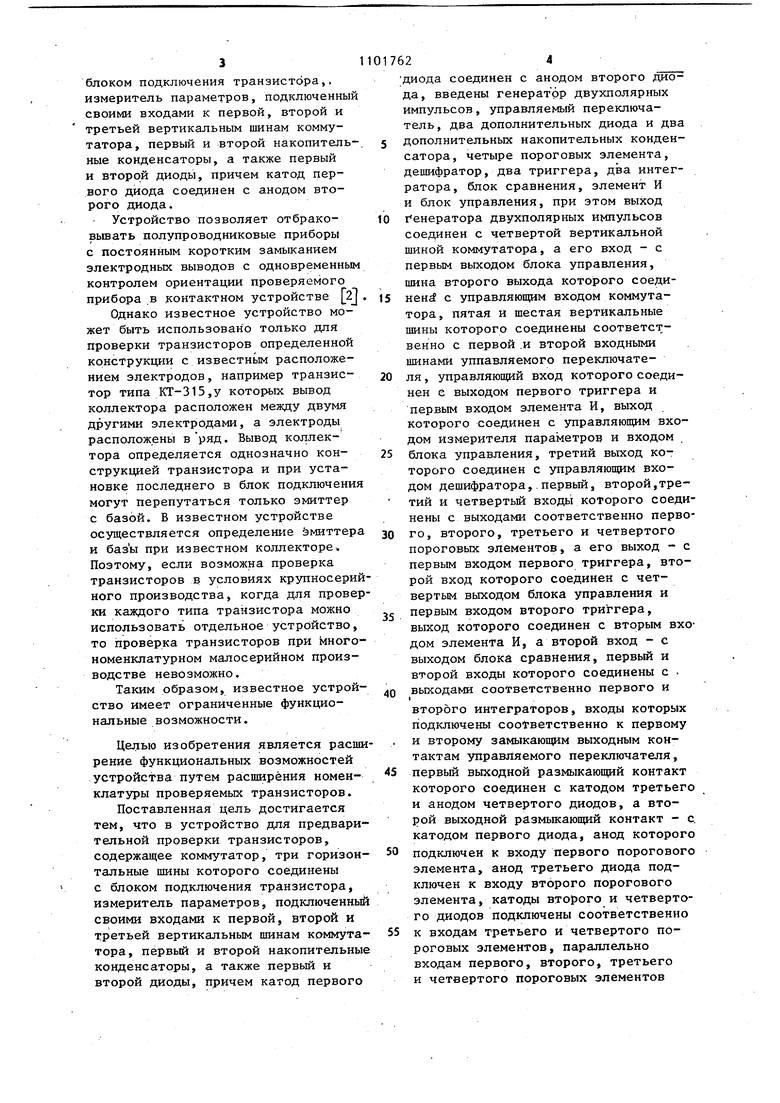

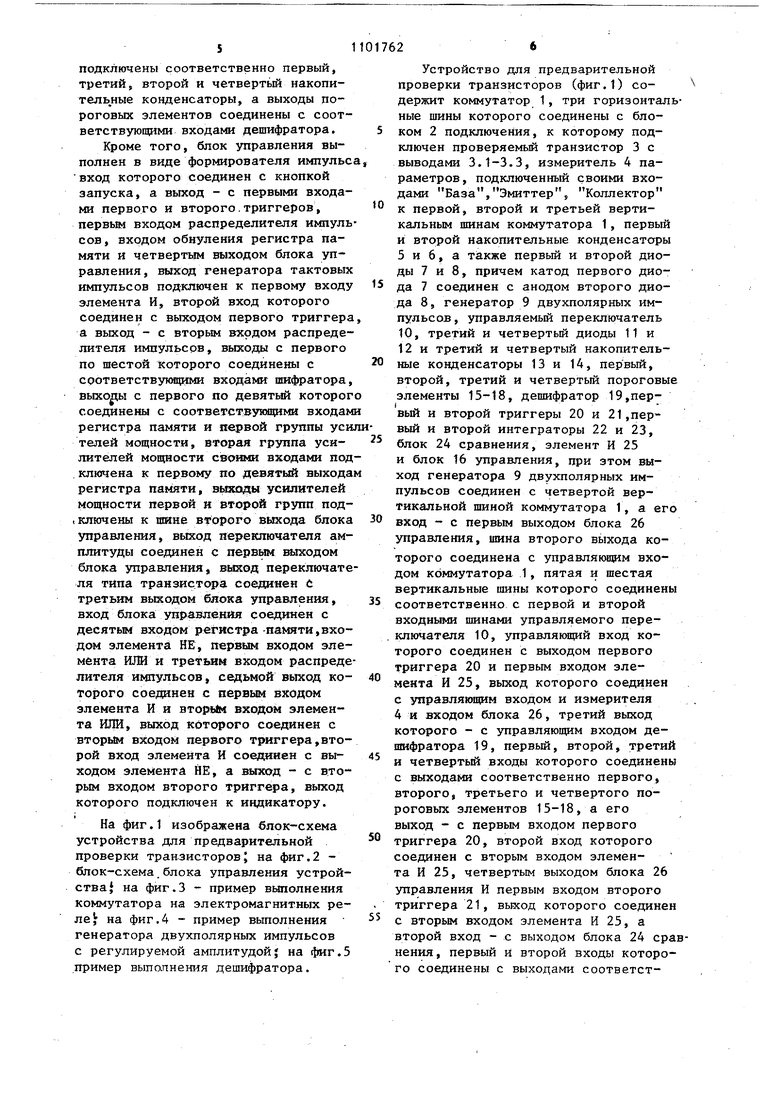

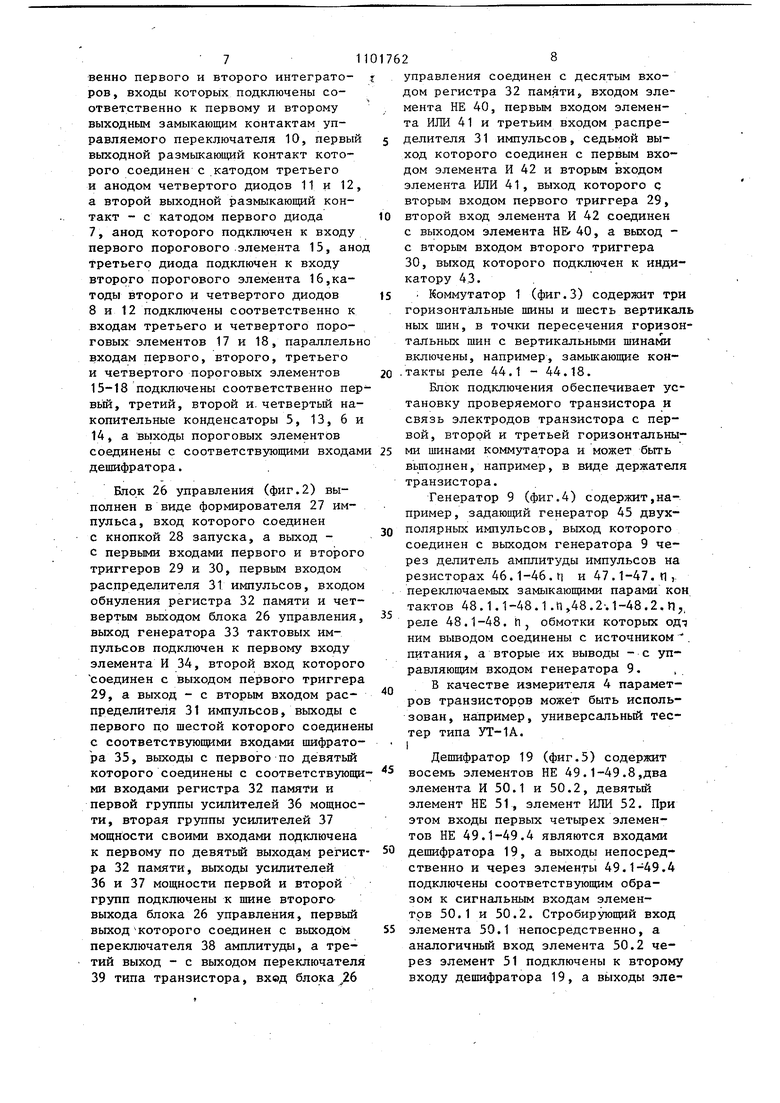

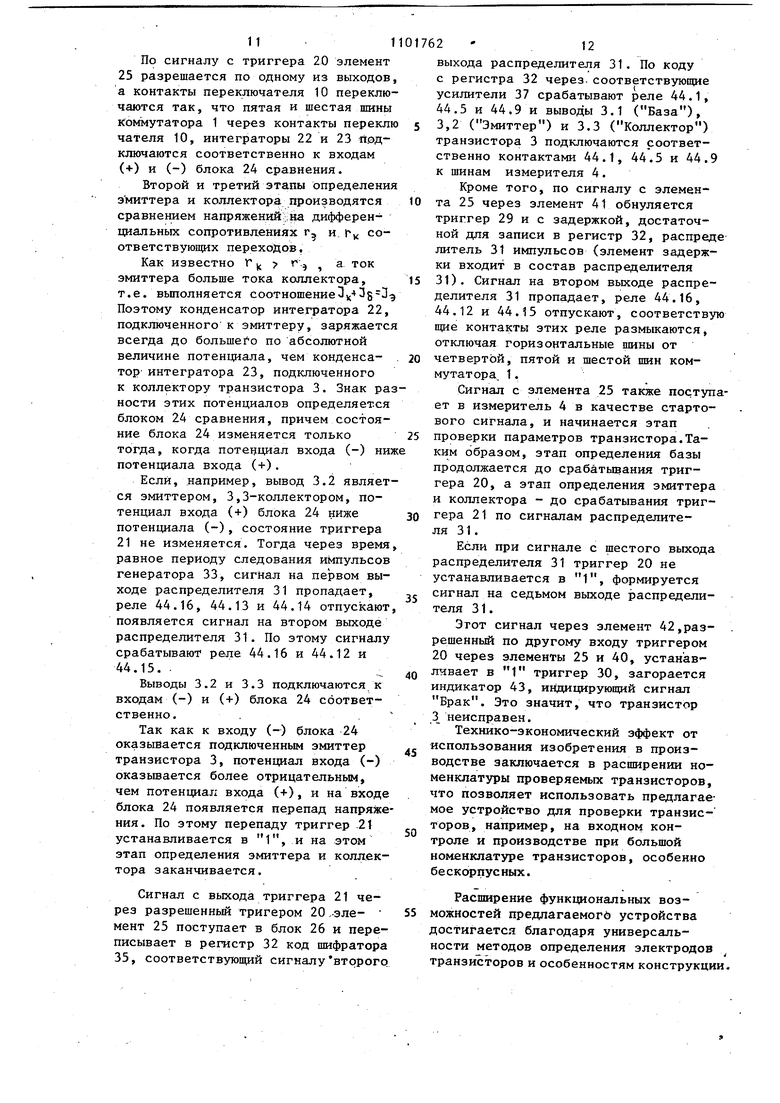

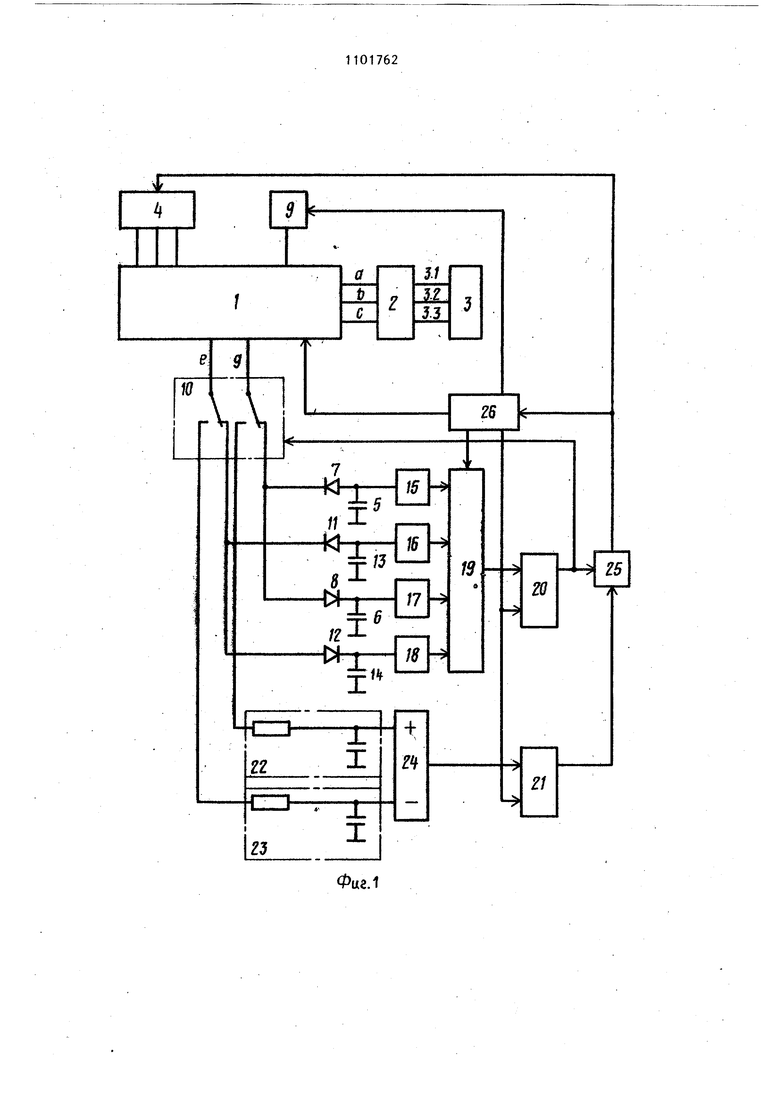

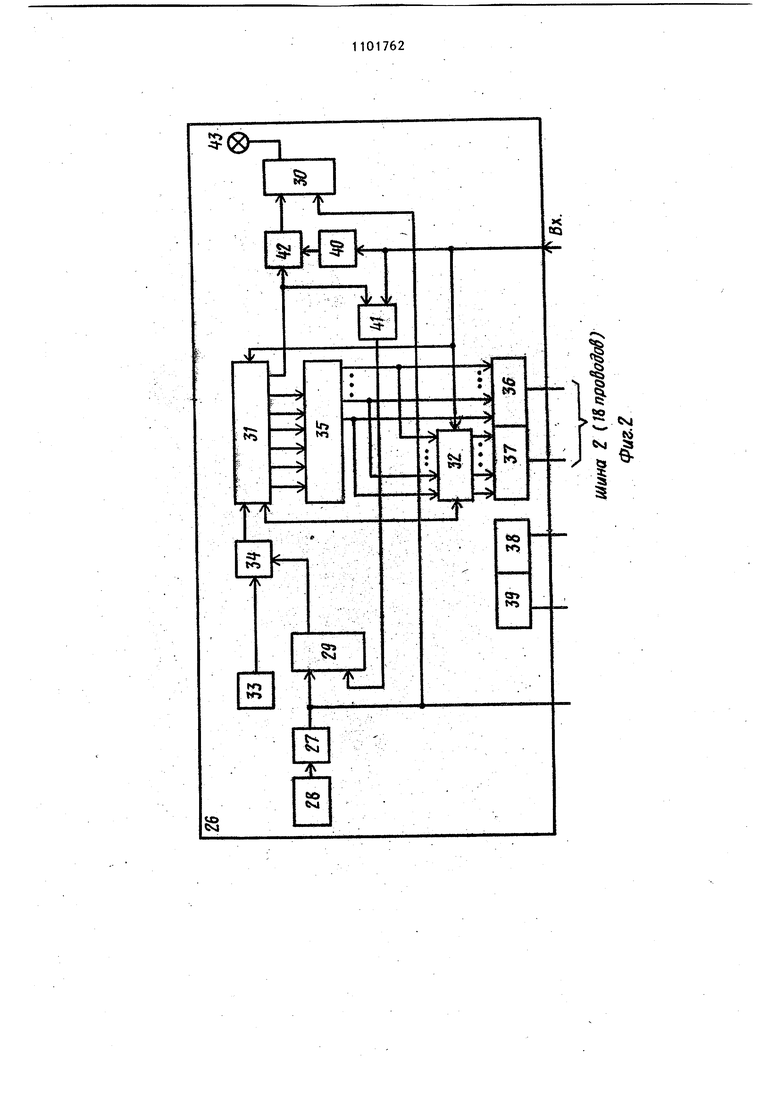

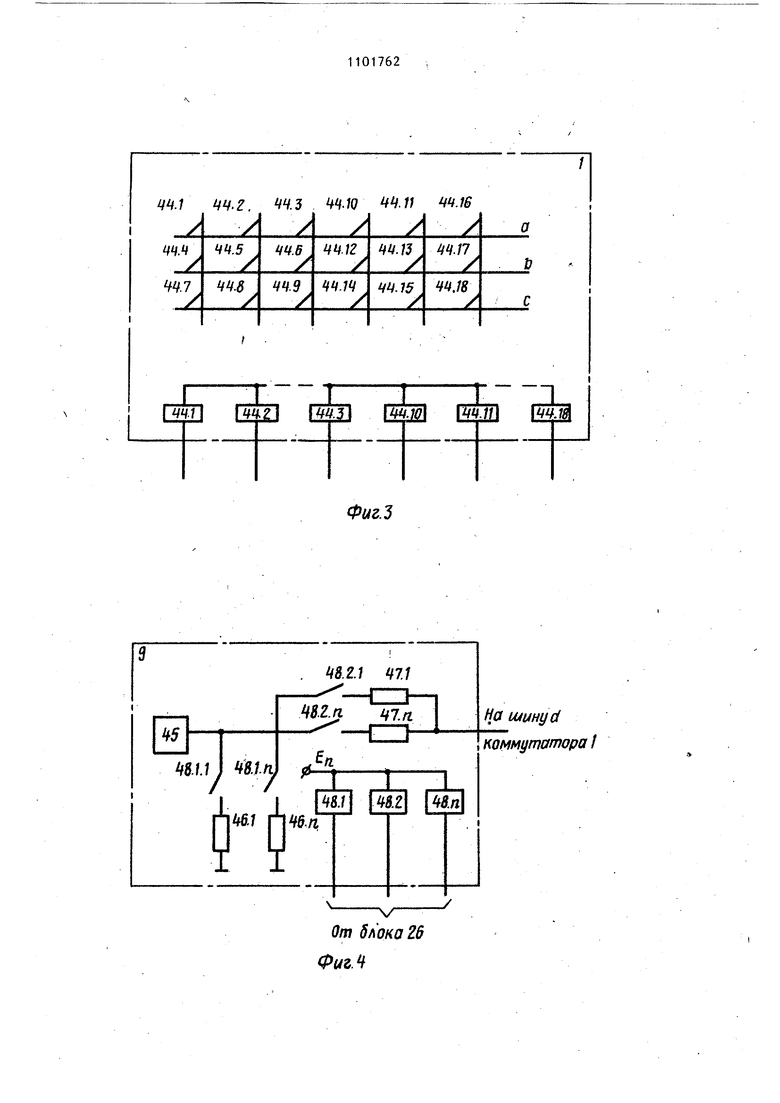

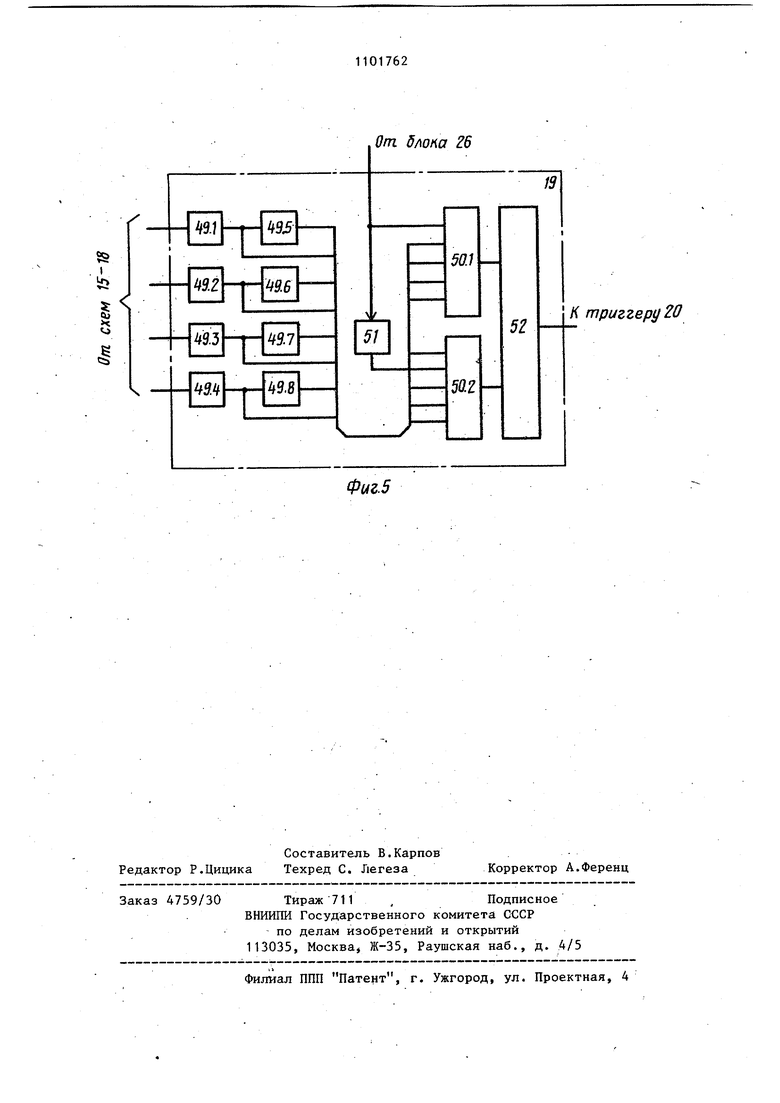

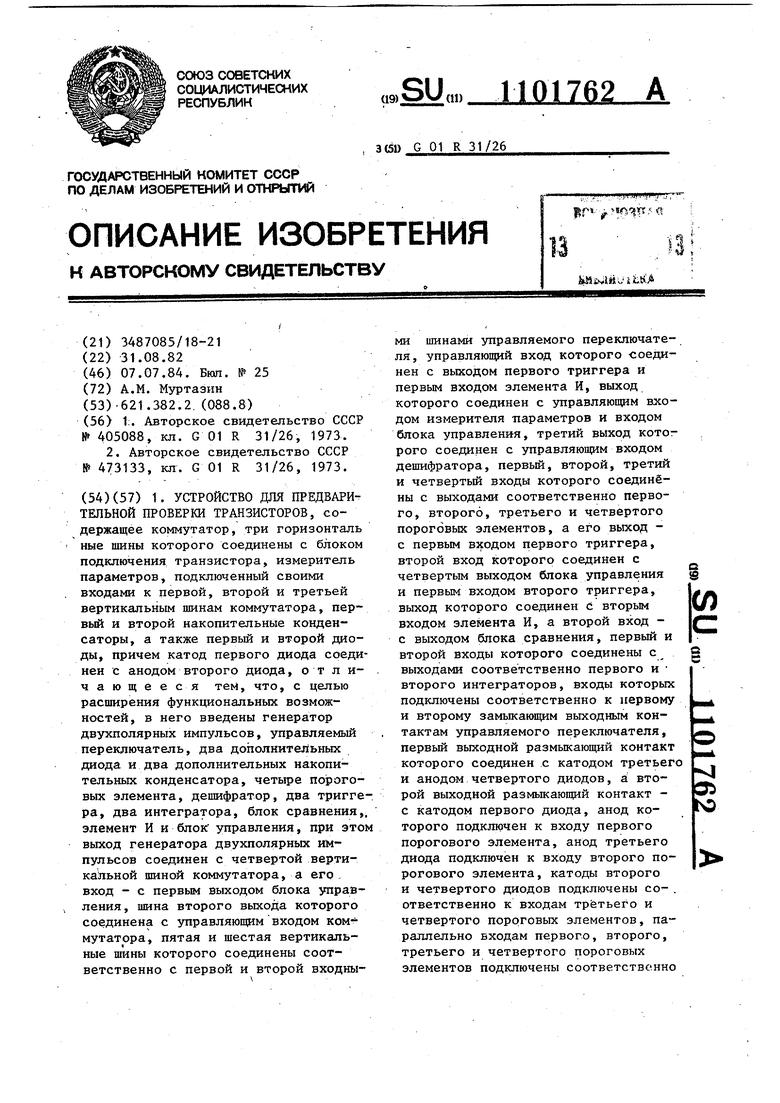

Наиболее близким к изобретению по технической сущности является устройство для предварительной проверки полупроводниковых приборов, содержащее коммутатор, три горизонтальйые шины которого соединены с 3 блоком подключения транзистора,, измеритель параметров, подключенны своими входами к первой, второй и третьей вертикальным шинам коммутатора, первый и второй накопитель ные конденсаторы, а также первый и второй диоды, причем катод первого диода соединен с анодом второго диода. Устройство позволяет отбраковьшать полупроводниковые приборы с постоянным коротким замыканием электродных выводов с одновременны контролем ориентации проверяемого прибора в контактном устройстве 2J Однако известное устройство может быть использовано только для проверки транзисторов определенной конструкции с известным расположением электродов, например транзистор типа КТ-315,у кото1)ых вывод коллектора расположен между двумя другими электродами, а электроды расположены вряд. Вывод коллектора определяется однозначно конструкцией транзистора и при установке последнего в блок подключени могут перепутаться только эмиттер с базой. В известном устройстве осуществляется определение эмиттер и базы при известном коллекторе. Поэтому, если возможна проверка транзисторов в условиях крупносери ного производства, когда для прове ки каждого типа транзистора можно использовать отдельное устройство, то проверка транзисторов при много номенклатурном малосерийном производстве невозможно. Таким образом, известное устрой ство имеет ограниченные функциональные возможности. Целью изобретения является расш рение функциональных возможностей устройства путем расширения номенклатуры проверяемых транзисторов. Поставленная цель достигается тем, что в устройство для предвари тельной проверки транзисторов, содержащее коммутатор, три горизон тальные шины которого соединены с блоком подключения транзистора, измеритель параметров, подключенны своими входами к первой, второй и третьей вертикальным шинам коммута тора, первый и второй накопительны конденсаторы, а также первый и второй диоды, причем катод первого 24 диода соединен с анодом второго диода, введены генератор двухполярных импульсов, управляемый переключатель, два дополнительных диода и два дополнительных накопительных конденсатора, четыре пороговых Элемента, дешифратор, два триггера, два интегратора, блок сравнения, элемент И и блок управления, при этом выход Генератора двухполярных и myльcoв соединен с четвертой вертикальной шиной коммутатора, а его вход - с первым выходом блока управления, шина второго выхода которого соединенй с управляющим входом коммутатора, пятая и шестая вертикальные шины которого соединены соответственно с первой .и второй входными шинами уппавляемого переключателя, управляющей вход которого соединен с выходом первого триггера и первым входом элемента И, выход которого соединен с управляющим входом измерителя параметров и входом блока управления, третий выход которого соединен с управляющим входом дешифратора,.первый, второй,третий и четвертьй входы которого соединены с выходами соответственно первого, второго, третьего и четвертого пороговых элементов, а его выход - с первым входом первого триггера, второй вход которого соединен с четвертым выходом блока управления и первым входом второго триггера, выход которого соединен с вторым входом элемента И, а второй вход - с выходом блока сравнения, первый и второй входы которого соединены с . выходами соответственно первого и второго интеграторов, входы которых подключены cootBeTCTBeHHo к первому и второму замыкающем выходным контактам управляемого переключателя, первый выходной размыкающий контакт которого соединен с катодом третьего и анодом четвертого диодов, а второй выходной размыкающий контакт - с, катодом первого диода, анод которого подключен к входу первого порогового элемента, анод третьего диода подключен к входу второго порогового элемента, катоды второго и четвертого диодов подключены соответственно к входам третьего и четвертого пороговых элементов, параллельно входам первого, второго, третьего и четвертого пороговых элементов подключены соответственно первый, третий, второй и четвертьй накопительные конденсаторы, а выходы пороговых элементов соединены с соответствующими входами дешифратора. Кроме того, блок управления выполнен в виде формирователя импульс вход которого соединен с кнопкой запуска, а выход - с первыми входами первого и второго.триггеров, первьа входом распределителя импуль сов, входом обнуления регистра памяти и четвертым выходом блока управления, выход генератора тактовых импульсов подключен к первому входу элемента И, второй вход которого соединен с выходом первого триггера а выход - с вторым входом распределителя импульсов, выходы с первого по шестой которого соединены с соответствующими входами шифратора, выходы с первого по девятый которог соединены с соответствукмцими входам регистра памяти и первой группы уси телей мощности, вторая группа усилителей мощности CSQHEMH входами под ключена к первому по девятый выхода регистра памяти, выходы усилителей мощности первой и второй групп под,ключены к шине второго выхода блока управления, выход переютючателя амплитуды соединен с первым тапсодом блока управления, выход переключате ля типа транзистора соединен с третьим выходом блока управления, вход блока управления соединен с десятьи входом регистра -памяти,входом элемента НЕ, первым входом элемента ИЛИ и третьим входом распреде лителя импульсов, седьмой выход которого соединен с первым входом элемента И и вторым входом элемента ИЛИ, выход которого соединен с вторым входом первого триггера,второй вход элемента И соединен с выходом элемента НЕ, а выход - с вторым входом второго триггера, выход которого подключен к индикатору. На фиг.1 изображена блок-схема устройства для предварительной проверки транзисторовJ на фиг.2 блок-схема.блока управления устройства J на фиг.З - пример выполнения коммутатора на электромагнитных реле на фиг.4 - пример выполнения генератора двухполярных импульсов с регулируемой амплитудой; на фиг.5 пример выпапнения дешифратора. Устройство для предварительной проверки транзисторов (фиг.1) содержит коммутатор 1, три горизонтальные шины которого соединены с блоком 2 подключения, к которому подключен проверяемьй транзистор 3 с выводами 3.1-3.3, измеритель 4 параметров, подключенный своими входами База,Эмиттер 5 Коллектор к первой, второй и третьей вертикальным шинам коммутатора 1, первый и второй накопительные конденсаторы 5 и 6, а также первый и второй диоды 7 и 8 , причем катод первого диода 7 соединен с анодом второго диода 8, генератор 9 двухполярных импульсов, управляемый переключатель 10, третий и четвертый диоды 11 и 12 и третий и четвертый накопительные конденсаторы 13 и 14, первый, второй, третий и четвертый пороговые элементы 15-18, дешифратор 19,первый и второй триггеры 20 и 21,первый и второй интеграторы 22 и 23, блок 24 сравнения, элемент И 25 и блок 16 управления, при этом выход генератора 9 двухполярных импульсов соединен с четвертой вертикальной шиной коммутатора 1, а его вход - с первым выходом блока 26 управления, шина второго выхода которого соединена с управляющим входом коммутатора 1, пятая и шестая вертикальные шины которого соединены соответственно с первой и второй входными шинами управляемого переключателя 10, управлянлций вход которого соединен с выходом первого триггера 20 и первым входом элемента И 25, выход которого соединен с управляющим входом и измерителя 4 и входом блока 26, третий выход которого - с 5шравляющим входом дешифратора 19, первый, второй, третий и четвертый входы которого соединены с выходами соответственно первого, второго, третьего и четвертого пороговых элементов 15-18, а его выход - с первым входом первого триггера 20, второй вход которого соединен с вторым входом элемента И 25, четвертым выходом блока 26 управления И первым входом второго триггера 21, выход которого соединен с вторым входом элемента И 25, а второй вход - с выходом блока 24 сравнения, первый и второй входы которого соединены с выходами соответст71венно первого и второго интеграторов, входы которых подключены соответственно к первому и второму выходным замыкающим контактам управляемого переключателя 10, первый выходной размыкающий контакт которого соединен с катодом третьего и анодом четвертого диодов 11 и 12, а второй выходной размьжающий контакт - с катодом первого диода 7, анод которого подключен к входу первого порогового элемента 15, ано третьего диода подключен к входу второго порогового элемента 16,катоды второго и четвертого диодов 8 и 12 подключены соответственно к входам третьего и четвертого пороговых элементов 17 и 18, параллельн входам первого, второго, третьего и четвертого пороговых элементов 15-18 подключены соответственно пер вый, третий, второй и. четвертьй накопительные конденсаторы 5, 13, 6 и 14, а выходы пороговых элементов соединены с соответствующими входам дешифратора. Блок 26 управления (фиг.2) выполнен в виде формирователя 27 импульса, вход которого соединен с кнопкой 28 запуска, а выход с первыми входами первого и второго триггеров 29 и 30, первым входом распределителя 31 импульсов, входом обнуления регистра 32 памяти и четвертым выходом блока 26 управления, выход генератора 33 тактовых импульсов подключен к первому входу элемента И 34, второй вход которого соединен с выходом первого триггера 29, а выход - с вторым входом распределителя 31 импульсов, выходы с первого по шестой которого соединен с соответствуюш 1ми входами шифратора 35, выходы с первого по девятый которого соединены с соответствующи ми входами регистра 32 памяти и первой грзпппы усилителей 36 мощности, вторая группы усилителей 37 мощности своими входами подключена к первому по девятьй выходам регист ра 32 памяти, выходы усилителей 36 и 37 мощности первой и второй групп подключены к шине второговыхода блока 26 управления, первый выход которого соединен с выходом переключателя 38 амплитуды, а третий выход - с выходом переключателя 39 типа транзистора, вход блока 26 2 управления соединен с десятым входом регистра 32 памяти, входом элемента НЕ 40, первым входом элемента ИЛИ 41 и третьим входом распределителя 31 импульсов, седьмой выход которого соединен с первым входом элемента И 42 и вторым входом элемента ИЛИ 41, выход которого с вторым входом первого триггера 29, второй вход элемента И 42 соединен с выходом элемента Н& 40, а выход с вторым входом второго триггера 30, выход которого подключен к индикатору 43. . Коммутатор 1 (фиг.З) содержит три горизонтальные шины и шесть вертикаль ных шин, в точки пересечения горизонтальных шин с вертикальными шинами включены, например, замыкающие контакты реле 44.1 - 44.18. Блок подключения обеспечивает установку проверяемого транзистора и связь электродов транзистора с первой, второй и третьей горизонтальными шинами коммутатора и может быть выполнен, например, в виде держателя транзистора. Генератор 9 (фиг.4) содержит,например , задающий генератор 45 двухполярных импульсов, выход которого соединен с выходом генератора 9 через делитель амплитуды импульсов на резисторах 46.1-46. Г| и 47.1-47. И,. переключаемых замыкающими парами кон тактов 48 .1.1 -48.1 . П ,48 .2-. 1 -48 .2. П,, реле 48.1-48. h, обмотки которых одт ним выводом соединены с источником . питания, а вторые их выводы - с управляющим входом генератора 9. В качестве измерителя 4 параметров транзисторов может быть использован, налример, универсальньй тестер типа УТ-1А. I Дешифратор 19 (фиг.5) содержит восемь элементов НЕ 49.1-49.8,два элемента И 50.1 и 50.2, девятый элемент НЕ 51, элемент ИЛИ 52. При этом входы первых четырех элементов НЕ 49.1-49.4 являются входами дешифратора 19, а выходы непосредственно и через элементы 49..4 подключены соответствующим образом к сигнальным входам элементов 50.1 и 50.2. Стробирующий вход элемента 50.1 непосредственно, а аналогичный вход элемента 50.2 через элемент 51 подключены к второму входу дешифратора 19, а выходы элв ментов 50.1 и 50.2 подключены к элементу 52, выход которого являет ся выходом дешифратора 19. Устройство для предварительной проверки транзисторов работает в три этапа следуюпщм образом. Первый этап - определение базы проверяемого транзистора. При опре делении базового электрода структу транзистора рассматривается как дв элементарных р- п перехода (диода) включенньт встречно, у которых средняя точка является электродом базы. Если на базу транзистора р-п-р 1И-.йтипа подают отрицательные (положительные) импульсы, то на эмиттере и коллекторе появляются тольк отрицательные (положительные) импульсы. При подаче импульсов на эмиттер или коллектор на двух других электродах сигналы имеют разну полярность. В исходном положении устройства триггеры 20, 21, 29 и 30, распреде литель 31 импульсов, регистр 32 памяти-обнуляются, реле 44.1-44.18 48.1-48. п обесточиваются, индикатор 43 не зажигается элементы НЕ 40.1-50.4 открываются, а эле менты 50.1 и 50.2 запрещаются сигн лами с выходом элементов 49.5-49.8 соответственно. Через блок 2 подкл чают к горизонтальным шинам коммутатора 1 транзистор 3. Затем переключателем 39 задают тип структуры, например р-п-р кон |тролируемого транзистора 3. Элемент 50.1 разрешается по стробирую щему входу, элемент 50,2 по аналогичному входу запрещается сигналом с выхода элемента 51. Переключателем 38 задают амплитуду выходных импульсов генератора 9. По сигналу с переключателя 38 включается одно из реле 48.1-48. п J например реле 48.1 контакты 48.1 .1 и 48.2.1 замь1каютс и резисторы 46.1 и 47.1 образуют делитель амплитуды импульсов задающего генератора 45. Ток в импул се ограничивается резистором 47.1. Так обеспечивается необходимая и допустимая мощность воздействующих на транзистор 3 импульсов. Амплитуда импульсов генератора 9 выбирается, исходя из минимального ток базы проверяемого транзистора 3. В случае проверки транзисторов с примерно одинаковыми по техническим условиям минимальными токами базы амплитуда импульсов генератора 9 постояннаГи равна, примерно, 0,7В. Далее нажимают кнопку 28 в блоке 26 управления. При этом срабатывает формирователь 27, который передним фронтом подтверждает нулевое состояние распределителя 31 импульсов, триггеров 20, 21 и 30, а задним - устанавливает триггер 29 в состояние, при котором элемент 34 разрешается, в результате импульсы с генератора 33 тактовых импульсов поступают на вход распределителя 31 импульсов. По первому импульсу генератора 33 появляется сигнал на первом выходе распределителя 31 импульсов . По этому сигналу шифратор 35 формирует код, поступающий через усилитель 36 на обмотки реле 44.16, 44.13 и 44.14 коммутатора 1. Эти реле срабатывают, замыкая своими контактами шины с четвертой по шестую коммутатора 1 с его горизонтальными шинами.. Двухполярные импульсы задающего генератора 9 поступают через Замкнутые шины коммутатора 1 на вьшод 3.1 контролируемого транзистора 3. Два других вьшода транзистора 3 подключаются соответственно через контакты реле 44.13 и 44.14, пятую и лпестую шины коммутатора и контакты перекпюча- еля 10, диоды 7 и 11 к накопительным конденсаторам 5 и 13 и пороговым элементам 15 и 16, а через диоды 8 и 12 - к накопительным конденсаторам 6 и 14. t- Если вьшод 3.1 оказывается базовым электродом, то на выводах 3.2 и 3.3 появляются импульсы отрицатель ной полярности. Через диоды 7 и 11 происходит перезаряд конденсаторов 5 и 13, и на них образуется отрицательный потенциал. Пороговые элементы 15 и 16 срабатывают. Элементы 49.1 и 49.2 закрываются, а 49.5 и 49.6 открываются. Элемент 50.1 разрешается по всем пяти входам, и сигнал с его выхода через элемент ИЛИ 52 устанавливает в 1 триггер 20. На этом этап определения базы.заканчивается, и начинйется определение эмиттера и колектора. 111 По сигналу с триггера 20 элемент 25 разрешается по одному из выходов а контакты переключателя 10 переключаются так, что пятая и шестая шины коммутатора 1 через контакты переклю чателя 10, интеграторы 22 и 23 подключаются соответственно к входам (ь) и (-) блока 24 сравнения. Второй и третий этапы определения эмиттера и коллектора производятся сравнением напряжений;;на дифференциальных сопротивлениях г и, 1 соответствующих переходов. Как известно Т , - г , а ток эмиттера больше тока коллектора, т.е. вьтолняется соотношениеЗ - Зз Зд Поэтому конденсатор интегратора 22, подключенного к эмиттеру, заряжаетс всегда до большего по абсолютной величине потенциала, чем конденсатор интегратора 23, подключенного к коллектору транзистора 3. Знак ра ности этих потенциалов определяется блоком 24 сравнения, причем состояние блока 24 изменяется только тогда, когда потецциал входа (-) ни потенциала входа (+). Если, например, вывод 3.2 являет ся эмиттером, 3,3-коллектором, потенциал входа (+) блока 24 ниже потенциала (-), состояние триггера 21 не изменяется. Тогда через время равное периоду следования импульсов генератора 33, сигнал на первом выходе распределителя 31 пропадает, реле 44.16, 44.13 и 44.14 отпускают появляется сигнал на втором выходе распределителя 31. По этому сигналу срабатывают реле 44.16 и 44.12 и 44.15. . Выводы 3.2 и 3.3 подключаются к входам (-) и (+) блока 24 соответственно. .. Так как к входу (-) блока 24 оказывается подключенным эмиттер транзистора 3, потенциал входа (-) оказьшается более отрицательньм, чем потенциал входа (+), и на входе блока 24 появляется пе:репад напряже ния. По этому перепаду триггер 2t устанавливается в 1, и на этом этап определения эмиттера и коллектора заканчивается. Сигнал с выхода триггера 21 через разрешенный тригером 20 ,-элемент 25 поступает в блок 26 и переписывает в регистр 32 код шифратора 35, соответствующий сигналувторого 2 выхода распределителя 31. По коду с регистра 32 через, соответствующие усилители 37 срабатывают реле 44.1, 44.5 и 44.9 и выводы 3.1 (База), 3,2 (Эмиттер) и 3.3 (Коллектор) транзистора 3 подключаются соответственно контактами 44.1, 44.5 и 44.9 к шинам измерителя 4. Кроме того, по сигналу с элемента 25 через элемент 41 обнуляется триггер 29 и с задержкой, достаточной для записи в регистр 32, распреде литель 31 импульсов (элемент задержки входит в состав распределителя 31). Сигнал на втором выходе распределителя 31 пропадает, реле 44.16, 44.12 и 44.15 отпускают, соответствую щие контакты этих реле размыкаются, отключая горизонтальные шины от четвертой, пятой и шестой шин коммутатора. 1. Сигнал с элемента 25 также поступает в измеритель 4 в качестве стартового сигнала, и начинается этап проверки параметров транзистора.Таким образом, этап определения базы продолжается до срабатывания триггера 20, а этап определения эмиттера и коллектора - до срабатывания триггера 21 по сигналам распределителя 31. Если при сигнале с шестого выхода распределителя 31 триггер 20 не устанавливается в 1, формируется сигнал на седьмом выходе распределителя 31. Этот сигнал через элемент 42,раз- . решенный по другому входу триггером 20 через элементы 25 и 40, устанавливает в 1 триггер 30, загорается индикатор 43, ивдицирующий сигнал Брак. Это значит, что транзистор 3 неисправен. Технико-экономический эффект от использования изобретения в производстве заключается в расширении номенклатуры проверяемых транзисторов, что позволяет использовать предлагаемое устройство для проверки транзисторов, например, на входном контроле и производстве при большой номенклатуре транзисторов, особенно бескорпусных. Расширение функциональных возможностей предлагаемого устройства достигается благодаря универсальности методов определения электродов транзисторов и особенностям конструкции.

Фиг.1

Фиг.З

5

п.

щи I 8.Ш

|4б.г

На utuHyd коммутатора /

От блока 26 Фиъ.

/

§

i

I

К триггеру 20

Фиг.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU405088A1 | |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство предварительной проверки полупроводниковых приборов | 1973 |

|

SU473133A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-07-07—Публикация

1982-08-31—Подача