1

Изобретение относится к вычисли тельной технике, в частности к запо. минающим устройствам (ЗУ), где уп- равляющий сдвиговый регистр может быть составной частью ЗУ последовательного действия, основным назначением которого является сбор и передача высокоскоростной информации, совмещение цифровых устройств с различной пропускной способностью и т.д.

Известны управляющие сдвиговые регистры для бункерного ЗУ, содержащие триггерные регистры с логическими схемами в цепях связи ГО

Наиболее близким по технической сущности к предлагаемому является регистр, который содержит одноступен чатый триггерный регистр с тремя фазовыми вентилями-схемами И в цепях связи Т.

Недостатками регистра являются большие аппаратурные затраты и сложное структурное выполнение.

Логическая структура такого регистра удобна для реализации на МДП-транзисторах, позволяющих реализовать кратковременное динамическое хранение заряда в узлах структуры. Однако она не может быть реализована на структурах с биполярными транзисторами, например транзисторно-транзисторной логике или инжекционной логике, необладающими указанным свойством.

Цель изобретения - упрощение регистра сдвига.

Поставленная цель достигается тем, что в регистре сдвига, содержащем ячейки памяти, каждая из которых выполнена на первом триггере и первом элементе И, выход которого соединен с одним из входов первых триггеров данной и предьщущей ячеек памяти, другой вход первого триггера каждой ячейки памяти подключен к выходу первого элемента И последующей ячейки памяти, один из входов первого элемента И каждой ячейки памяти соединен с первой тактовой шиной, и.-вторую тактовую шину, в каждую ячейку памяти введены второй , второй итретий элементы И, певые входы которых соединены с выходами первого триггера данной ячейки памяти, другой вход первого элелемента И каждой ячейки памяти соединен, с прямым выходом второго триггера данной ячейки памяти, инверсный выход которого подключен к выходу данной ячейки памяти, входы .второго триггера каждой ячейки памяти подсоединены к выходам второго и третьего элементов И данной ячейки памяти, вторые входы второго и третьего элементов И каждой-ячейки памяти соединены.со второй тактовой шиной, третий вход второго элемента И подключен к одному из

входов третьего элемента И и прямому выходу первого триггера предыдущ ячейки памяти.

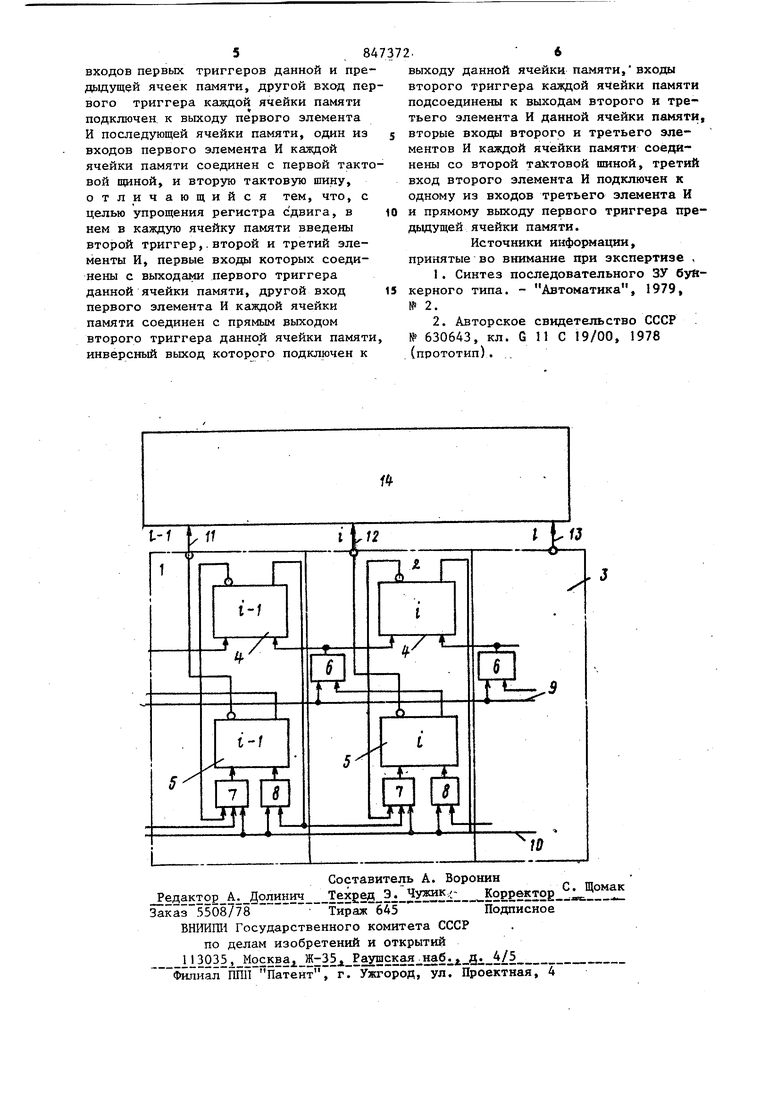

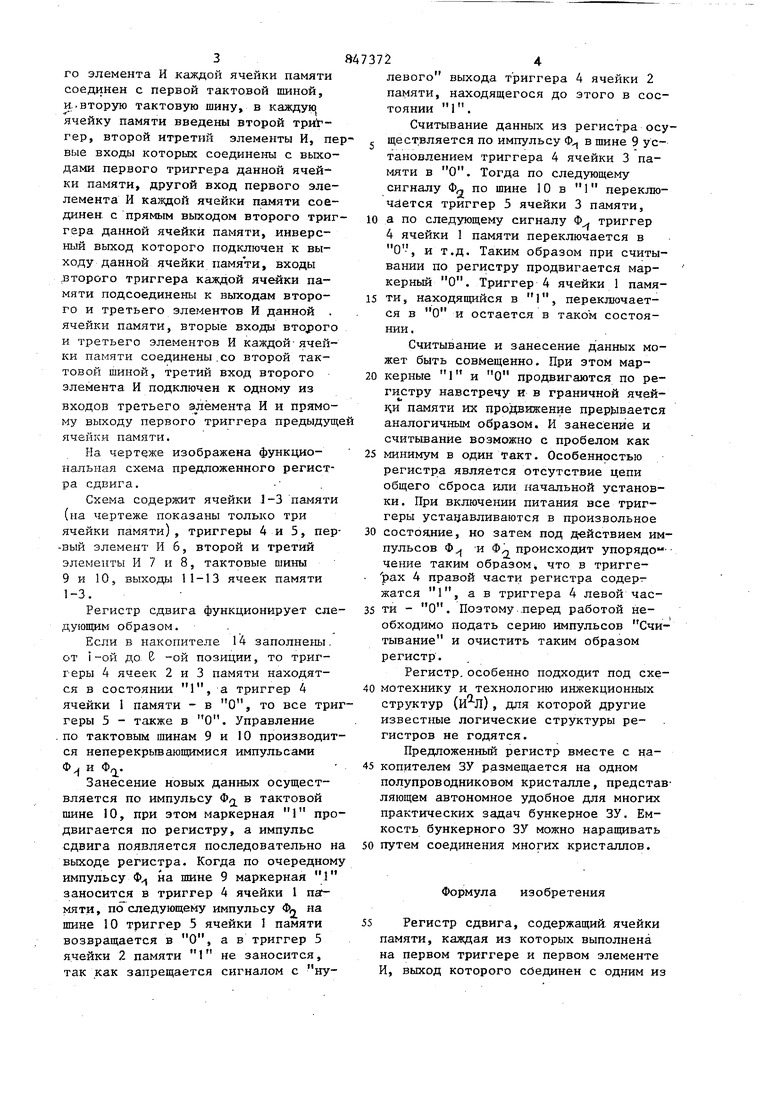

На чертеже изображена функциональная схема предложенного регистра сдвига.

Схема содержит ячейки ,1-3 памяти (на чертеже показаны только три ячейки памяти), триггеры 4 и 5, пер-вый элемент И 6, второй и третий элементы И 7 и 8, тактовые шины 9 и 10, выходы 11-13 ячеек памяти 1-3.

Регистр сдвига функционирует следующим образом.

Если в накопителе 14 заполнены. от i-ой до, В -ой позиции, то триггеры 4 ячеек 2 и 3 памяти находятся в состоянии 1, а триггер 4 ячейки 1 памяти - в О, то все тригеры 5 - также в О. Управление .по тактовым шинам 9 и 10 производится неперекрывающимися импульсами Фг.

Занесение новых данных осуществляется по импульсу OQ В тактовой шине 10, при этом маркерная 1 продвигается по регистру, а импульс сдвига появляется последовательно н выходе регистра. Когда по очередном импульсу Фх, на шине 9 маркерная 1 заносится в триггер 4 ячейки 1 па мяти, по следующему импульсу Ф на шине 10 триггер .5 ячейки 1 памяти возвращается в О, а в триггер 5 ячейки 2 памяти 1 не заносится, так как запрещается сигналом с нулевого выхода триггера 4 ячейки 2 памяти, находящегося до этого в состоянии 1.

Считывание данных из регистра осуществляется по импульсу Ф в шине 9 установлением триггера 4 ячейки 3 памяти в О. Тогда по следующему сигналу Фд по шине 10 в 1 переключается триггер 5 ячейки 3 памяти,

а по следующему сигналу Ф. триггер 4 ячейки 1 памяти переключается в О, и т.д. Таким образом при считывании по регистру продвигается маркерный О. Триггер 4 ячейки 1 памяти, находящийся в 1, переключается в О и остается в таком состоянии .

Считывание и занесение данных может быть совмещенно. При этом маркерные 1 и О продвигаются по регистру навстречу я в граничной ячейк;и памяти их продвижение прерывается аналогичным образом. И занесение и считьшание возможно с пробелом как

минимум в один такт. Особенностью регистра является отсутствие цепи общего сброса или начальной установки. При включении питания все триггеры устанавливаются в произвольное

состояние, но затем под д-ействием импульсов Ф -и Ф.2 происходит упорядо - чение таким образом что в триггеpax 4 правой части регистра содержатся 1, а в триггера 4 левой части - О. Поэтому..перед работой необходимо подать серию импульсов Считывание и очистить таким образом регистр.

Регистр, особенно подходит под схемотехнику и технологию инжекционных структур (ил), для которой другие известные логические структуры регистров не годятся.

Предложенный регистр вместе с накопителем ЗУ размещается на одном полупроводниковом кристалле, представляющем автономное удобное для многих практических задач бункерное ЗУ. Емкость бункерного ЗУ можно наращивать

путем соединения многих кристаллов.

Формула изобретения

55 Регистр сдвига, содержащий, ячейки памяти, каждая из которых выполнена на первом триггере и первом элементе И, выход которого соединен с одним из

входов первых триггеров данной и предыдущей ячеек памяти, другой вход первого триггера каждой ячейки памяти подключен, к выходу первого элемента И последующей ячейки памяти, один из входов первого элемента И каждой ячейки памяти соединен с первой тактовой щиной, и вторую тактовую шину, отличающийся тем, что, с целью упрощения регистра сдвига, в нем в каждую ячейку памяти введены второй триггер,.второй и третий элементы И, первые входы которых соединены с выходами первого триггера данной ячейки памяти, другой вход первого элемента И каждой ячейки памяти соединен с прямым выходом второго триггера данной ячейки памяти, инверсный выход которого подключен к

выходу данной ячейки памяти, входы второго триггера каждой ячейки памяти подсоединены к выходам второго и третьего элемента И данной ячейки памяти, вторые входы второго и третьего элементов И каждой ячейки памяти соединены со второй тактовой шиной, третий вход второго элемента И подключен к одному из входов третьего элемента И и прямому выходу первого триггера предьщущей ячейки памяти.

Источники информации, принятые во внимание при экспертизе ,

1.Синтез последовательного ЗУ буйкерного типа. - Автоматика, 1979,

№ 2.

2.Авторское свидетельство СССР № 630643, кл. G 11 С 19/00, 1978

. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор амплитудных распределений | 1984 |

|

SU1247894A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Устройство для обмена информацией | 1986 |

|

SU1363228A1 |

| Генератор тестов | 1987 |

|

SU1522213A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU873279A1 |

| Распределитель импульсов для многотактового запоминающего устройства на регистрах сдвига | 1978 |

|

SU752488A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1136173A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1990 |

|

SU1771533A3 |

Авторы

Даты

1981-07-15—Публикация

1979-10-16—Подача