Изобретение относится к области запоминающих устройств ЗУ и может быть использовано как составная час бункерного ЗУ, основным назначением которого является накопление высоко скоростной спорадической информации например в телеметрии, совмещение цифровых устройств с различными про пускными способностями и Т,П, Известен распределить импульсов для бункерного ЗУ с раздельными цепями сдвига в накопителе, содержащий двухступенчатый статический триг герный регистр р. . В указанном устройстве управление сдвигом в регистрах накопителя осуществляется от распределителя импульсов по раздельным цепям. Недостатком этого распределителя является неполная его асинхронность Наиболее близким из известных по технической сущности к предлагаемому является распределитель, содержащий первую и вторую группы триггеров, шины управления сдвигом, накопительные элементы 2 , К недостаткам этого распределителя следует отнести сложность структуры и низкое быстродействие по занесению информации ( в указанном известном устройстве высокое быстродействие достигнуто средствами особой технологии, но не оптимизацией структуры распределителя), Цель изобретения - повышение быстродействия и упрощение распределителя, Поставленная цель достигается тем, что в распределителе импульсов для многотактового регистрового запоминающего устройства на регистрах сдвига, содержащем две группы триггеров, накопительные элементы, например, первый и второй конденсаторы, одни из обкладок которых соединены с шиной нулевого потенциала, шину занесения информации и шины управления сдвигом, нулевой выход 1-го триггера первой группы соединен с нулевым входом i-ro триггера и единичным входом (1 + 1)-го триггера второй группы и с другой обкладкой первого конденсатора, нулевой выход 1-го триггера второй группы соединен с нулевым входом { - 1)-го триггера и единичным входом i-ro триггера первой группы, с.другой обкладкой второго конденсатора и 1-ой шиной управления сдвигом.

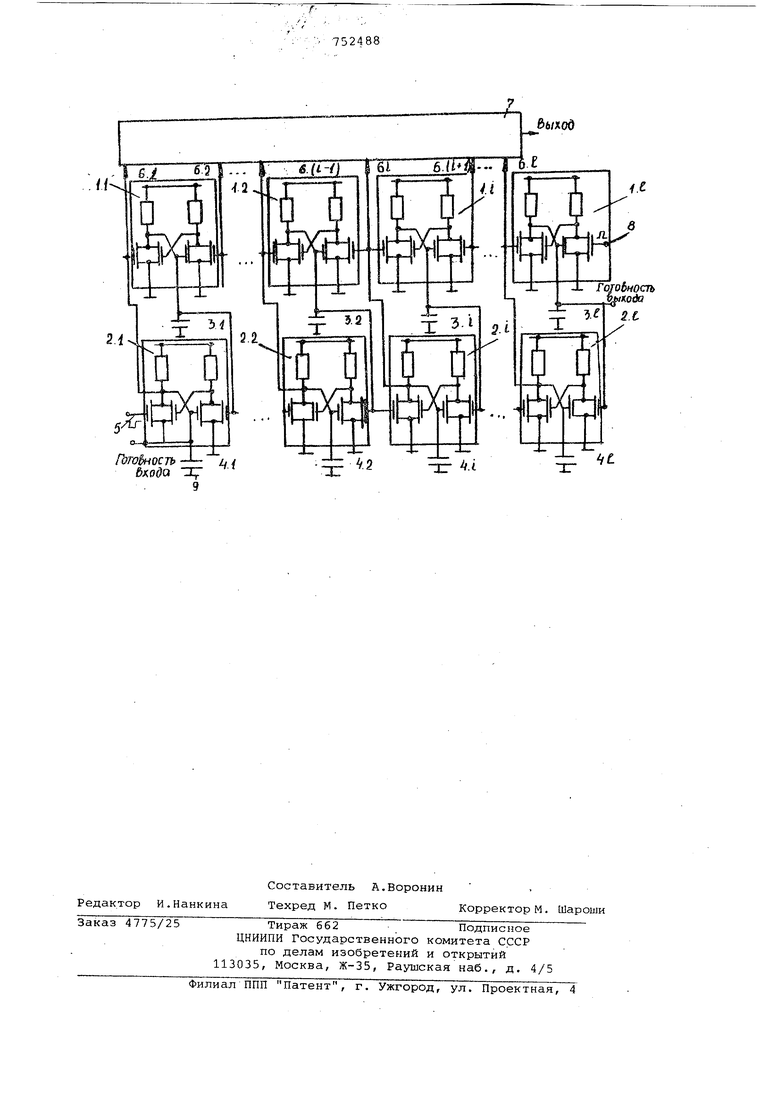

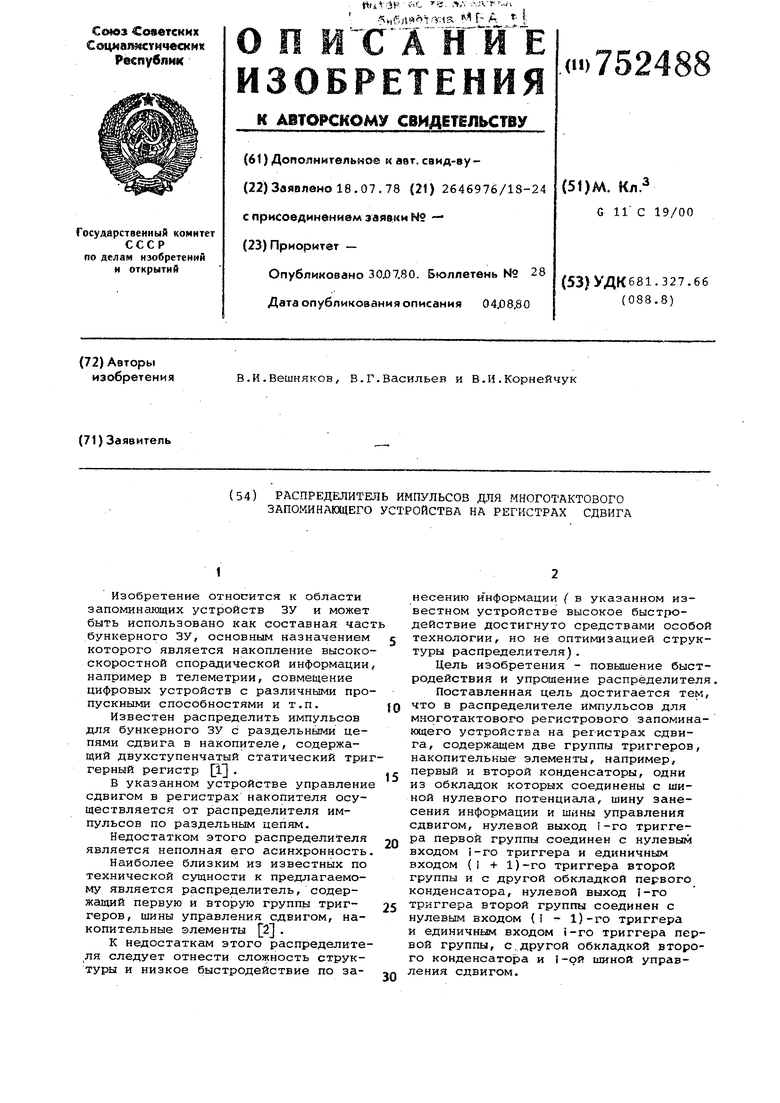

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит триггеры 1. 1.1-1 К первой группы, триггеры 2.1-2 0 второй группы, накопительные элементы, например, первые и вторые конденсаторы 3.1-3 Е- и 4.1-46, шину 5 занесения информации, шины 6.1-6 управления сдвигом, накопитель 7 регистрового ЗУ, шину 8 считывания, шину 9 нулевого потенциала.Каждый триггер выполнен на четырех ключевых МДПтранэисторах и других резисторах.

Накопитель 7 регистрового ЗУ состоит из одноступенчатых Е - разрядных ( или 6 -позиционных, где В - глубина бункера) сдвиговых регистров с раздельными шинами сдвига и содержит, кроме того, усилителей импульсов, входы которых подключены к соответствующим шинам управления сдвигом (на чертеже не показаны).

Распределительимпульсов работает следующим образом.

Первое слово выводится первым. По мере поступления новые данные продвигаются по регистрам накопителя 7 и занимают позиции вплотную к выходу Если в накопителе заполнены от 1-ой до 2 -ой позиции, то триггеры l.i-l.E распределителя установлены в 1 (на нулевых их выходах низкие потенциалы) , а триггеры 1.1-1.(( - 1) установлены в О. Триггеры 2.1-2(i - 1) при этом блокированы, так как на нулевых и единичных их входах высокие потенциалы, и соответственно на их. выходах низкие потенциалы. Триггеры

2.1 - 2. Е при этом установлены в II | II

Занесение нового информационного слова осуществляется подачей отрицательного импульса на шину 5 занесения информации. На нулевом выходе триггера 2.1 при этом с задержкой, определяемой узловой емкостью, появляется импульс, который производит занесение входного слова на первую позицию в накопителе 7 и устанавливает в 1 триггер 1.1. По окончании входного импульса на шине 5 триггер 2.1 переключается в 1. Отрицательным потенциалом на выходе триггера 1.1 переключается с защержкой в О триггер 2.2 и импульс действует по 2-ой цепи, управления сдвигом, производя при этом переключение с определе11ной задержкой триггера 1.1 в О а триггера 1.2 - в 1. Аналогично происходит дальнейшее последовательное возбуждение шин 6.1-6.Е,управления, маркерная 1 пробегает по распределителю слева направо, а усилители формируют импульсы по раздельным шинам сдвига в накопителе.-Когд им пульс управления действует на шине 6. i, то он переключает в 1 триг fep l.i и возвращает в О триггер

l.(i- 1). При этом длительность импульса обуславливается суммарной задержкой последовательного переключения цепочки элементов двух транзисторов триггера l.(i- 1) зарядом конденсатора 3.(i - 1) на его выходе, одного из транзисторов 2 триггера 2. и разрядом емкости на его выходе. Время задержки между возбуждениями двух соседних шин, например (i - 1)и i-ой, обуславливается задержкой на переключение одного транзистора 4 триггера 1.(i - 1), разрядом екости на его выходе, переключением одного транзистора 3 триггера 2.i и зарядомемкости на его выходе. Длительность импульса равна или немного больше времени задержки между импульсами на двух соседних шинах управления, а усилители отрабатывают входной сигнал с некоторой задержкой по заднему фронту, таким образом, что импульсы по шинам сдвига в накопителе частично перекрываются.

Если импульс действует на 6.() - 1)-ой шине, переключая триггер l.(i - 1) в 1, а триггер l.i уже находится в 1, то импульса на шине 61 не будет и триггер l.(i - 1 останется в 1. Это означает, что новое слово продвинулось по регистрам накопителя 7 на нужную позицию вплотную к ранее заполненным данным Занесение данных осуществляется асинхронно при наличии сигнала Готовность входа, указывающего на неполное заполнение бункера.

Считывание из ЗУ осуществляется подачей короткого положительного импульса на шину 8 при наличии информации в ЗУ, на что указывает сигнал Готовность выхода. При этом триггер 1. 6 переключается с некоторой задержкой в О, далее с некоторой задержкой переключается в О триггер 2.2 и на шине 6.6 действует импульс, производя сдвиг слова в накопителе let- 1-ой позиции в К- ую (на выход). При этом с задержкой переключается в О триггер 1 ( Е- 1) и возвращается в 1 триггер 1.С. Дальнейшее последовательное возбуждение шин управления сдвигом происходит аналогично и маркерный О пробегает по распределителю справа налево. Когда импульс действует на шине 6.i, то он переключает в О триггер l.(i - 1) и возвращает в 1 триггер 1.. Длительность импульсов при считывании формируется той же цепочкой элементов, что и при занесении, а задержка между импульсами двух соседних шин, например 6 i-ой и 6(i - 1)ой, обухзлавливается суммарной задержкой последовательного переключения .следующих элементов: двух транзисторов триггера l(i - 1) зарядом емкости на его выходе, переключением двух транзисторов триггера 2 (i- 1), а также зарядом емкости на его выходе. Это время больше, чем длительность импульса ( так как основная задержка за счет заряда ем кости), и последовательное возбужде ние шин управления сдвигом 6.8-6. при считывании и соответственно шин сдвига в накопителе происходит непе рекрывающимися импульсами. Если импульс действует на шине 6.i, устанавливая 6 О триггер l.(i - 1), а триггер l.(i - 2) нахо дится также в О, то импульса на ш не 6 . i - 1, не будет, и триггер l.(i - 1) останется в О. Это озна чает, что вес. массив данных в ЗУ сдвинулся на одну позицию к выходу. Считывание и занесение данных могут осуществляться асинхронно независимо одно от другого, возможно, например, одновременное считывание и занесение данных на разных частоTcix. При этом происходит встречное продвижение маркерных О и 1, а в нужном месте дальнейшее продвижение их прерывается, как и в рассмотренных случаях. Таким образом, предложенный распределитель осуществляет управление по раздельным шинам сдвига в накопителе: импульсы, пробегая справа Нсшево, в двух соседних шинах не перекрываются, что необходимо для исключения возможности сквозных переносов в накопителе, а импульсы, пробегающие слева направо, в двух соседних шинах частично перекрываются, но в этом случае ошибок не происходит, а быстродействие по занесению данных повышается, так как процессы сдвига информационного ело ва при этом частично совмещены. В предлагаемом распределителе импульсов достигнута высокаяскорос по занесению данных, что является о новным показателем для бункерного ЗУ. Структура распределителя проста и регулярна. Весь распределитель мультиплицирован, из единственного топологического фрагмента: статического R-S-триггера с подключенным к одному из его выходов конденсатором. Такой распределитель вместе с накопителем (структура которого так же регулярна) размещаются на одном полупроводниковом кристалле, представляющем автономное, удобное в применении, ЗУ. Из отдельных таких кристаллов можно свободно наращивать больШУЮ емкость ЗУ. Формула изобретения Распределитель импульсов для многотактового запоминающего устройства на регистрах сдвига, содержащий две группы триггеров, накопительные элементы, например, первый и второй конденсаторы, одни из обкладок которых соединены с шиной нулевого потенциала, шину занесения информации и шины управления сдвигом, отличающийся тем, что, с целью повышения быстродействия и упрощения устройства, в нем нулевой выход i-ro триггера первой группы соединен с нулевым входом i-ro триггера и единичнЕлм входом (i+ 1)-го триггера второй группы и с другой обкладкой первого конденсатора, нулевой выход i-ro триггера второй группы соединен с нулевым входом ({ - 1)-го триггера и единичным входом 1-го триггера первой группы, с другой обкладкой второго конденсатора и i-ой шиной управения сдвигом. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 630643, кл.С 11 С19/00, 01.08.76. 2. Электроника, 1976, 23, . 80-81 (прототип). дхода З 9 rofol HOcrb j| /xodo

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Управляющий регистр для буферного запоминающего устройства | 1987 |

|

SU1499405A1 |

| Регистр сдвига для буферного запоминающего устройства | 1985 |

|

SU1432609A1 |

| Регистр сдвига | 1979 |

|

SU847372A1 |

| Регистр для буферного запоминающего устройства | 1984 |

|

SU1170511A1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU809362A1 |

| Устройство для поиска максимального числа | 1985 |

|

SU1314334A1 |

| Блок управления для запоминающего устройства | 1975 |

|

SU637786A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-18—Подача