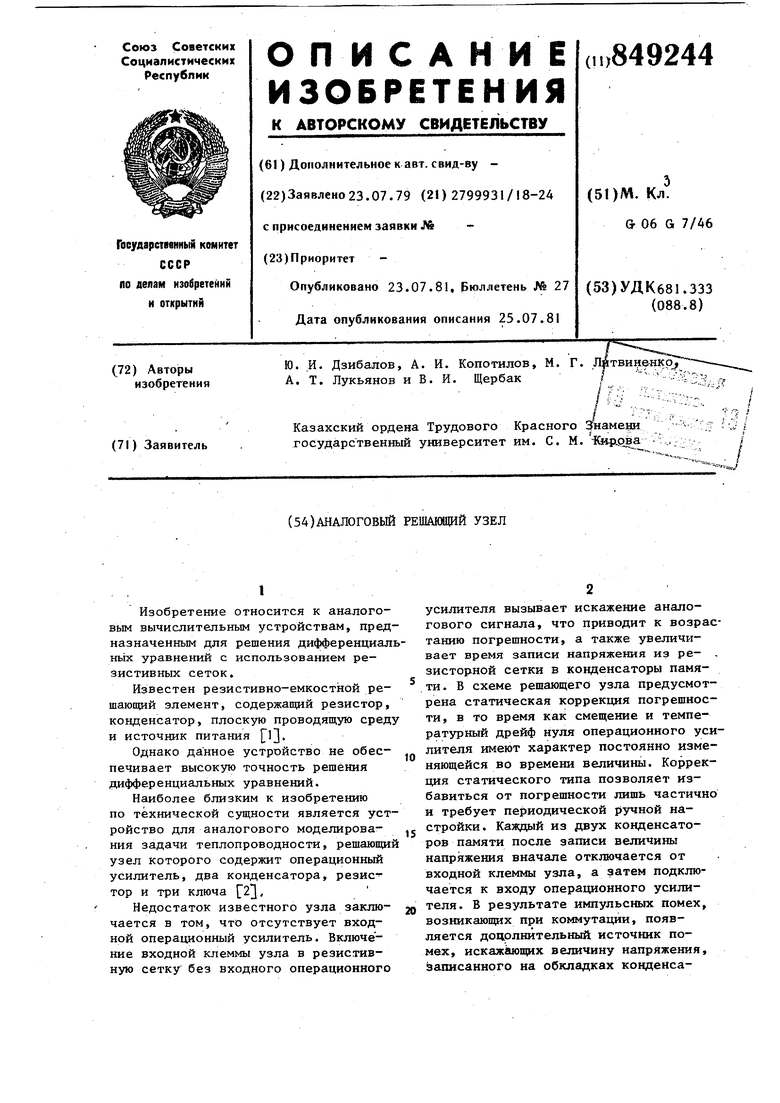

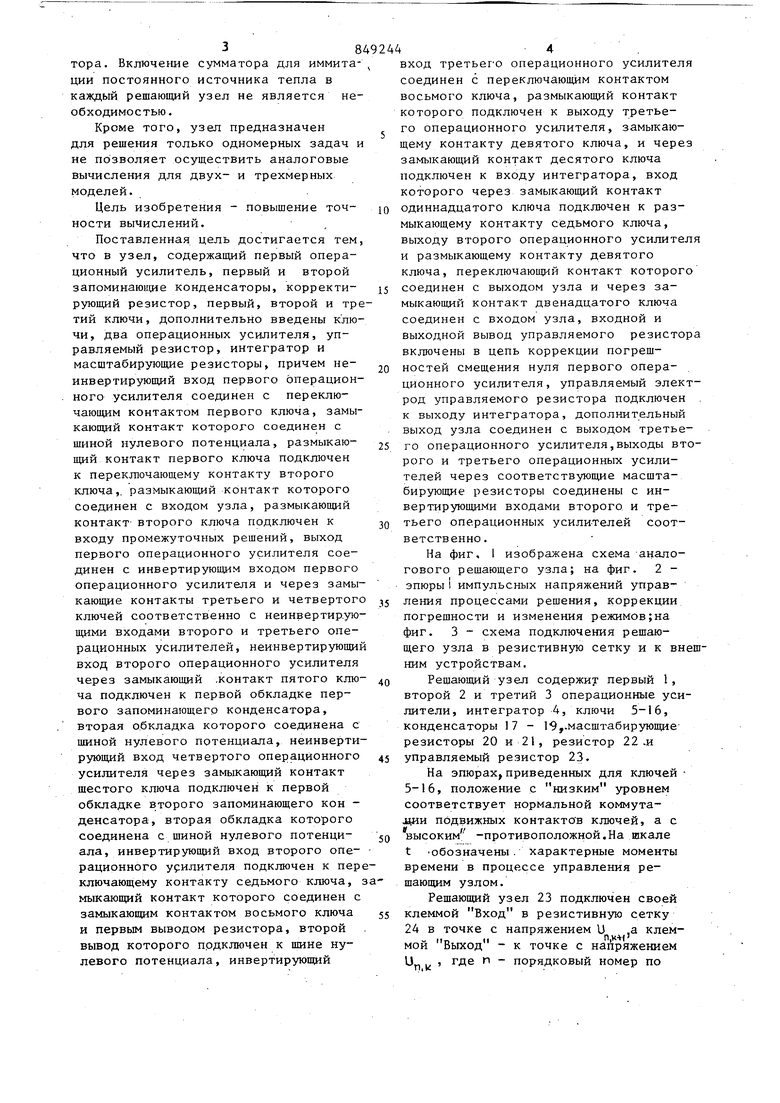

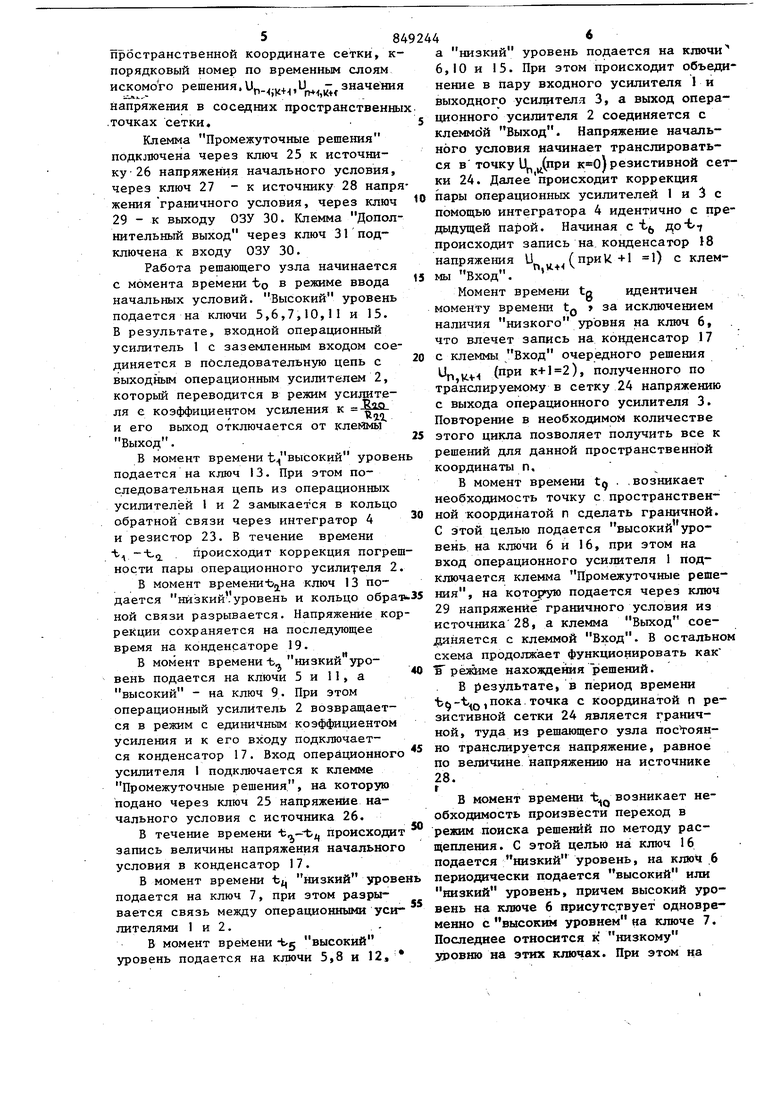

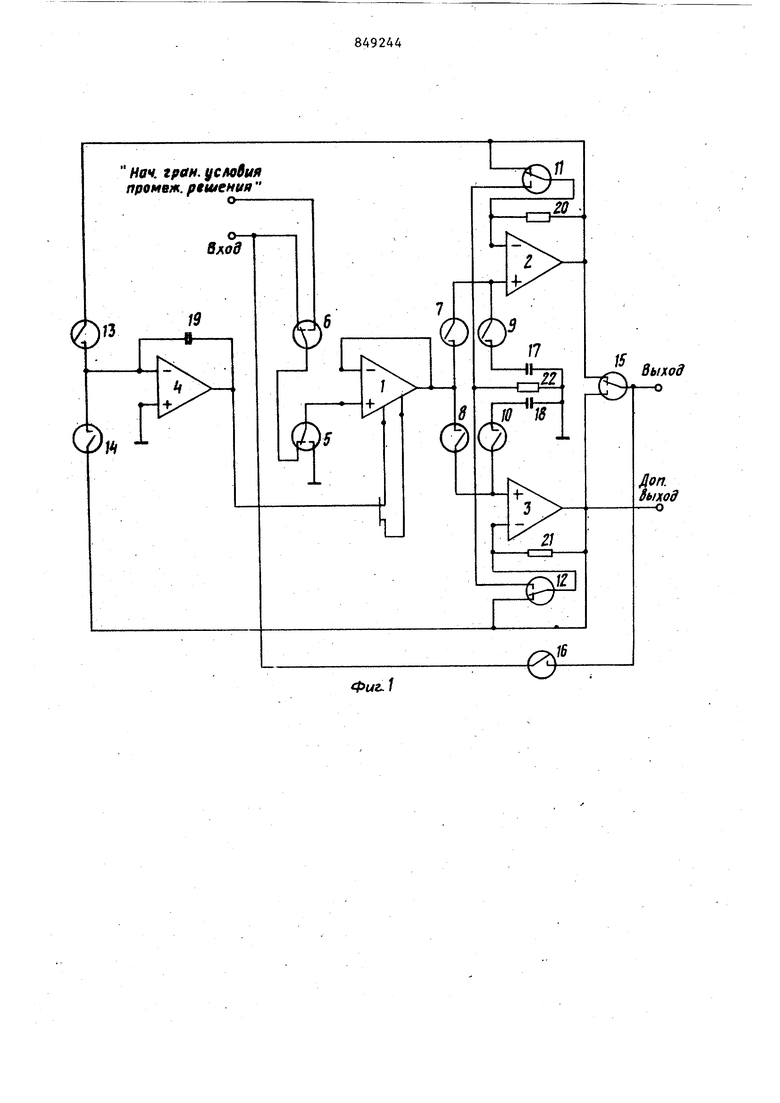

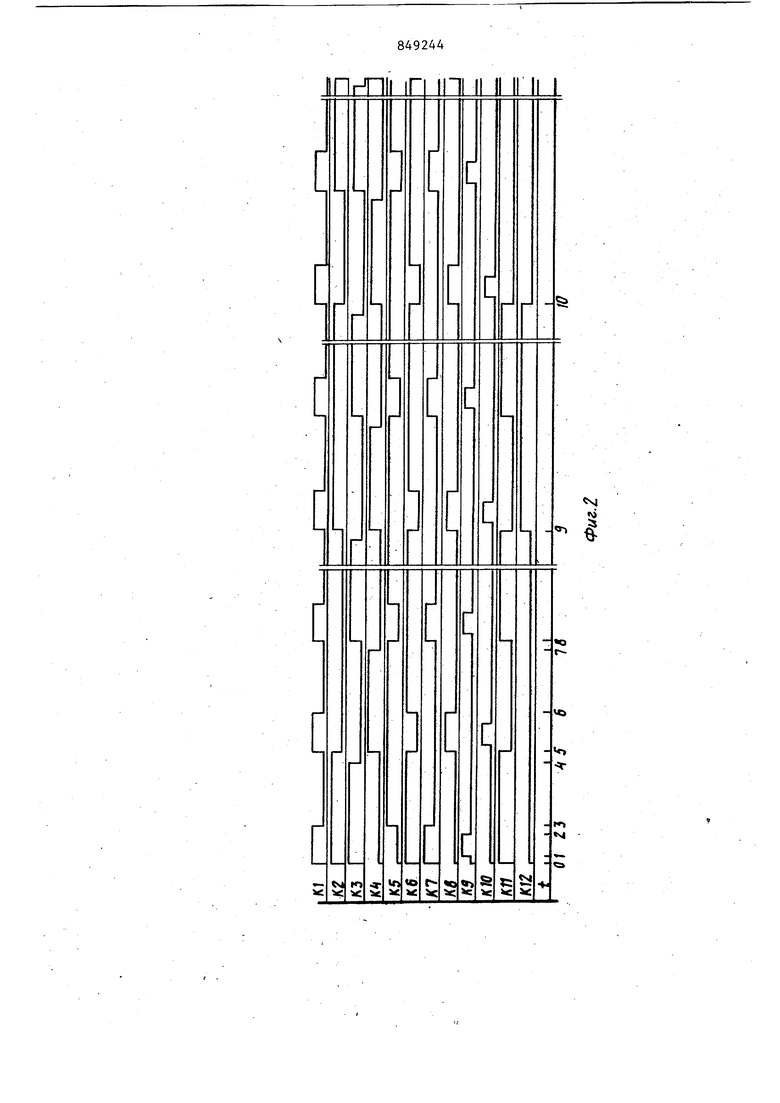

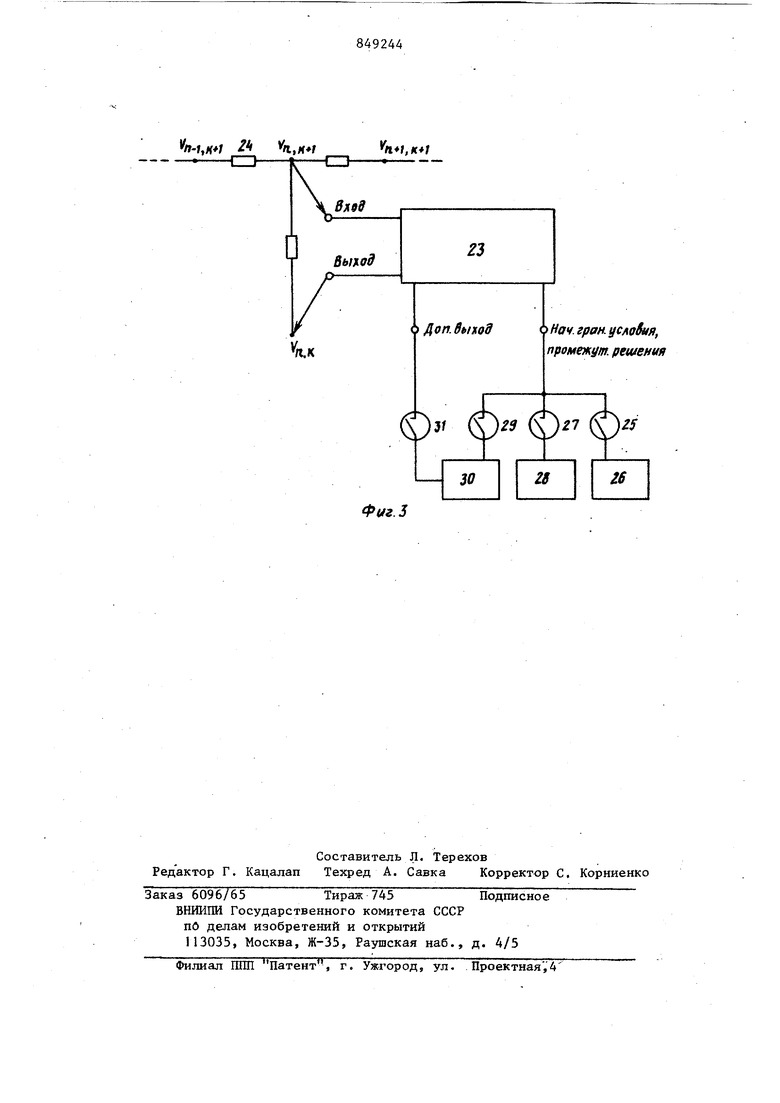

Изобретение относится к аналоговым вычислительным устройствам, пред назначенным для решения дифференциал ных уравнений с использованием ре- зистивных сеток. Известен резистивно-емкостной решающий элемент, содержащий резистор, конденсатор, плоскую проводящую сред и источник питания р. Однако данное устройство не обеспечивает высокую точность решения дифференциальных уравнений. Наиболее близким к изобретению по технической сущности является уст ройство для аналогового моделирования задачи теплопроводности, решающи узел которого содержит операционный усилитель, два конденсатора, резистор и три ключа 2. Недостаток известного узла заключается в том, что отсутствует входной операционный усилитель. Включение входной клеммы узла в резистивную сетку без входного операционного усилителя вызывает искажение аналогового сигнала, что приводит к возрастанию погрешности, а также увеличивает время записи напряжения из ре- . зисторной сетки в конденсаторы памяти. В схеме решающего узла предусмотрена статическая коррекция погрешности, в то время как смещение и температурный дрейф нуля операционного усилителя имеют характер постоянно изменяющейся во времени величины. Коррекция статического типа позволяет избавиться от погрешности лишь частично и требует периодической ручной настройки. Каждый из двух конденсаторов памяти после записи величины напряжения вначале отключается от входной клеммы узла, а затем подключается к входу операционного усилителя. В результате импульсных помех, возникающих при коммутации, появляется дополнительный источник помех, искажающих величину напряжения, Написанного на обкладках конденсатора. Включение сумматора для иммита ции постоянного источника тепла в каждый решающий узел не является не обходимостью. Кроме того, узел предназначен для решения только одномерных задач не позволяет осуществить аналоговые вычисления для двух- и трехмерных моделей. Цель изобретения - повышение точности вычислений. Поставленная цель достигается тем что в узел, содержащий первый операционный усилитель, первый и второй запоминаюище конденсаторы, корректирующий резистор, первый, второй и тр тий ключи, дополнительно введены клю чи, два операционных усилителя, управляемый резистор, интегратор и масштабирующие резисторы, причем неинвертирующий вход первого операцион ного усилителя соединен с переключающим контактом первого ключа, замы кающий контакт которого соединен с шиной нулевого потенциала, размыкаюш й контакт первого ключа подключен к переключающему контакту второго ключа,, размыкающий контакт которого соединен с входом узла, размыкающий контакт- второго ключа подключен к входу промежуточных решений, выход первого операционного усилителя соединен с инвертирующим входом первого операционного усилителя и через замы кающие контакты третьего и четвертог ключей соответственно с неинвертир.ую щими входами второго и третьего операционных усилителей, неинвертируюши вход второго операционного усилителя через замыкаюший .контакт пятого клю ча подключен к первой обкладке первого запоминающего конденсатора, вторая обкладка которого соединена с шиной нулевого потенциала, неинверти рующий вход четвертого операционного усилителя через замыкающий контакт шестого ключа подключен к первой обкладке второго запоминающего кон денсатора, вторая обкладка которого соединена с шиной нулевого потенциала, инвертирующий вход второго oneрационного урилителя подключен к пер ключающему контакту седьмого ключа, мыкающий контакт которого соединен с замыкающим контактом восьмого ключа и первым выводом резистора, второй вывод которого подключен к шине нулевого потенциала, инвертирующий ВХОД третьего операционного усилителя соединен с переключающим контактом восьмого ключа, размыкающий контакт которого подключен к выходу третьего операционного усилителя, замыкающему контакту девятого ключа, и через замыкающий контакт десятого ключа подключен к входу интегратора, вход которого через замыкающий контакт одиннадцатого ключа подключен к размыкающему контакту седьмого ключа. Выходу второго операционного усилителя и размыкающему контакту девятого Ключа, переключаюш {й контакт которого соединен с выходом узла и через замыкающий контакт двенадцатого ключа соединен с входом узла, входной и выходной вывод управляемого резистора включены в цепь коррекции погрешностей смещения нуля первого операционного усилителя, управляемый электрод управляемого резистора подключен , к выходу интегратора, дополнительный выход узла соединен с выходом третьего операционного усилителя,выходы второго и третьего операционных усилителей через соответствующие масштабирующие резисторы соединены с инвертирующими входами второго и третьего операционных усилителей соответственно. На фиг, 1 изображена схема аналогового решающего узла; на фиг. 2 эпюры I импульсных напряжений управления процессами решения, коррекции погрешности и изменения режимов;на фиг. 3 - схема подключения решающего узла в резистивную сетку и к внешним устройствам. Решающий узел содержиу первый 1, второй 2 и третий 3 операционные усилители, интегратор 4, ключи 5-16, конденсаторы 1 7 - 19,-масштабирующие резисторы 20 и 21, резистор 22 .и управляемый резистор 23. На эпюрах,приведенных для ключей 5-16, положение с низким уровнем соответствует нормальной коммутаofiH подвижных контактов ключей, а с высоким -противоположной,На шкале t Обозначены, характерные моменты времени в процессе управления решающим узлом. Решающий узел 23 подключен своей клеммой Вход в резистивную сетку 24 в точке с напряжением U .а клем- 1Гт IIП,К( мои Выход - к точке с напряжением где п - порядковый номер по пространственной координате сетки, порядковый номер по временным слоям искомого решения,Uf..........и,- значени i:lA. IT IlK+l напряжения в соседних пространственн .точках сетки. Клемма Промежуточные решения подкотючена через ключ 25 к источнику 26 напряжения начального условия через ключ 27 - к источнику 28 напр жения граничного условия, через ключ 29 - к выходу ОЗУ 30. Клемма Допол нительный выход через ключ 3 Г подключена к входу ОЗУ 30. Работа решающего узла начинается с момента времени Ьо в режиме ввода начальных условий. Высокий уровень подается на ключи 5,6,7,10,11 и 15. В результате, входной операционный усилитель 1 с заземленным входом сое диняется в последовательную цепь с выходным операционным усилителем 2, который переводится в режим усилителя с коэффициентом усиления к Е и его выход отключается от клеимы Выход. В момент времени Ъ высокий урове подается на ключ 13. При этом последовательная цепь из операционных усилителей 1 и 2 замыкается в кольцо обратной связи через интегратор 4 и резистор 23. В течение времени Ьд --tcj . происходит коррекция погре ности пары операционного усилителя 2 В момент времени-Ьз,на ключ 13 подается низкий .уровень и кольцо обра ной связи разрывается. Напряжение ко рекции сохраняется на последующее время на конденсаторе 19. В момент времени -ь„ низкий уровень подается на ключи высокий на ключ 9. операционный усилитель 2 возвращается в режим с единичным коэффициентом усиления и к его входу подключается конденсатор I7. Вход операционног усилителя I подключается к клемме Промежуточные решения., на которую подано через ключ 25 напряжение начального условия с источника 26. В течение времени Ь„--Ь|, происходи запись величины напряжения начальног условия в конденсатор 17. В момент времени Ъ низкий уров подается на ключ 7, при этом разрывается связь между операционными уси лителями 1 и 2. В момент времени -tg высокий уровень подается на ключи 5,8 и 12, а низкий уровень подается на ключи 6,10 и 15. При зтом происходит объеди нение в Пару входного усилителя и выходного усилителя 3, а выход операционного усилителя 2 соединяется с клеммой Выход. Напряжение начального условия начинает транслироваться вточку Ц (при )резистивной сетки 24. Далеепроисходит коррекция пары операционных усилителей 1 и 3 с помощью интегратора 4 идентично с предыдущей парой. Начиная с i/, доЬ7 происходит запись на конденсатор 18 напряжения U (прии+1 1) с клем.. .1 П. мы Вход. Момент времени tg идентичен моменту времени t за исключением наличия низкого уровня н ключ 6, что влечет запись на конденсатор 17 с клеммы Вход очередного решения Up . (при ), полученного по транслируемому в сетку 24 напряжению с выхода операционного усилителя 3. Повторение в необходимом количестве этого цикла позволяет получить все к решений для данной пространственной координаты п. В момент времени to .возникает необходимость точку с пространственной координатой п сделать граничной. С этой целью подается высокийуровень на ключи 6 и 16, при этом на вход операционного усилителя 1 под ключается клемма Промежуточные решения, на котор ую подается через ключ 29 напряжение граничного условия из источника 28, а клемма Выход соединяется с клеммой Вход. В остальном схема продолжает функционировать как в рёяйме нахождениярешений. В результате, в период времени ,пока точка с Координатой п резистивной сетки 24 является граничной, туда из решающего узла постоянно транслируется напряжение, равное по величине напряжению на источнике В момент времени 1ц возникает необходимость произвести переход в ежим поиска решений по методу расепления. С этой целью на ключ 16 одается низкий уровень, на ключ 6 ериодически подается высокий или низкий уровень, причем высокий уроень на ключе 6 присутс,твует одновреенно с высоким уровнем на ключе 7. низкому оследнее относится к При этом на ровню на этих ключах. 8492 ОЗУ аналоговая информация подается только на конденсатор 17 усилителя 2 и постоянно транслируется на клемму Выход. Полученное на резистивной сетке 24 напряжение нового решения поступает на клемму Выход, откуда оно подается только на конденсатор 18 усилителя 3 и постоянно транслируется на клемму Дополнительный выход. С этой клеммы через ключ,решения вновь заносится в ОЗУ. Благодаря высокоомному входу решающий узел имеет практически полную гальваническую развязку с резистивной сеткой и не вносит искажений в формирование сеткой аналоговой величины. Наличие входного усилителя позволяет широко варьировать номинальные величины составляющих сетку резистороб, при этом время записи результата 20 ных

вычислений из сетки в решающий узел остается неизменным или может быть независимо изменено.

После записи результата на конденсатор памяти происходит только одно отключение конденсатора от выхода входного операционного усилителя-.Подключение конденсатора к входу выходного усилителя осуществляется в решающем узле заблаговременно. Сведение к минимуму коммутационных переключений, искажающих аналоговую величину, приводит к дополнительному повьш1ению точности.

В схеме решающего узла усилители искажают аналоговую величину сигнала за счет наличия у них смещения ну и дрейфа его величины во времени. Дпя-организации коррекции используется особенность работы двух выходных операционных усилителей, по-очередная запись напряжения в их конденсаторы памяти из сетки и поочередная (в противоположной фазе) трансляция ими этого напряжения на резистивную сетку. Например, если второй выходной усилитель транслирует напряжение в сетку, вход третьего соединяется с выходом первого входного усилителя. Цепь из первого и третьего усилителей замыкается на время коррекции в кольцо отрицательно обратной связи интегратором. Сигнал напряжения с выхода интегратора постоянно подается на управляемый резис тор, который вЛлючен в цепь коррекции нуля входного операционного усилителя Так как в это время первый усилитель 5 10 15

цию. Коммутацией ключей схема переводится в режим задания граничных условий. В результате на входе в. нуж11ЫЙ момент времени можно задавать напряжение, соответствующее по величине граничному условию. Возможностью такой коммутации обладает каждый решающий узел резистивной сетки, что позволяет автоматически изменить масштаб в процессе аналогового вычисления..

Изобретение позволяет при минимуме дополнительных аппаратурных затрат достигнуть значительного увеличения точности.

Формула изобретения

Аналоговый решающий узел, содepжaш й первый операционный усилите первый и второй запоминающие конденсаторы, резистор, первый, второй и третий ключи, отличающийс

тем, что, с целью повышения точности, в него дополнительно введены ключи,два операционных усилителя, управляемый резистор, интегратор и масштабирующие резисторы, причем неинвертирующий вход первого операционного усилителя соединен с переключающим контактом первого ключа, змыкающий контакт которого соединен с шиной нулевого потенциала, размыкающий контакт первого ключа подключен к переключающему контакту второго ключа замыкающий контакт которого, соединен с входом узла, размыкающий контакт которого соединен с входом 4о заземляется по входу, а третий переводится в режим усилителя с , происходит автоматическая отстройка суммарного смещения нуля у этой пары усилителей. Выработанное напряжение коррекции нуля запоминается в интеграторе и после разрыва цепи обратной связи. Через откорректированную пару происходит вначале запись напряжения из резистивной сетки на конденсатор, а затем после отключения .входного БУ трансляция этого напряжения в сетку. При этом входной операционный усилитель образует новую корректируемую пару с вторым выходным усилителем и все процессы в новой паре аналогично повторяются. В решающем узле выход промежуточрешений несет совмещенную функузла, размыкающий конта кт второго ключа подключен к выходу-промежуточных решений, выход первого операционного усилителя соединен с инвертирующим входом первого операционного усилителя и через замыкающие контакты третьего и четвертого ключей соответственно с неинвертирующими входами второго и третьего операционных усилителей, неинвертирующи вход второго операционного усилителя через замыкающий контакт пятого ключ подключен к первой обкладке первого запоминающего конденсатора, вторая обкладка которого соединена с шиной нулевого потенциала, неинвертирующий вход четвертого операционного усилителя через замыкающий контакт шестого ключа подключен к первой обкладке второго запоминающего конденсатора, вторая обкладка которого соединена с шиной нулевого потенциала, инвертирующий вход второго операционного усилителя подключен к переключающему контакту седьмого ключа, замыкающий контакт которого соединен с замыкающим контактом восьмого ключа и первым выводом резистора, второй вывод которого подключен к шине нулевого потенциала, инвертирующий вход третьего операционного усилителя соединен с переключающим контактом восьмого ключа, размыкающий контакт которого подключен к выходу третьего операционного усилителя, замыкающему контакту девятого ключа, и через замыкающий контакт десятого ключа подключен к входу интегратора, вход которого через замыкающий контакт одиннадцатого ключа подключен к размыкающему контакту седьмо ключа, выходу второго операционного усилителя и размыкающему контакту девятого ключа, переключающий контакт которого соединен с выходом узла и через замыкающий контакт двенадцатого ключа соединен с входом узла, входной и выходной вывод управляемого резистора включены в цепь коррекции погрешностей смещения нуля первого операционного усилителя, управляемый вывод управляемого резистора подключен к выходу интегратора, дополтельный выход узла соединен с выходом третьего операционного усилителя, выходы второго и третьего операционных усилителей через соответствующие масштабирующие резисторы соединены с инвертирующими входами второго и третьего операционных усилителей соответственно.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 444212, кл. G 06 G 7/40, 1978.

2.Аналоговое моделирование задач теплопроводности с помощью электрической резистивной цепи и аналоговой памяти, -Mem.Fde Eng.Kuoto Univ, 1977 39, № n-15 (прототип).

Нач. гран, у слабая промвгк. ptufCHua о

И

Ь

ZO

Вмд

/5

ё

о

41D«r

/7

я ; - Выход

Эг

гг

4Ь

Q IS

оымд-о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Интегратор | 1984 |

|

SU1161963A1 |

| Устройство для моделирования электромагнитных процессов в асинхронных машинах | 1989 |

|

SU1681315A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Интегратор с автоматической кор-РЕКциЕй НулЕВОгО уРОВНя | 1978 |

|

SU811285A1 |

| УСТРОЙСТВО ДЛЯ КЛАССИФИКАЦИИ МНОГОПАРАМЕТРИЧЕСКИХ ОБЪЕКТОВ | 1991 |

|

RU2049355C1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ СИГНАЛОВ РЕЗИСТИВНЫХ ДАТЧИКОВ ВО ВРЕМЕННОЙ ИНТЕРВАЛ | 1994 |

|

RU2097777C1 |

| Интегратор с автоматической коррекцией нулевого уровня | 1982 |

|

SU1108471A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1420537A1 |

/f

а

.

tsi

ч

0

ч«ч

2l Я.,

CD--ftCZ

О

Bbijiod

Чк

23

9 Hot. гран, условия,

о Доп. вняод промежут. решения

)з

Z9 ( )г7 ( )/5

Фиг. 5

Авторы

Даты

1981-07-23—Публикация

1979-07-23—Подача