Изобретение относится к электронике и радиотехнике и может быть использовано в различных устройствах автоматики и измерительной техники. Известны интеграторы, построенные на основе усилителей с автоматической коррекцией нулевого уровня и состоящие из основного операционного усилителя (ОУ), охваченного емкостной обратной связью, дополнительног усилителя, вход которого подсоедине к выходу основного ОУ, запоминающего конденсатора и ключа, подключенного к неинвертирующему входу основ кого ОУ. К инвертирующему входу основного ОУ подключены источник вход ного тока, интегрирующий конденсатор |И входной ключ, второй вывод которо то Подключен к общей (нулевой) шине интегратора .1П. Известные интеграторы подобного типа позволяют повысить точность интегрирования входного воздействия за счет компенсации напряжения смещения (и его дрейфа) основного ОУ, однако напряжение смещения компенсируется неполностью, что обусловлено запоминанием напряжения смещения и на интегрирующем конденсаторе Кроме того, на интегрирующем конденсаторе запоминается напряжение смещения дополнительного усилителя., что также снижает точность интегрирования . Наиболее близким по технической сущности к предлагаемому является и тегратор с автоматической коррекцией нулевого уровня, содержащий первый и второй операционные усилители интегрирующий конденсатор, первый и второй запоминающие конденсаторы, причем инвертирующий вход первого ОУ подключен к источнику входного тока, через первый замыкающий ключ соединен с шиной нулевого потенциала и через интегрирующий конденсато с выходом этого ОУ, выход второго ОУ через второй замыкающий ключ подключен к неинвертирующему входу первого ОУ, соединенному через первьй запоминаю1ций конденсатор с шиной нулевого потенциала, инвертирующий вход вя-орого ОУ через первый размыкающий ключ соединен с его выходом и через второй запоминающий конденсатор подключен к общему выво ду последовательно соединенных .третьего замыкающего и второго раз12мыкающего ключей, включенных между выходом первого ОУ и шиной нулевого потенциала, выход первого ОУ является выходом устройства t2K. Недостатком данного интегратораj является наличие динамической погрещности, возникающей в результате разрыва петли отрицательной обратной связи по постоянному току в режиме запоминания напряжения компенсации, что приводит к снижению точности интегрирования.. . Цель.изобретения - повыщение точности интегрирования. Поставленная цель достигается тем что в интегратор с автоматической коррекцией нулевого уровня, содержащий первый дифференциальный операционный усилитель, инвертирующий вход которого подключен к источнику входного тока, через первый замыкающий ключ соединен с шиной нулевого потенциала и через интегрирующий конденсатор - с выходом первого дифференциального операционного усилителя, являющегося выходом интегратора, неинвертирующий вход первого дифференциального операционного усилителя через первый запоминающий конденсатор соединен с шиной нулевого потенциала и через втррой замыкающий ключ подключен к второго дифференциального операционного усилителя, соединенного через первый размыкающий ключ с его инвертирующим входом , третий замыкающий ключ, один вывод которого подключен к выходу первого дифференциального операционного усилителя, второй запоминающий конденсатор и второй размыкающий ключ, один вывод которого соединен с первой обкладкой второго запоминакщего конденсатора, введены третий размыкающий ключ и четвертый замыкающий ключ, причем второй вывод второго размыкающего ключа соединен, с вторым выводом третьего замыкающего ключа и с инвертирующим входом второго дифференциального операционного усилителя, неинвертирующий вход которого подключен к второй обкладке второго запоминающего конденсатора и через . третий размыкающий ключ к шине нулевого потенциала, а между шиной нулевого потенциала и первой обкладкой второго запоминающего конденсатора включен четвертый замыкающий клю.

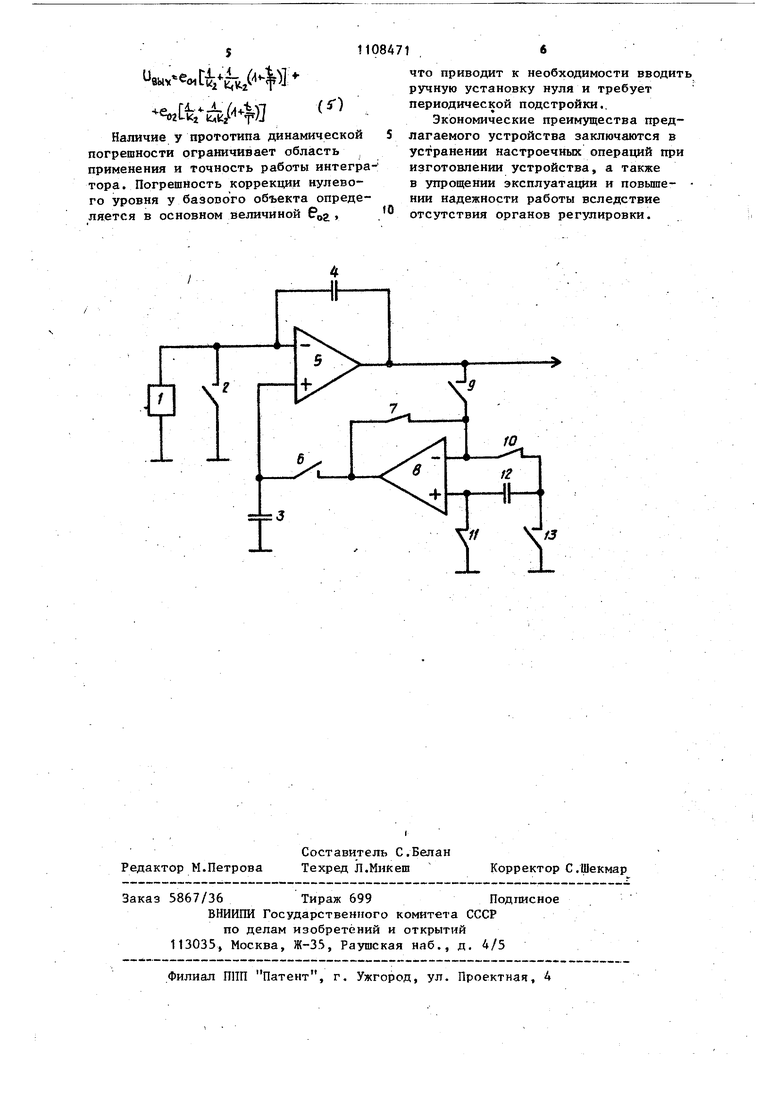

На чертеже представлена функциональная схема предлагаемого интегратора.

Интегратор содержит источник 1 входного тока, первый замыкающий ключ 2, первый запоминающий конденсатор 3, интегрирующий конденсатор 4, первый дифференциальный операционный усилитель ОУ 5, второй замыкающий ключ 6, первый размыкающий ключ 7, второй дифференциальный операционный усилитель ОУ 8, третий замыкающий ключ 9, второй и третий размыкакнцие ключи 10 и 11, второй запоминающий конденсатор 12 и четвертый замыкающий ключ 13. Между инвертирующим входом ОУ 5 и шиной нулевого потенциала включены источники 1 входного тока и ключ 2, а I между неинвертирующим входом ОУ 5 и шиной нулевого потенциала - первый запоминающий конденсатор 3, интегрирующий конденсатор 4 включен между выходом ОУ 5 и его инвертирующим входомJ кЛюч 6 включен между выходом ОУ 8 и неинвертирующим входом ОУ 5, ключ 7 включен между выходом ОУ 5 и его инвертирующим входом, инвертирующий вход ОУ 5 через ключ.9 соединен с выходом ОУ 5, а через ключ 10 - с первой обкладкой второго запоминающего конденсатора 12 вторая обкладка конденсатора 12 соединена с неинвертирующим входом ОУ 8 первая и вторая обкладки конденсатора 12 через ключи 13 и :11 соответственно соединены с шиной нулевого потенциала, выход ОУ 5 является выходом устройства. В качестве ОУ 5 и 8 могут быть использованы ОУ широкого применения с малой величиной входного тока и большим значением коэффициента подавления синфазного сигнала. Таким требованиям удовлетворяет ОУ типа 140УД8А. В качестве ключей 2, 6, 7, 9, 10, 11 и 13 могут быть использованы две микросхемы К590КН5, каждая из которых содержит четыре независимых КМОП ключа. Конденсаторы 3, 4 и 12 должны иметь минимальный ток утечки и малую постоянную времени поляризации. Конденсатор 4 должен быть с малым ТКЕ.

Интегратор работает в двух режимах: режиме запоминания компенсирующего напряжения и в режиме интегрирования .

В режиме запоминания компенсирующего напряжения ключ 2 закорачивает инвертирующий вход ОУ 5 и тем самым обеспечивает обнуление конденсатора 4 и отключение источника 1 входного тока. Замкнутый в этом режиме ключ 6 обеспечивает подключение выхода ОУ 8 к конденсатору 3, а замкнутый ключ 9 - подключение выхода ОУ 5 к инвертирующему входу ОУ 8. Ключи 7, 10 и 1Г в этом режиме разомкнуты. В результате на конденсаторе 3 устанавливается компенсирующее напряжение (и), равное

5

П -Kl, fl) °4 KtJir

где Gf, , eoi напряжение смещения нуля ОУ 5 и В соответст0венно,

К, К - коэффициент передачи ОУ 5 и 8 соответственно,

Vtil иапряженке на конден5саторе 12.

На интегрирующем конденсаторе4 устанавливается напряжение (Vc) равное

30

-. (2)

и

йЧ

в режиме интегрирования ключи 2, 6, 9 и 13 разомкнуты, а ключи 7, 10 и 11 замкнуты. В этом режиме (помимо интегрирования входного воздействия)- осуществляется запоминание напряжения смещения нуля BQ ОУ 8 на конденсаторе 12.

(3)

Uc,7

.i

При отсутствии входного воздействия выходное напряжение интегратора UebtxB режиме интегрирования определяется следующим выражением:

bifcbiv -еа,(1 -f ). и,, ()

50

где Т - RC (R - выходное сопротивление источника 1 входного тока, С - величина емкости интегрирующего конденсатора) t - время интегрирования.

Пр,н условии, Что К-( 1 и Kji 1 иэ (1), (2), (3) и (4) имеем 51108 0 avd-K/ iJ Наличие у прототипа динамической погрешности ограничивает область применения и точность работы интегра- тора. Погрешность коррекции нулевого уровня у базового объекта определяется в основном величиной вог . что приводит к необходимости вводить ручную установку нуля и требует периодической подстройки.. Экономические преимущества предлагаемого устройства заключаются в устранении настроечных операций при изготовлении устройства, а также в упрощении эксплуатации и повьше- НИИ надежности работы вследствие отсутствия органов регулировки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор с автоматической коррекцией нулевого уровня | 1983 |

|

SU1104539A1 |

| Интегратор с автоматической кор-РЕКциЕй НулЕВОгО уРОВНя | 1978 |

|

SU811285A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Устройство для извлечения корня | 1978 |

|

SU811292A1 |

| Интегратор | 1980 |

|

SU920756A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841056A1 |

| Интегрирующее устройство | 1983 |

|

SU1105903A1 |

| Устройство для интегрирования сигнала | 1988 |

|

SU1571623A1 |

ИНТЕГРАТОР С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ НУЛЕВОГО УРОВНЯ, содержащий первый дифференциальный операционный усилитель, инвертирующий вход которого подключен к источнику входного тока, через первый замыкающий ключ соединен с шиной нулевого потенциала и через интегрирующий конденсатор - с выходом первого дифференциального операционного усилителя , .являющегося выходом интегратора, неинвертирующий вход первого дифференциального операционного усилителя через первый запоминаюи 1й конденсатор соединен с шиной нулевого потенциала и через второй замыкающий ключ подключен к выходу второго дифференциального операционного усилителя, соединенного-через первый размыкающий ключ с его инвертирующим входом, третий замыкающий ключ, один вывод которого подключен к выходу первого дифференциального операционного усилителя, второй запог-шиающий конденсатор и второй размыкающий ключ, один вывод которого соединен с первой обкладкой второго запоминающего конденсатора, о т личающийся тем, что, с целью повышения точности интегрироваi ния, в него введень третий размыкающий ключ и четвертый замыкакиций (Л ключ, причем второй вьтод второго размыкающего ключа соединен с вторым выводом третьего замыкающего С ключа и с инвертирующим входом втоs рого дифференциального операционного усилителя,неинвертирующий вход которого подключен к второй обкладке второго запоминающего конденсатора и через третий размыкающий ключ к шине нулевого потенциала, а между иагной нулевого потенциала СХ 4 и первой Обкладкой второго запоминающего конденсатора включен четвер тый замьжающий ключ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3667055, кл 330-9, опублик | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Интегратор с автоматической кор-РЕКциЕй НулЕВОгО уРОВНя | 1978 |

|

SU811285A1 |

Авторы

Даты

1984-08-15—Публикация

1982-11-09—Подача