I

Изобретение относится к автоматике и вы 1ислительной технике и может найти применение в высоконадежных цифровых синхронизируюпщх устройствах.

По основному авт. св. № 645282 известен резервированный делитель частоты, содержащий три канала, каждый из которых состоит из счетчика импульсов на ЗК-триггерах (счетчика) , счетный вход первого из которых соединен с входной шиной мажоритарного элемента, входы которого соединены с выходами счетчиков каждого канала и логического элемента эквивалентности, входы Которого соединены с выходами счетчика и мажоритарного элемента данного канала, а выход подключен к О и К входам первого ЛК-триггера счетчика каждого канала СП

Недостатком известного устройства является низкая надежность, обусловленная потерей работоспособности канала делителя на время цикла пересчета, следующего за циклом, в котором произошел сбой, приводящий к отставанию одного из каналов.

Цель изобретения - повышение надежности деления.

Поставленная цель достигается тем, что в резервированный делитель частоты, содержаний три канала, каждый из которых состоит из счетчика импульсов,

10 мажоритарного элемента и логического элемента эквивалентности, каждый канал дополнительно содержит синхронный дву ступенчатый О-триггер, дополнительный мажоритарный элемент, дополнитель15ный элемент логической эквивалентности и элемент ШШ-НЕ, причем входы Ь и С синхронного двухступенчатого р-триггера соединены соответственно с выходом и входом счетчика данного

20 канала, выход синхронного двухступенчатого: О-Триггера соединен со входом дополнительного мажоритарного элемента, другие входы которого соединены

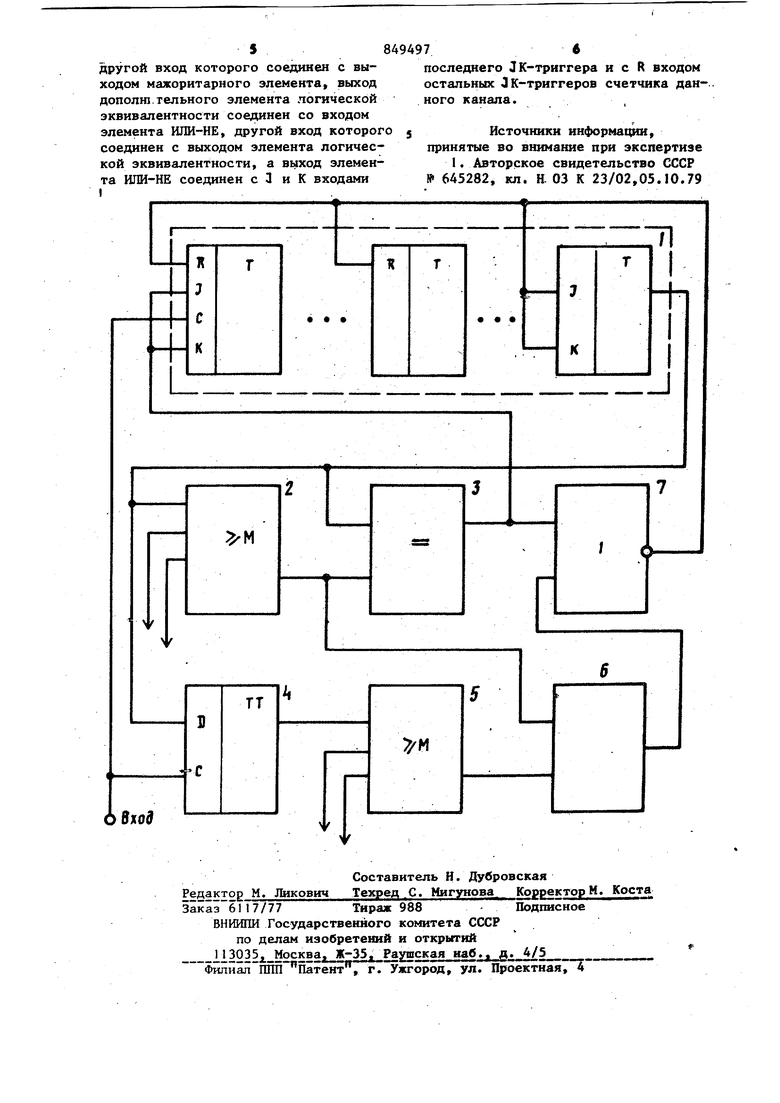

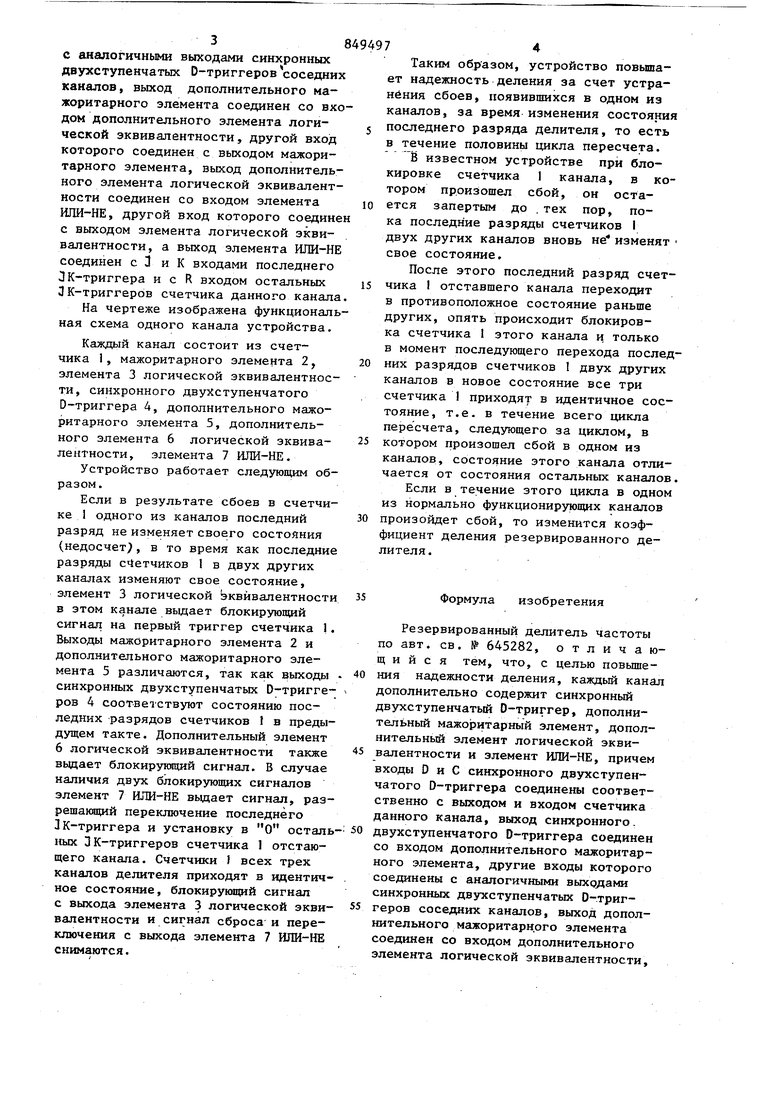

с аналогичными выxoдa ш синхронных двухступенчатых D-триггеров соседних каналов, выход дополнительного мажоритарного элемента соединен со входом дополнительного элемента логической эквивалентности, другой вход которого соединен с вькодом мажоритарного элемента, выход дополнительного элемента логической эквивалентности соединен со входом элемента ИЛИ-НЕ, другой вход которого соедине с выходом элемента логической эквивалентности, а выход элемента ШШ-НЕ соединен с 3 и К входами последнего ЛК-триггера и с R входом остальных ЗК-триггеров счетчика данного канала На чертеже изображена функциональная схема одного канала устройства.

Каждый канал состоит из счетчика 1, мажоритарного элемента 2, элемента 3 логической эквивалентности, синхронного двухступенчатого D-триггера 4, дополнительного мажоритарного элемента 5, дополнительного элемента 6 логической эквивалентности, элемента 7 ИЛИ-НЕ.

Устройство работает следуюпщм образом.

Если в результате сбоев в счетчике 1 одного из каналов последний разряд не изменяет своего состояния (недосчет, в то время как последние разряды с1етчиков 1 в двух других каналах изменяют свое состояние, элемент 3 логической Эквивалентности в этом канале выдает блокируюпщй сигнал на первый триггер счетчика 1. Выходы мажоритарного элемента 2 и дополнительного мажоритарного элемента 5 различаются, так как щькоцы синхронных двухступенчатых D-триггеров 4 соответствуют состоянию последних разрядов счетчиков 1 в предыдущем такте. Дополнительный элемент 6 логической эквивалентности также выдает блокирунлций сигнал. В случае наличия двух блокирующих сигналов элемент 7 ИЛИ-НЕ выдает сигнал, разрешакяций переключение последнего ЗК-триггера и установку в О остальных ЗК-триггеров счетчика 1 отстающего канала. Счетчики i всех трех каналов делителя приходят в идентичное состояние, блокирующий сигнал с выхода элемента 3 логической эквивалентности и сигнал сброса и переключения с выхода элемента 7 ШШ-НЕ снимаются.

Таким образом, устройство повьшает надежность деления за счет устранения сбоев, появившихся в одном из каналов, за время изменения состояния

последнего разряда делителя, то есть в течение половины цикла пересчета. В известном устройстве при блокировке счетчика 1 канала, в котором произошел сбой, он остается запертым до . тех пор, пока последние разряды счетчиков I двух других каналов вновь не изменят свое состояние.

После этого последний разряд счетчика I отставшего канала переходит в противоположное состояние раньше других, опять происходит блокировка счетчика 1 этого канала и только в момент последующего перехода последних разрядов счетчиков 1 двух других каналов в новое состояние все три счетчика 1 приходят в идентичное состояние, т.е. в течение всего цикла пересчета, следующего за циклом, в

котором произошел сбой в одном из

каналов, состояние этого канала отличается от состояния остальных каналов. Если в течение этого цикла в одном из нормально функционирующих каналов

произойдет сбой, то изменится коэффициент деления резервированного делителя.

Формула изобретения

Резервированный делитель частоты по авт. св. № 645282, отличающийся тем, что, с целью повышения надежности деления, каждый канал дополнительно содержит синхронный двухступенчатый 0-триггер, дополнительный мажо ритарный элемент, дополнительньй элемент логической эквивалентности и элемент ИЛИ-НЕ, причем входы D и С синхронного двухступенчатого D-триГгера соединены соответственно с выходом и входом счетчика данного канала, выход синхронного.

двухступенчатого D-триггера соединен со входом дополнительного мажоритарного элемента, другие входы которого соединены с аналогичными выходами синхронных двухступенчатых 0-триггеров соседних каналов, выход дополнительного мажоритарного элемента соединен со входом дополнительного элемента логической эквивалентности.

другой вход которого соединен с выходом мажоритарного элемента выход дополш. тельного элемента логической эквивалентности соединен со входом элемента ИЛИ-НЕ, другой вход которого соединен с выходом элемента логической эквивалентности, а выход элемента ИЛИ-НЕ соединен с 3 и К входами I

последнего ЛК-триггера и с R входом остальных ЛК-триггеров счетчика дан-, ного канала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 645282, кл. Н- 03 К 23/02,05.10.79

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1983 |

|

SU1128389A1 |

| Резервированный делитель частоты импульсов | 1977 |

|

SU698130A2 |

| Резервированный делитель частоты | 1983 |

|

SU1163473A1 |

| Резервированное пересчетноеуСТРОйСТВО | 1978 |

|

SU834923A1 |

| Резервированный делитель частоты | 1983 |

|

SU1109910A1 |

| Трехканальный резервированныйРАСпРЕдЕлиТЕль иМпульСОВ | 1978 |

|

SU798848A1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU953744A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1993 |

|

RU2111609C1 |

| Резервированный делитель частоты | 1985 |

|

SU1265995A1 |

| Резервированный делитель частоты | 1977 |

|

SU645282A1 |

ИiJ:

Авторы

Даты

1981-07-23—Публикация

1979-10-05—Подача