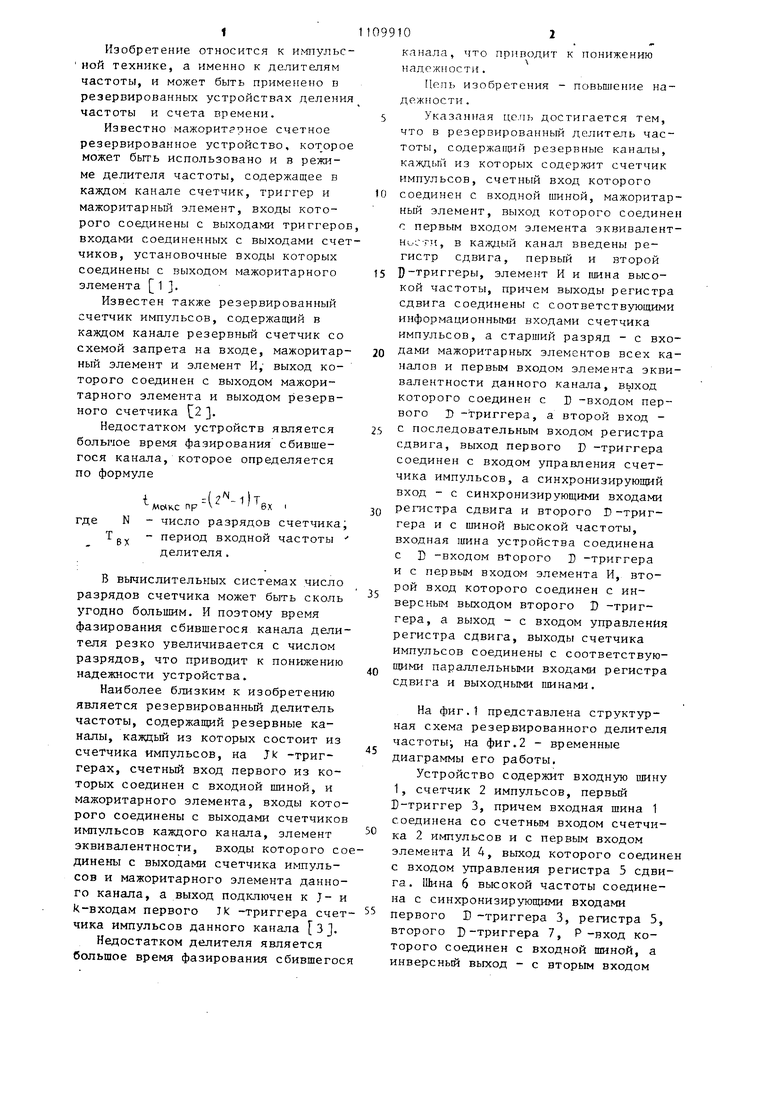

1 Изобретение относится к импульс ной технике, а именно к делителям частоты, и может быть применено в резервированных устройствах делени частоты и счета времени. Известно мажоритарное счетное резервированное устройство, может быть использовано и в режиме делителя частоты, содержащее в каждом канале счетчик, триггер и мажоритарный элемент, входы которого соединены с выходами триггеро входами соединенных с выходами сче чиков, установочные входы которых соединены с выходом мажоритарного элемента Известен также резервированный счетчик импульсов, содержащий в каждом канале резервный счетчик со схемой запрета на входе, мажоритар ный элемент и элемент И, выход которого соединен с выходом мажоритарного элемента и выходом резервного счетчика 2 . Недостатком устройств является большое время фазирования сбившегося канала, которое определяется по формуле ,)Те np-V - бх где N - число разрядов счетчика Tg. - период входной частоты делителя. В вычислительных системах число разрядов счетчика может быть сколь угодно большим. И поэтому время фазирования сбившегося канала дели теля резко увеличивается с числом разрядов, что приводит к понижению надежности устройства. Наиболее близким к изобретению является резервированный делитель частоты, содержащий резервные каналы, каждый из которых состоит из счетчика импульсов, на JX -триггерах, счетный вход первого из которых соединен с входной шиной, и мажоритарного элемента, входы кото рого соединены с выходами счетчико импульсов каждого канала, элемент эквивалентности, входы которого с динены с выходами счетчика импульсов и мажоритарного элемента данно го канала, а выход подключен к Jk-входам первого JX -триггера сче чика импульсов данного канала З Недостатком делителя является большое время фазирования сбившего 02 канала, что приводит к понижению надежности. 1епь изобретения - повьшгение надежности . Указанная цель достигается тем, что в резервированный делитель частоты, содержапц й резервные каналы, кащ;ьш из которых содержит счетчик импульсов, счетный вход которого соединен с входной шиной, мажоритарный элемент, выход которого соединен с nepBbtM входом элемента эквивалентHL,.CTH, в каждый канал введены регистр сдвига, первый и второй D-триггеры, элемент И и шина высокой частоты, причем выходы регистра сдвига соединены с соответствующими информационными входами счетчика импульсов, а старший разряд - с входами мажоритарных элементов всех каналов и первым входом элемента эквивалентности данного капалаf выход которого соединен с Б -входом первого D -триггера, а второй вход с последовательным входом регистра сдвига, выход первого Г -триггера соединен с входом управления счетчика импульсов, а синхронизирующий вход - с синхронизирующими входами регистра сдвига и второго D-триггера и с шиной высокой частоты, входная шина устройства соединена с Г) -входом второго I -триггера и с первым входом элемента И, второй вход которого соединен с инверсным выходом второго D -триггера, а выход - с входом управления регистра сдвига, выходы счетчика импульсов соединены с соответствующими параллельными входами регистра сдвига и выходными шинами, На фиг.1 представлена структурная схема резервированного делителя частоты; на фиг.2 - временные диаграммы его работы. Устройство содержит входную шину 1, счетчик 2 импульсов, первый Б-триггер 3, причем входная шина 1 соединена со счетным входом счетчика 2 импульсов и с первым входом элемента И 4, выход которого соединен с входом управления регистра 5 сдвига. Шина 6 высокой частоты соединена с синхронизирующими входами первого D -триггера 3, регистра 5, второго D-триггера 7, Р -вход которого соединен с входной шиной, а инверсньЕй выход - с вторым входом

элемента И 4. Выходы регистра 5 соедирсены с соответствующими параллельными входами счетчика 2. Кроме того, старший разряд регистра 5 соединен также с входами 8 мажоритарных элементов 9 всех каналов и с первым входом элемента 10 эквива::ентности, второй вход которого соединен с выходом мажоритарного элемента 9 и с последовательным входом регистра 5, а выход - с Г-входом D -триггера 3. Выход D-триггера 3 соединен с входом, управления счетчика 2. Выходы счетчика 2 соединены с соответствующими параллельными входами регистра 5 и с выходными шинами 11 устройства.

Делитель работает следующим образом.

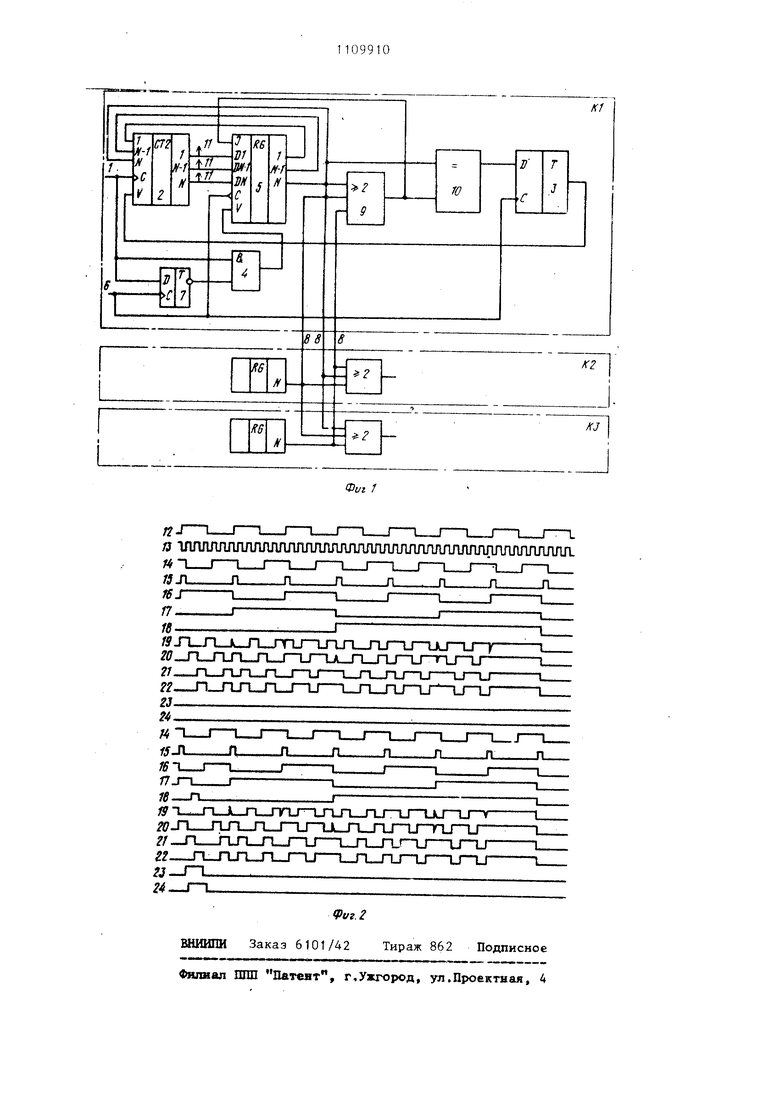

Входной сигнал с входной шины 1 (фиг.2, диаграмма 12) поступает на счетный вход счетчика 2 и содержимое счетчика увеличивается на единицу. Входной сигнал сдвигается синхроимпульсами с шины 6 высокой частоты (диаграмма 13), на D-триггере 7 (диаграмма 14) и на элементе И 4 (диаграмма 15) вырабатывается сигнал,переводящий регистр 5 в параллельный режим работы. Содержимое счетчика 2 (диаграммы 1618) перезаписывается в регистр 5 (диаграммы 19-21). По окончании сигнала с элемента И 4 регистр 5 переходит в последовательный режим работы. Старший разряд регистра 5 (диаграмма 21) поступает на вход 8 мажоритарного элемента 9 (диаграмма 22), и уже скорректированная информация старшего разряда, если произошел сбой, поступает на последовательный вход регистра 5. Одноврменно в случае сбоя на выходе элемента 10 эквивалентности (диаграмма 23) вырабатьгоается импульс положительной полярности, который спуст длительность синхронизирующей частоты через Б -триггер 3 (диаграмма 24) поступает на вход управления счетчика 2 сбившегося канала и переводит его в параллельный режим работы. Содержимое регистра 5 (диаграммы 19-21) перезаписывается в счетчик 2 (диаграммы 16-18) и одновременно начинает происходить коррекци регистра 5 сбившегося канала. Спуст N синхроимпульсов с шины 6 высокой частоты 6 (диаграмма 13), где N число разрядов счетчика и регистра,

происходит полная коррекция регистра в сбившемся.канале. Содержимое регистра перезаписывается в счетчик 2 и поступает на выходные шины 11

(диаграммы 16-18). По окончании коррекции регистра на выходе элемента 10 эквивалентности (диаграм {а 23) вырабатывается сигнал отрицательной полярности, который через D -триггер 3 (диаграмма 24) спустя длительность синхроимпульса переводит счетчик 2 в последовательный режим работы, фиксируя первоначальное состояние счетчиков синхронных каналов.

Таким образом, за N синхроимпульсов происходит полная коррекция сбившегося счетчика.

Максимальное время приведения

сбившегося счетчика к синхронно работаю1цим определяется по формуле

i - NT

чс(кс пр ел где N - число разрядов счетчика;

Tg - период синхроимпульсов. В синхронно работающих каналах на выходе элемента 10 эквивалентности (диаграмма 23) и Г -триггере 3 (диаграмма 24), т.е. на входе управления счетчика 2 присутствует нулевой уровень, т.е. счетчики находятся в последовательном режиме работы. Сравнение информации происходит во время Т - Т, , , где Т- - период входных импульD Л

сов с входной шины 1; т g ci nrдлительность синхроимпульсов с шины 6 высокой частоты.

Время коррекции информации в известном устройстве равно () Tg

где N - число разрядов счетчика; Tg - период входной частоты.

Время коррекции информации в предлагаемом устройстве равно 1 в, сини. Кроме того, в известных устройствах входная информация может меняться как угодно медленно и сбои могут наблюдаться уже в паузах между входными импульсами, а сравнение информации начинается только

после прихода входного импульса. В предлагаемом устройстве сравнение происходит практически постоянно, а именно за время ,. Таким образом, техническая эффективность предлагаемого устройства по сравнению с известным выражается в уменьшении времени фазирования, постоянном сравнении информации, т.е. в повышении надежности

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

| Мажоритарное счетно-резервированное устройство | 1989 |

|

SU1690190A1 |

| Резервированный делитель-формирователь | 1986 |

|

SU1368982A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2022 |

|

RU2785274C1 |

| Мажоритарное резервированное счетное устройство | 1980 |

|

SU938411A1 |

| Многоканальное резервированное счетное устройство | 1983 |

|

SU1099389A1 |

| Мажоритарное счетное резервированное устройство | 1986 |

|

SU1338120A1 |

| Счетное резервированное устройство | 1981 |

|

SU978356A1 |

| Резервированный делитель частоты | 1985 |

|

SU1265995A1 |

| Резервированный счетчик импульсов | 1986 |

|

SU1370778A1 |

РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ, содержащий резервные каналы, каждый из которых содержит счетчик импульсов, счетный вход которого соединен с входной шиной, мажоритарный элемент, выход которого соединен с первым входом элемента эквивалентности, отличающийся тем, что, с целью повышения надежности, в каждый канал введены регистр сдвига, первый и второй D -триггеры, элемент И и шина высокой частоты,причем выходы регистра сдвига соединены с соответствующими информационными входами счетчика импульсов, а старший разряд - с входами мажоритарных элементов всех каналов и первым входом элемента эквивалентности данного канала, выход которого соединен с D-ВХОДОМ первого D -триггера, а второй ВХОД - с последовательным входом регистра сдвига, выход первого D-триггера соединен с входом управления счетчика импульсов, а синхронизирующий вход - с синхронизирующими входами регистра сдвига, второго D-триггера и с шиной высокой частоты, входная шина устройства соединена с D -входом второго D -триггера и с первьм входом элемента И, второй вход которого соединен с инверсным выходом второго D -триггера, а выход - с входом управления регистра сдвига, при этом выходы счетчика импульсов соединены с соответствующиСО ми параллельными входами регистра сдвига и выходными шинами.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Лосев В.В., Яковлев Д.О | |||

| Исправление сбоев пересчетных схем | |||

| - Автоматика и телемеханика, 1971, № 5 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-23—Публикация

1983-03-21—Подача