(54) УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| УСТРОЙСТВО АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2259638C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2197788C2 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| СПОСОБ УСТОЙЧИВОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ ПРИ ПРИМЕНЕНИИ ЖЕСТКИХ И МЯГКИХ РЕШЕНИЙ И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2023 |

|

RU2812964C1 |

| Способ кодовой цикловой синхронизации для каскадного кода при применении жестких решений | 2016 |

|

RU2633148C2 |

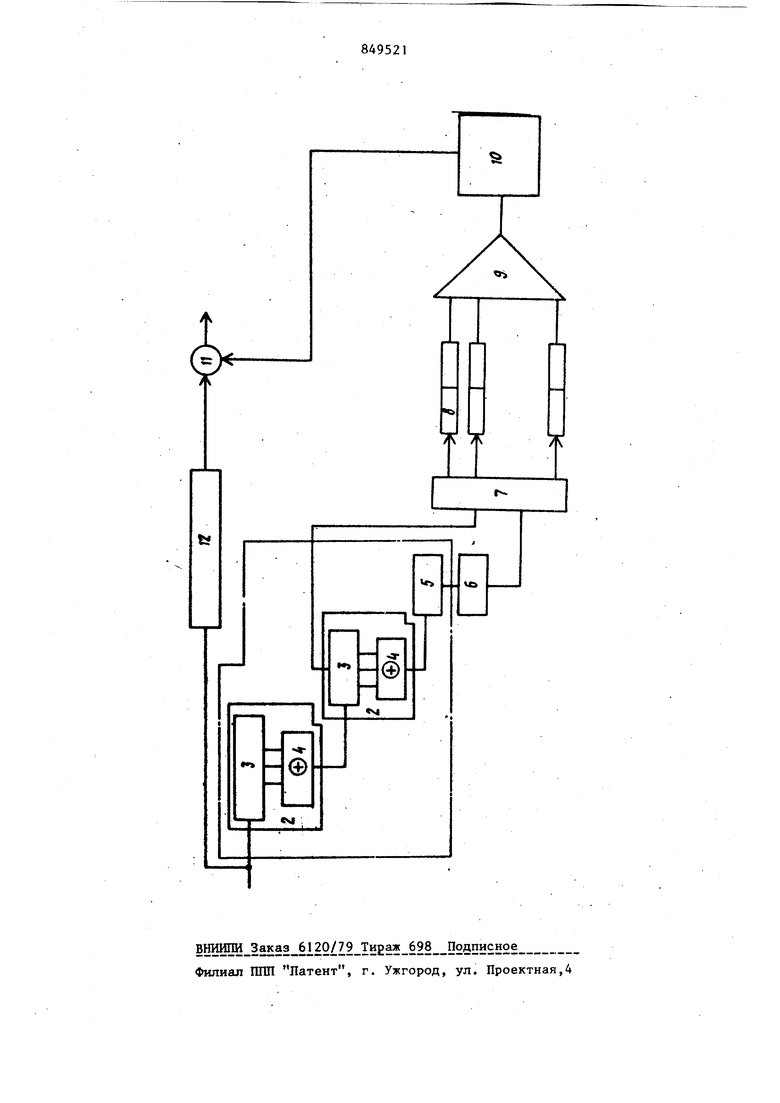

Изобретение относится к системам телеграфной связи и передачи данных и может использоваться для цикловой синхронизации и фазового пуска в сис темах передачи дискретной информации, в которых используются групповы корректирующие, в частности, каскадные коды. Известно устройство для цикловой синхронизации, содержащее объединенные по входу регистр задержки и узел обнаружения ошибок, выход которого подключен к дешифратору, и счетчик Однако это устройство облагает недостаточными помехоустойчивостью и быстродействием. Цель изобретения - повышение помехоустойчивости и быстродействия устройства. Цель достигается тем, что в устройство дая цикловой синхронизации , содержащее объединенные по входу регистр задержки и узел обнаружения ошибок, выход которого подключен к дешифратору и счетчик, введены коммутатор, k-1 счетчиков, пороговый блок, генератор импульсов и сумматор, а узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена и регистра, причем другой выход узла обнаружения ошибок через коммутатор подключен к входам k счетчиков , выходы которых через последовательно соединенные пороговый блок и генера тор импульсов подключены к входу сумматора, другой вход которого соединен с выходом регистра задержки а выход дешифратора подключен к другому входу коммутатора. На чертеже приведена структурная, электрическая схема предлагаемого устройства. Устройство для цикловой сихронизации содержит узел 1 обнаружения ошибок, выполнецный из двух последовательно соединетшх фильтров 2 Хаффмена, каждый из которых- сое . 3 трит из регистра 3, сумматора 4 и регистра 5, дешифратор 6, коммутатор 7, Ьсчетчиков 8, пороговый блок 9, генер атор 10 импульсов, сумматор 11 и регистр 12 задержки. Устройство работает следующим образом. Входная последовательность сформи рована в виде суммы по модулю 2 трех пойледовательностей - информационного кодового слова, последовательности Cg, переводящей кодовое слово в смежный класс, соответствующий ном ру кодового слова в сообщении и последовательности С, нарушающей циклические свойства йсходоого кода. Формирование передаваемой последовательности производится по следующему принципу. Все кодовые слова, входящие в сообщение, переводятся в последовательность смежных классов путем сло жения по mod 2 1-го слова (n,k) код с полиномом С - последовательность, нарушающая циклические свойства кода и может быть,наприме .0 .0. О,. . О 1. ; Cnfvvпoлинoм(n-l) выV- - YT W бирается следующим образом. Устанавливается однозначное соот ветствие между номером кодового сло ва 1 и полиномом С|))Степени (k-1)) где k 1од,М, N - число слов в сооб щении .В простейшем случае полином Cg(x) может быть просто двоичной записью номера 1. Учитывая, что при прохождении фильтров Хаффмена в приемном устройстве номера циклически сдвигаются, целесообразно этот сдвиг учитывать при формировании. Далее полином С)кодируется циклическим кодом (n,k). Полученный полином и есть полином )- Если проверочные многочлены h(x){n,k)- кода и h (х) (п, k) - кода не имеют общих множителей, то в результате сложения слов (n,k) и (n,kO - кодов будет получено слово циклического (n.) кода. Естественно, что при зтом величина (kt-k) должна быть меньше п. В случае, когда исходный (n,k) - код является кодом ВЧХ. В зтом случае код (n,kM может быть выбран таким образом, чтобы суммарный код также являлся кодом ВЧХ, и следовательно, имел бы вполне определенное гарантированное кодово расстояние. Входная последователь4ность, сформированная в виде суммы по модулю два трех последовательностей, поступает на регистр 12 задержки, а также на два последовательно соединенных фильтра 2 Хаффмена. 8первом фильтре Хаффмена вычисляется синдром исходного кода, а во втором - синдром последовательности Cg, при этом бит синдрома получается немедленно после поступления очередного бита информации. При поступлении безошибочного слова в регистре 5 заш-гсана комбинация с , соответствующая преобразованной фильтрации 2 Хаффмена последовательности С, а в.регистре 3 второго фильтра 2 Хаффмена - номер кодового слова 1. Дешифратор 6 при обнаружении комбинации С выдает сигнал в коммутатор 7, который записывает в один из счетчиков 8 номер кодового слова из регистра 3. Объем счетчиков 8 выбирается равным произведению числа кодовых слов в сообщении на число бит в кодовом слове. На счетчики 8 постоянно поступают такты с частотой поступления информации. При приходе очередного неискаженного слова коммутатор 7 записывает его номер в следующий счетчик 8. Если в первом и во втором случаях номера записаны правильно, то,к моменту записи второго номера в первом счетчике окажется то же число. При приходе последнего бита сообщения те счетчики 8, в которые были приведены записи в моменты, соответствующие границам слов, выдадут сигналы переполнения и, если их окажется больше выбранного порога порогового блока 9, то это будет сигналом циклового фазирования, по которому генератор 10 импульсов вырабатывает последовательность Cg®C. Регистр 12 задержки выбирается равным длине сообщения и в следующий за срабатыванием порогового блока 9 такт первый бит сообщения поступит с его выхода. На сумматоре 11 производится снятие последовательности C-bCg, и с его выхода поступает информация в виде исходного кода. При ,3том на вход устройства может поступать следующее сообщение.Число счетчиков 8-V и порог w порогового, блока 9определяется параметрами канала свя-. зи, кода к требованияьш по вероятности синхронизации.

Предлагаемое устройство обеспечивает цикловую синхронизацию сообщений без введения дополнительной избыточности для определения начала сообщения или границ слов каскадного кода. Проверка условий правильного приема . W или более слов из N без требования приема этого числа слов подряд обеспечивает возможность синхронизации при более высоком уровне помех в канале связи.

Формула изобретения

Устройство для цикловой синхронизации, содержащее объединенные по входу регистр задержки и узел обнаружения ошибок, выход которого подключен к дешифратору и счетчик, о т личающееся тем, что, с целью повышения помехоустойчивости

и быстродействия, введены коммутатор k-1 счетчиков, пороговый блок, генератор импульсов и сумматор, а узел обнар ужеИия ошибок выполнен в виде двук последовательно соединенных фильтров Хаффмена и регистра, причем другой выход узла обнаружения ошибок через коммутатор подклочен к входам k счетчиков, выходы которых ,через последовательно соединенные пороговый блок и генератор импуль- . сов подключены к входу сумматора, другой вход которого соединен с выходом регистра задержки, а выход дешифратора подключен к другому вход коммутатора.

Источники информации, принятые во внимаЕше при экспертизе

Авторы

Даты

1981-07-23—Публикация

1978-12-06—Подача