(54) УСТРОЙСТВО ДЛЯ ПРОВЕДЕНИЯ МАТРИЧНЫХ ИСПЫТАНИЙ МИКРОЭЛЕКТРОННЫХ СХЕМ

1

Изобретение относится к автомати ке и вычислительной технике и предназначено для исследования и оптимизации параметров микросхем и допусков на них па критерию процента выхода годных микросхем любых безынерционных схем в статическом режиме.

Известны устройства для проведения матричных испытаний радиоэлектронных схем.

Матричные испытания в этих устройствах имеют своей целью определение количественных характеристик параметрической надежности исследуемых устройств, определение двумерных сечений области работоспособности, оптимальных сечений допусковой области, максимально возможных диапазонов изменения каждого параметра, их оптимальных значений и фиксации этих значений в физической моделисх,емы

PI и Г23.

Недостатки этих устройств заключаются в отсутствии анализа промежуточных результатов матричных испытаний и отсутствии оптимизации внутренних параметров исследуемых схем, а также в недостаточной точности, обусловленной возможностью исследования влияния на выходные парамет-/

ры схемы одновременного изменения только двух параметров компонентов. В реальных условиях отклонения выходных параметров схемы являются функцией одновременного изменения всех параметров компонентов. Кроме этого, этим устройством не учитываются законы распределения входных и выходных параметров, корреIdляционные связи между параметрами компонентов, всегда имеющие место для интегральных схем, а также степень влияния отклонения каждого входного параметра на выходные па15раметры.

Наиболее близким к предлагаемому является устройство, содержащее блок управления, выход оторого подключен к управляющим входам дат20чика случайных чисел, блоков формирования тестовых сигналов, моделирования, контроля, построения сечений области работоспособности вычислительных блоков, накопителей,

25 элемента И,, блока установки номинальных значений и детектора влияния параметров, первый вход которого соединен с первым выходом генератора тактовых импульсов, остальные выходы которого пЬдключены к

30

первым входам блоков коммутации, контроля и установки номинальных значений, второй вход блока коммутации соединен с выходом блока перебора реализации, вход которого связан с выходом датчика случайных чисел, выход блока коммутации подключен к первому входу блока моделирования, второй вход которого связан с выходом блока формирования тестовых сигналов, а выход - с вторым входом блока контроля, выход которого связан со входом анализатора реализации, первый выход которого соединен со входом блока построения сечений области работоспособности, подключенного выходом через первый вычислительный блок ко второму входу блока установки номинальных значений, подключенного выходами ко второму входу блока управгвния и детектору влияния параметров, связанного выходом с первым входом в.торого- иы ислительного блока, вторые в}4одн .которого связаны с выходами н.акопителей подключенных входами к выходам элемента И, входы которых и третий вход блока управления соединены- соответственно со вторым и выходами ансшизатора реализации зЗ . :

Однако такое устройство обладает недостаточным быстродействием,, так как необходимое число начальных- случайных векторов, для которых опре-. деляется выполнение условий райотоспоробности и проводится попарный . случайный перебор всех параметров ; для нахождения номинальных значений параметров, определяемое по формуле

. л е-1 п hfc

N 2-g7-en -

где п - число квантуемых параметров схемы;

t - число квантов, на которое разбит диапазон возможных изменений каждого параметра; (1-ck-) - заданная достоверность

того, что полученные данные при испытаниях объема N.. отличались бы от истинных (т.е. при полном переборе всех комбинаций квантов параметров N) не больше, чем на t

- заданная ошибка испытаний, является чрезмерно большим.

В отличие от схем на дискретных элементах в интегральных схемах уровень технологии определяет лишь вероятность попадания значения данного параметра усомпонента в заданну область при выбранных номинальных значениях параметров компонентов схем.

Таким образом, параметры компонентов являются случайными величинами, характеристики которых могут быть заданы только статистически. Следовательно, этап функционального синтеза должен быть выполнен статистическим синтезом. Устройство учитывает случайные распределения параметров отдельных компонентов и корреляционных связей между ними -и их влияние на распределение выходных параметров интегральных схем-, т.е. на их разброс от схемы к , позволяет сделать вывод, что требования к компонентам могут быть менее жесткими и, следовательно, процент выхода годных схем при,их производстве более высоким. Однако .помимо указанного выше недостатка такого устройства, заключающегося в необходимости использования большого числа начальных случайных векторов, следует отметить, что это устройство также не учитывает взаимосвязанность номиналов параметров исследуемых схем,допусков на них и процента выхода годных микросхем, что снижает точность получаемых устройством результатов.

Цель изобретения - повышение быстродействия и точности устройства.

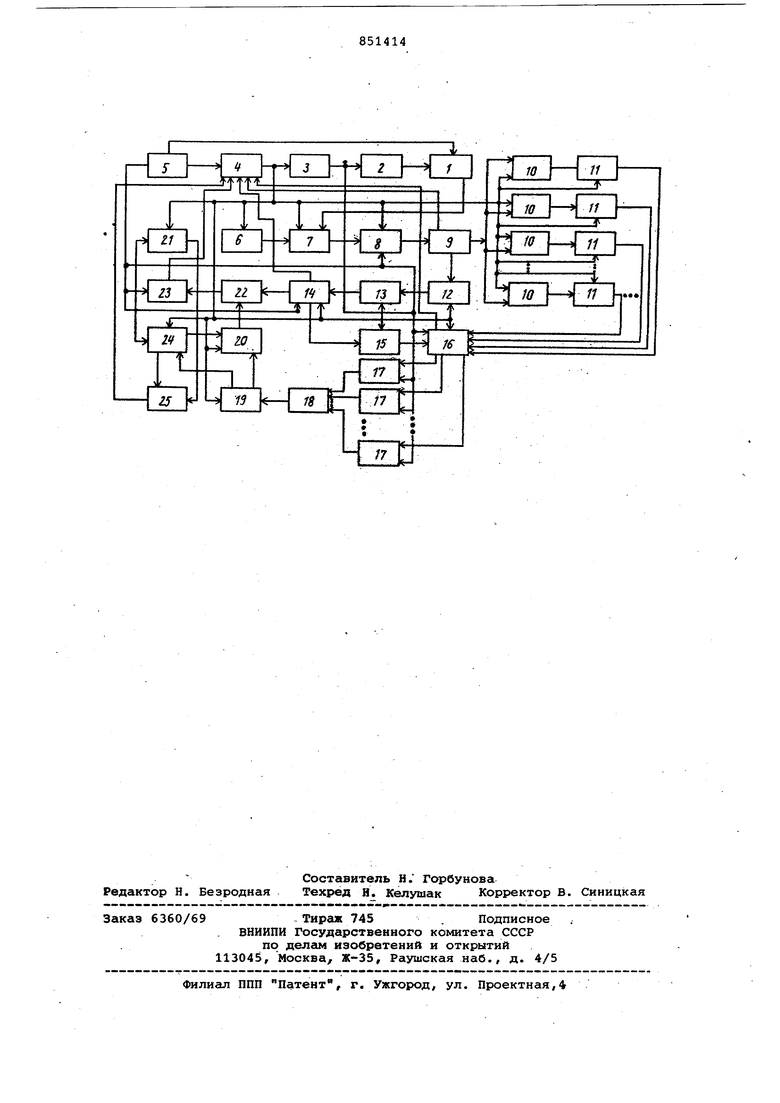

Поставленная цель достигается тем, что в устройство для проведения матричных испытаний микроэлектронных схем, содержащее блок управления, соединенный первым выходом со входом блока определения коэффициентов влияния через включенные последовательно датчик случайных чисел, блок перебора реализаций, блок коммутации, блок моделирования, блок контроля, анализатор реализаций, блок формировния сечений области работоспособност первый вычислительный блок, блок установки номинальных значений параметров, второй выход которого соединен с первым входом блока управления, а второй вход - с первым выходом генератора импульсов, подключенного вторым выходом ко второму входу блока коммутации, а третьим выходом - к третьему входу блокэ управления, подсоединенного первым выходом ко второму входу блока моделирования, .второму входу блока контроля входу блока формирования тестовых сигналов, третьему входу блока установки номинальных значений параметров, второму входу первого вычислительного блока, второму входу блока определения коэффициентов влия,ния, второму входу блока формирования-сечений области работоспособности, первому входу второго вычислительного блока, первым входам накопителей и первым входам блоков совпадения, вторые входы которых соединены ,со вторым выходом анализатора реа.лизаций-, а выходы - со вторыми входами соответствующих блоков совпадения, выходы которых подключены ко ,вторым входам второго вычислительно го блока, соединенного третьим входом с третьим входом блока контроля и с первым входом генератора импуль сов, четвертым входом - с выходом блока определения коэффициентов вли яния, А первым выходом - с четвертьв входом блока управления, пятый вход КОТОРОГО подключен к третьему выходу анализатооа реализаций, введены блок памяти, блок уставок, бло выбора максимума ДОПУСТИМЫХ реали{заиий., блок разности, блоки сравнения и последовательно включенные эл мент И, счетчик годных реализаций, компаратор, ключ и блок уставок,сое диненный вторым входом с первым вых дом генератора импульсов, а выходом с шестым входом блока управления, седьмой вход которого подключен к выходу блока разности, соединенного первым входом с первым блок максимума допустимых реализаций, а вторым входом - с выходом блока памяти, подключенного первым входом к первому выходу блока управления, а вторым входом - ко второму выходу блока выбора максимума допусти ос реализаций, первый вход которого сое дивен со вторым выходом счетчика годных реализаций, а третий выход со вторым входом компаратора, соединенного третьим входом со вторым входом счетчика годных реализаций, со вторым входом блока выбора максимума допустимых реализаций и с первым выходом блока управления,блок сравнения первыми входами подключены к выходу датчика случайных чисел, вторыми входами - ко вторым выходам второго вычислительного блока, а выходами - ко входам элемента И. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит блок 1 коммутаций, блок 2 перебора реализаций датчик 3 случайных чисел, блок 4 управления, генератор 5 - импульсов, блок б формирования тестовых сигналов, блок 7 моделирования, блок 8 контроля, анализатор 9 реализации, блоки 10 совпадения, накопители 11, блок 12 формирования сечений области работоспособности, первый вычислительный блок 13, блок 14 установки номинальных значений параметров,блок 15 определения коэф циентов алияиия второй вычислительный блок 16, блоки 17 сравнения, элемент И 18, счетчик 19 годных реализгщий, ком:паратор 20, блок 21 памяти ключ 22, блок 23 уставок, блок 24 выбора максимума допустимых реализаций, блок 25 разности. Блок 1 коммутаций представляет группу ключевых элементов, обе печнваюсцих ко№лутацик представителей квантов исследуемых элементов физической модели 7 и управляемых блоком 2 перебора реализаций,Блок 2 перебора реализаций служит для управления коммутирующими ключами. Датчик 3 случайных чисел служит для нахождения по команде с блока управления необходимого числа начальных случайных векторов, распределенных по равномерному закону и удовлетворяющих условиям работоспособности, для проведения последовательного попарного случайного перебора пapa «тpoв физической модели исследуемой схемы блока 7 для каждого начального случайного вектора, для формирования случайных векторов имеющих заданные математические ож11 Дания, соответствующие компонентам кгикдого начального случайного вектора, дисперсии и коэффициенты корреляции и распределенные по заданным законам распределения. Блок 4 управления через датчик 3 случайных квантов управляет блоком перебора реализаций, находя не-° обходимое число начальных случайных точек, удовлетворяющих условиям работоспособности, и, проводя последовательный попарный перебор параметров физической модели исследуе.мой схемы блока 7 для каждой начальной случайной точки, выдает в блок 12 формирования сеченной области работоспособности текущие номера параметров и их квантов, участвующие в переборе, по команде блока 14 установки номинальных значений параметров включает соответствующий номер кванта параметра физической модели схемы, выдает в блок- 15 определения коэффициентов влияния номинальные значения параметров компонентов , полученные для каждого начального случайного вектора, удовлетворившего условиям работоспособности, а во второй вычислительный блок 16 - данные с накопителей 11 для определения закона распределения выходного параметра, выдает команду в датчик 3 случайных чисел на формирование случайных нормально распределенных векторов с коррелированными компонентами, разрешает выдачу определенных во втором вычислительном блоке 16 границ допусков наг первые вхопы соответствующих схем совпадения, по его команде данные с выхода счетчика годных реализаций поступают на входы компаратора 20 и блока 24 выбора максимума допустимых реализаций, разрегаает подачу сигнала с компаратора 20 на вход ключа 22, сигналов с блока 24 выбора максимума допустимых реализаций в блок 21 памяти и блок 25 разности, а также сигнала с блдка 21 памяти в

блок 25 разности и координирует работу остальных блоков,

Генератор 5 тактовых импульсов используется для синхронизации блока 1 коммутации, блока 8 контроля, блока 14 установки номинальных значений параметров, второго вычислительного блока 16 и блока 23 уставок с блоком управления по заданному

ритму,

БЛОК б формирования тестовых сигналов вырабатывает для каждой конкретной физической модели схегал комплекс входных сигналов.

Блок 7 моделирования выполнен в виде платы, на которой последователно с контактами соответствующих ключевых элементов блока 1 коммутации подключены выхода квантов моделируемых параметров исследуемой схемы с начальными диапазонами изменения, обеспечивающими определение границ сечений области работоспособности этой схемы.

Блок 8 контроля преобразует любой выходной сигнал исследуемой схемы в вид и величину, удобную для обработки и анализа в анализаторе 9 реализаций.

Анализатор 9 реализаций характеризует каждую реализацию, определяя, работоспособна она или нет в соответствии с выбранными критериями работоспособности. Блоки 10 соэпадения, представленные в количестве, определяемом заданным числом уровней отклонения выходного сигнала, охватывают весь возможный диапазон изменения этого выходного сигнала- в цифровом эквиваленте.

Накопители 11 предназначены для накопления количества реализаций, при которых величина выходного сигнала (в цифровом эквиваленте) совпадают с уставкой соответствующего блока 10.

Блок 12 формирования сечений области работоспособности по данным блока 4 управления и анализатора 9 реализаций получает сечение области работоспособности для калодой пары параметров, преобразует эту информацию в вид, удобный для последующей работы, и по команде блока управления выдает ее в первый вычислительный блок 13.

Вычислительный блок 13 вписывает в каждое сечение области работоспос бностиоптимальное сечение до пусковой области, осуществляет обработку серии полученных сечений допусковой области для каждого параметра, определяя максимально возможный диапазон изменения и его оптимальное значение, и по команде блока управления сообщает это значение в блок 14, установки номингшьных значений параметров.

Блок 14 останавливает работу всего устройства на время, кратное периоду поступления тактовых пульсов, в течение которого вносит изменения в программу работы блока управления, устанавливая в блоке 7 5 полученное в результате предыдущей обработки оптимальное значение, и выдает команду на продолжение работы устройства. Блок 15 определения коэффициентов влияния параметров на основании выданных по сигналу блока управления данных о номинальных значениях параметров схемь для каждого из начальных случайных векторов, удовлетворяющих условиям работоспособности, определяет коэффициенты влияния соответствующих параметров и преобразует их в вид, удобный для последующей работы.

Второй вычислительный блок 16,

куда по сигналу блока управления

поступают значения коэффициентов влияния и данные с накопителей, определяет закон распределения выходного параметра и, используя CJHформацию о законах распределения входных параметров и корреляционных связях между ними, определяет оптимальные допуски на параметры элементов для кгикдого начального случайного вектора, т.е. границы интервалов допустимых значений по каждому из параметров исследуемой схемы, кото иле по сигнсшу с блока 4 управления поступают на первые входы соответствующих блоков сравнения 17, а 5 на основании известного коэффициента вариации определяет среднеквадратические отклонения компонентов каждого начального случайного вектора. Затем он останавливает работу д устройства на время, кратное периоду поступления тактовых импульсов, в течение которого вносит изменения в програкму работы блока 4 управления . и выдает команду на продолжение работы устройства.

5 Блоки 17 сравнения, представленные в количестве, определяемом числом элелдантов схекш, тогда, когда случайные значения компонентов коррелированных векторов совпадают с соот0 ветствукмцими интервалами допустимых значений, выдают соответствукицие импульсы.

Элемент И 18 оценивает каждую реализацию и в случае появления сигналов на всех его входах вырабатывает импульс, поступающий на счетчик 19 годных реализаций.

Счетчик 19 годных реализаций предназначен для накопления количества реализаций, при которых совокупности случайных величин соответствующих компонентов каждого начального случайного вектора (в цифровом эквиваленте) совпадают с соотствую5 щими границами интервалов допустимых

значений блоков 17 сравнения, которые он передает в номпаратор 20 и блок 24 выбора максимума допустимых реализаций по команде с блока 4 управления.

Компаратор 20 сравнивает текущее значение количества годных реализа иШ (процента годных микросхем) с некоторым наперед заданным (нижним допустимым) порогом и в случае положительной разности выдает сигнал по команде с блока 4 управления на ключ 22.

Блок 21 памяти служит для хранения нижнего допустимого значения числа годных реализаций и последующих значений после каждого следующего шага сокращения диапазонов допустимых значений параметров исследуемо схемы, которые поступают в него по сигнёшу с блока 4 управления из блока 24 выбора максимума годных реализаций и которые он по соответствующе команде блока 4 управления передает в блок 25 разности.

Ключ 22 имеет число входов и выходов , соответствукицее числу параметров исследуемой схемы. При появлении на его управляющем входе сигнала он пропускает сигнгшы, поступающие хна него из блока 14 установки номинальных значений параметров на входы блока 23 уставок границ допустимых значений.

Блок 23 уставок границ допустимых значений представляет собой логический блок с числом пар состояний соответствующих числу параметров исследуемой схемы. Каждая пара состояний характеризует нижнюю и верхнюю границу допустимых значений одного паргшетра. Компоненты первого начального случайного вектора, поступавядие на его входы, опрокидывают обе его границы в положение, в цифровом эквиваленте соответствукндее пришедшему номинальному значению каждого параметра исследуемой сх&ма. Компоненты второго случайного вектора опрокидывают одну из каждой пары его границ, причем левую (нижнхяо) или правую (верхнюю) в зависимости от того, меньше или больше соответствующая компонента второго начального случайного вектора соответствукицей компоненты первого начальиого случайного вектора. Компоненты каждого последующего качальногр случайного вектора будут опрокидывать одну из его соответствуняцих границ только в том случае, если они либо меньше соответствующей нижней, либо больше соответствующей верхней границ, полученных после прихода соответствукицих компонентов первых двух начальных случайных векторов. Затем блок 23 уставок границ допустимых значений останавливает работу всего устройства на

время, кратное периоду поступления тактовых импульсов, в течение которого вносит изменения в программу работы блока 4 управления, устанавливая новые границы допустимых изменений параметров, полученные в результате предыдущего шага, и выдает команду на продолжение работы устройства.

Блок 24 выбора максимума допустимых реализаций имеет на своем перoвом и втором выходах сигнал, в цифровом эквиваленте равный нижнему допустимому значению количества годных реализаций, которое после каждого шага матричных испытаний, заклю5чакндегося в выбрасывании совокупности начальных случайньис векторов, заменяется максимсшьным количеством годных реализаций, полученных для одного из этих векторов, которое по сигналу с блока 4 управления пе0редается в блок 21 памяти и устанавливается в качестве порогового для подачи в блок 25 разности и компаратор 20.

Блок 25 разности сравнивает зна5чения получившегося в ходе очередного шага проведенных матричных испытаний максимальное число годных реализаций с максимальным количеством годных реализаций на предыдущем шаге

0 и в случае, когда эта разность больше некоторого наперед заданного числа годных реализаций, выдает команду на проведение следующего шага матричных испытаний, в противном случае

5 выдает команду на остановку работы устройства и разрешает печать компонентов вектора (номинальных значений) и допусков на них вектора, который в текущем шаге дает максимум

0 количества годных реализаций. ,

Устройство работает следующим образом.

После пуска устройства блок 4 управления, работакяций по заданной программе, выдает команду в датчик

5 3 случайных чисел, которыЛ случайным образом выбирает кванты в соответствующем исходном диапазоне каждого параметра схеьол, разрешает выдачу сигналов о координатах первого

O случг1йного вектора в блок 2 перебора регшиэаций на срабатывание соответствующих ключевых элементов блока 1 коммутации для включения выбранных представителей квантов внутренних

5 параметров физической модели схемы в блок 7 моделирования. На вход собрайной физической модели схемы и блока б формирования тестовых сигнсшов подается комплекс входных сигналов, а блок 8 контроля и аналиОзатор 9 реализаций в соответствии с заданными ограничениями на выходные параметры схемы проводят оценку реализации (работоспособности схемы при данном наборе значений внутрен5

НИХ параметров). Сигнал с анализатора 9 реализаций поступает на блок 4 управления, который в случае неудовлетворения первого случайного вектора условиям работоспособности вьшает команду в датчик 3 случайных чисел на выбор следующего случайного вектора, в противном случае дает разрешение в датчик 3 случайных чисел с поступлением следукицих тактовых импульсов на проведение последовательного попарного случайного перебора квантов первого и второго внутренних параметров схемы,причем остальные параметры представлены своими номинальными значениями, являющимися координатами случайного вектора, удовлетворившего условиям работоспособности.

Блок 4 управления дает разрешение на параллельное считывание результатов оценки работоспособности каждой ситуации при попарном случайном переборе с анализатора 9 реализаций на блоки 10 совпадения, каждый из которых настроен на определенное число, в цифровом выражении эквивалентное соответствующим квантам, на которое разбит весь возможный диапазон изменения выходного параметра испытуемого устройства. На выходе элемента И, у которого в данной регшизации число совпадает с поступившим с анализатора 9 реализаций, появляется признак совпащения, разрешающий прибавление единицы в связанный с этим элементом накопитель 11.

Результаты оценки работоспособности каждой ситуации попарного случайного перебора и координаты кваитов параметров, участвукицих в реализации, выдаются также в блок 12 формирования сечений области рабо- тоспособности. Полученное таким образом двумерное сечение области работоспособности по команде блока-4 управления передается в первый вычислительный блок 13 в виде, удобном для его работы, первый вычислительный блок 13 вписывает в каждое двумерное сечение области работоспособности оптимальное двумерное сечение допусковой области. Параллельно с работой первого вы ислительного блока 13 продолжается случайный перебор квантов первого и третьего внутренних параметров схемы, первого и четвертого и т.д. Таким образом, получаем серию оптимальных двумерных сечений допусковой-области относительно первого параметра. Первый вычислительный блок 13 проводит совместную обработку всей серии сечений определяя максимально допустимей диапазон изменения первого параметра и его оптимальное для этой серии сечений номинальное значение. При получении сечения области работоспособности первого и последнего параметров первый вычислительный блок 13 останавливает работу устройства до момента выдачи оптимального номинального значения первого параметра для первого случайного вектора, удовлетворившего условиям работоспособности. По окончании обработки серии сечений первого параметра с остальными по команде блока 4 управления это значение сообщается в блок 14 установки номинальных значений параметров, который преобразует номер кванта, соответствуюпшй оптимальному значению первого параметра в вид, удобный для изменения програмгиы работы блока 4 управления, и блокирует работу устройства на время своей работы и время включения представителя кванта первого параметра, соответствующего определенному номинальному значению (время блокировки кратно периоду поступления тактовых импульсов), после чего с поступлением следующих тактовых импульсов дает команду на продолжение работы устройства.

Аналогичным образом проводится попарный случайный перебор второго внутреннего параметра схемы со всеми остальными, кроме первого, и определяется его оптимальное номинальное значение, затем третьего со всеми остальными, кроме первого и второго параметров и т.д.

По окончании попарного случайного перебора всех параметров для первого случайного вектора, удовлетворившего условиям работоспособности, и нахождении оптимальных номинальных значений последние по команде блока 4 управления поступают в блок 15 определения коэффициентов влияния, где находятся коэффициенты влияния каждого входного параметра схемы на выходной параметр и по команде блока 4 управления передаются во второй вычислительный блок 16. в результате всех циклов испытаний для первого случайного вектора в накопителях 11 собираются числа, представляющие в целом гистох-рамму, т.е. дифференциалъную функцию распределенная выходного сигнала испытуемого устройства, причем информация с накопителей 11 по сигналу блока 4 управления поступает во второй вычислительный блок 16, который определяет закон распределения выходного параметра и на основании данных о коэффициентах влияния входных параметров закон распределения входных парс1метров и корреляционных связей между ними определяет оптимальные допуски на параметры схемы для первого случайного вектора, удовлетворившего условиям работоспособности, а на основании данных о коэффициенте вариации определяет среднеквадратические отклонения компонентов первого случайного вектора, которые поступают вблок 4 управления для изменения программы его работы. Блок 4 управления выдает 1Лэманду в датчик 3 случайных чисел на формирование случайных нормально распределенных ..векторов с корреЛированными компонентами, причем компоненты этих векторов обладают заданными из второго вычислительного блока: 16 среднеквадратическими отклонениями .и связанйг известными коэффициентами корреляции. Сигналы о случайных квантах парс1метров с выхода датчика случайных чисел поступают на первые входы соответствующих блоков 17 сравнения на вторые входы которых подаются из второго вычислительного блока 16 определенные там допуски, т.е. значения границ интервалов допустимых значений по каждому из параметров. Когда случайное значение параметра совпадает с интервалом допустимых значений, на выходе соответствуюйШх блоков 17 сравнения появляется сигнал. При наличии таких сигналов на всех входах элемента И 18 последний вырабатывает импульс, поступающий на счетчик 19 годных реализаций. В результате серии из п испытаний для первого случайного вектора в счетчи ке 19 годных реализаций накапливается некоторое число, отражающее процент выхода годных микросхем, ко торые в виде, удобном для последую щей работы, по команде с блока 4 уп равления подается на первый вход компаратора 20, на второй вход кото рого поступает некоторое заданное .начальное значение процента выхода ГОДНЫХ микросхем (годных реализаций из блока 24 выбора максимума допуст мых реализаций, соответствующее ниж нему допустимому порогу. В случае положительной разности между сигналами на первом и втором входах компаратора на выходе последнего появляется сигнал, открывающий ключ 22. Номинальные значения первого началь ного случайного вектора, поступающие из блока 14 установки номинальных значений параметров, проходят через ключевой элемент на соответствующие входы блока 23 уставок границ допустимых значений и опрокидывают соответствующие пары состояний, характеризукноие его границы по каждому параметру, в положения, соответствукяцие в цифровом эквиваленте пришедшим номинальным значениям. Компоненты второго случайного начального вектора опрокидывают одну из калсдой пары его границ, причем левую (нижнюю) нли правую (верхнюю) в завнсимрсти от того, меньше или больше соответствующая компонента второго начального случайного вектора соответствующей компоненты первого случайного вектора. Данные о номинальных значениях каждого следующего начального случайного вектора при положительной разности в компараторе 20 и появлении сигнала на управляющем входе ключа 22 проходят через ключ 22 и опрокидывают одну из каждой пары его границ только в том случае, если соответствующие компоненты либо меньше соответствующей нижней, либо больше соответствующей верхней границ, полученных после прихода предьадущего вектора. По окончании испытания М начальных случа.йных векторов для кг1ждого из KOTOpfcuc проведено п реализаций в соответствии с заданным законом распреде чения его компонент, дисперсиями и коэффициентами корреляции в блоке 23 уставок границ допустимых значений элементов формируются новые границы, которые/ естественно, уже предыдущих. Затем блок 23 уставок границ допустимых значений останавливает работу всего устройства на время, кратное периоду поступления тактовых импульсов, в течение которого вносит изменения в программу работы блока 4 управления, устанавливая новые границы допустимых значений параметров, полученные в результате последнего шага проведения матричных испытаний, и вьщает команду о на продолжение, работы устройства. Вместе с формированием новых границ допустимых значений параметров сигнал со счетчика 19 годных реализаций для каждого начального случайного вектора поступает кроме компаратора 20 также на вход блока 24 выбора максимума допустимых реализаций и опрокидывает его в том случае, если последующее значение больше предыдущего. Затем по сигналу с блока 4 управления максимальное значение годных реализаций устанавливается как пороговое для следующей серии из N начальных случайных векторов (следующего шага проведения матричных испытаний) и подается на второй вход компаратора 20 и одновременно засылается в блок 25 разности и блок 21, откуда по сигналу с блока 4 управления предыдущее пороговое значение блока 24 выбора максимума допустимых реализаций поступает на второй вход блока 25 разности. В случае, если разность между сигналами на первом и втором входах блока 25 разности больше некоторого наперед заданного числа годных реализаций, отражающего достоверность и ошибку матричныз4 испытаний, на выходе последнего появляется сигнал, поступающий на вход блока 4 управления , куда с приходом следующих тактовых импульсов поступают полученные в ходе преды1яущего шага проведения матричных испытаний новые.

олее узкие границы допустимых зменений параметров, и цикл испытаий исследуемой схемы продолжается. огда указанная разность в блоке 5 разности меньше наперед заданного исла годных реализаций, на выходе оследнего появляется сигнал другой олярйости, который поступает на блок 4 управления и разрешает печать номинальных значений и допусков комонентов того начального случайного вектора, который в ходе последнего ага матричных испытаний дает наибольшее значение количества годных реализаций (процент выхода годных микросхем) и останавливает работу устройства.

Таким образом, введение в устройство для проведения матричных испытаний микроэлектронных схем элемента И, счетчика годных реализаций, компаратора, ключа, блока уставок, блоков сравнения, блока памяти,блока выбора максимума допустимых реализаций и блока разности выгодно отличает предлагаемое устройство для проведения матричных испытаний микроэлектронных схем от известного так как, во-первых, позволяет сократить необходимое число начальных случайных векторов и тем самым повысить производительность работы устройства и,.во-вторых, обеспечивает учет неразрывной связи номинальных значений, допусков на них и процента выхода годных микросхем, проявляющийся в ходе проведения комплексных матричных испытаний, а также позволяет получить оптимальный вектор номинальных значений параметров исследуемой схемы и допусков на них, что увеличивает точность устройства.

Формула изобретения

Устройство для проведения матричных испытаний микроэлектронных схем, содержащее блок управления, соединенный первым выходом со входом блока определения коэффициентов влияния через включенные последовательно датчик случайных чисел, блок перебора реализаций, блок коммутации, блок моделирования, блок контроля, анализатор реализаций, Ьлок формирования сечений области работоспособности, первый вычислительный блок, блок установки номинальных значений. napaiyieTpoB, второй выход которого соединен с первым входом блока управлений, а второй вход - с первым выходом генератора импульсов, подключенного вторым выходом ко второму входу блока коммутации, а третьим выходом - к третьему входу блока управления, подсоединенного первым выходом ко второму входу блока моделирования, второму входу блока контроля, входу блока формирования тестовых сигналов, третьему входу блок установки номинальных значений параметров , второму входу первого вычистельного блока, второму входу блока определения коэффициентов влияния, второму входу блока формирования сечений области работоспособности, певому входу второго вычислительного блока, первым входам накопиг елей и первым входам блоков совпадения,вторые входы которых соединены со вторым выходом анализатора реализаций, а выходы - со вторыми входами соотвствующих блоков совпадения, выходы которых подключены ко вторым входам второго вычислительного блока, соединенного третьим входом с третьим входом блока контроля и с первым входом генератора импульсов, четвертым входом - с выходом блока определения коэффициентов влияния, а первым выходом - с четвертым входом блока управления, пятый вход которого подключен к третьему выход анализатора регшизаций, отличающееся тем, что, с целью повышения быстродействия и точности устройства, в него введены блок памяти, блок выбора максимума до- пустимых реализаций, блок разности, блоки сравнения и последовательно включенные элемент И, счетчик годных реализаций, компаратор, ключ и блок уставок, соединенный вторым входом с первым выходом генератора импульсов, а выходом - с шестым входом блока управления, седьмой вх которого подключен к выходу блока разности, соединенного первым входом с первым выходом блок максимума допустимых реализаций, а вторым входом - с выходом блока памяти,.подключенного первым входом к первому выходу блока управления, а вторым входом - ко второму выходу блока выбра максимума допустимых реализаций, первый вход которого соединен со вторым выходом счетчика годных реализаций, а третий выход - со вторым входом Компаратора, соединенного третьим входом со вторым входом счетчика годных реализаций, со вторым входом блока выбора максимума допустимых реализаций и с первым выходом блока управления, блоки сравнения первыми входами подключены к выходу датчика случайных чисел, вторыми входами - ко BTopbJM выходам второго вычислительного блока, а выходами - ко входам элемента И.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 383510, кл. G 06 F 15/46, 1968.

2.Авторское свидетельство СССР № 516048, кл. G 06 F 15/46, 1976.

3.Авторское свидетельство СССР по заявке 2630041/18-24,

кл. G 06 F 15/46, 1978 (прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проведения матричных испытаний микроэлектронных схем | 1979 |

|

SU868778A2 |

| Устройство для проведения матричных испытаний радиоэлектронных схем | 1978 |

|

SU765813A1 |

| Устройство для проведения матричных испытаний радиоэлектронных схем | 1975 |

|

SU516048A1 |

| Оптимизатор | 1981 |

|

SU983650A1 |

| Устройство для определения границы области работоспособности технических объектов | 1975 |

|

SU558280A1 |

| Устройство для прогнозирования параметрической надежности радиоэлектронных устройств | 1977 |

|

SU732894A1 |

| УСТРОЙСТВО для ПРОВЕДЕНИЯ МАТРИЧНЫХ ИСПЫТАНИЙ СТАТИСТИЧЕСКИМ СПОСОБОМ | 1966 |

|

SU183830A1 |

| Устройство для определения параметрической надежности радиоэлектронных устройств | 1974 |

|

SU522504A2 |

| Устройство для определения требо-ВАНий K пАРАМЕТРАМ ТЕХНичЕСКиХуСТРОйСТВ | 1979 |

|

SU798641A1 |

| Устройство для определения параметрической надежности радиоэлектронных объектов | 1988 |

|

SU1647583A2 |

Авторы

Даты

1981-07-30—Публикация

1979-11-16—Подача