(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ТРЕБОВАНИЙ К ПАРАМЕТРАМ ТЕХНИЧЕСКИХ- УСТРОЙСТВ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем | 2017 |

|

RU2674281C1 |

| Устройство для прогнозирования надежности | 1977 |

|

SU746349A2 |

| АДАПТИВНАЯ АНТЕННАЯ РЕШЕТКА | 1991 |

|

RU2014681C1 |

| Устройство для прогнозирования надежности | 1980 |

|

SU928267A2 |

| Устройство для определения амплитудно-фазовых характеристик системы регулирования | 1978 |

|

SU930268A1 |

| Устройство для измерения корреляционногоОТНОшЕНия дВуХ СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU851420A2 |

| Устройство для прогнозирования надежности | 1980 |

|

SU894620A1 |

| ЦИФРОВОЙ ИНТЕЛЛЕКТУАЛЬНЫЙ РЕКУРСИВНЫЙ ФИЛЬТР | 2007 |

|

RU2357357C2 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

1

Изобретение относится к вычислительной технике и автоматике и может быть использовано при разработке и построении систем повышения надежности.

Известно устройство, содержащее, анализатор случайного процесса, коррелятор, блок возвеления в степень , блок дифференцирования, сумматор, блок управления, вычислитель ный блок, блок произведения и регистрирующий блок 1.

Недостатком известного устройства является узкая область его применения в силу того, что устройство позволяет прогнозировать только надежность технических устройств (ТУ), т.е. решать прямую задачу теории надежности. Алгоритм,положенный в основу работы устройства, используют для решения обратной задачи теории надежности - синтеза свойств ТУ с учето; заданных требований к его надежности.

Известно также устройство, позволяющее прогнозировать надежность, ТУ и синтезировать требования к их свойствам, содержащее коррелятор, анализатор случайного процесса, вычислительный блок, блок возведения в степень, блок управления, блок произведения, блок памяти, блок дифференцирования, сумматор, регистрирующий блок , блок транспонирования

матриц и дополнительный вычислительный блок 2.

Недостатком этого устройства являются большие ошибки в определении синтезируемых свойств ТУ. Задача

синтеза требований к свойствам ТУ, исходя из требований к надежности ТУ, является некорректной и решение ее методом квадратных корней или г тодом Гаусса приводит к получению

результата, имеющего большие погрешности.

Цель изобретения - повышение точности устройства. . Поставленная цель достигается

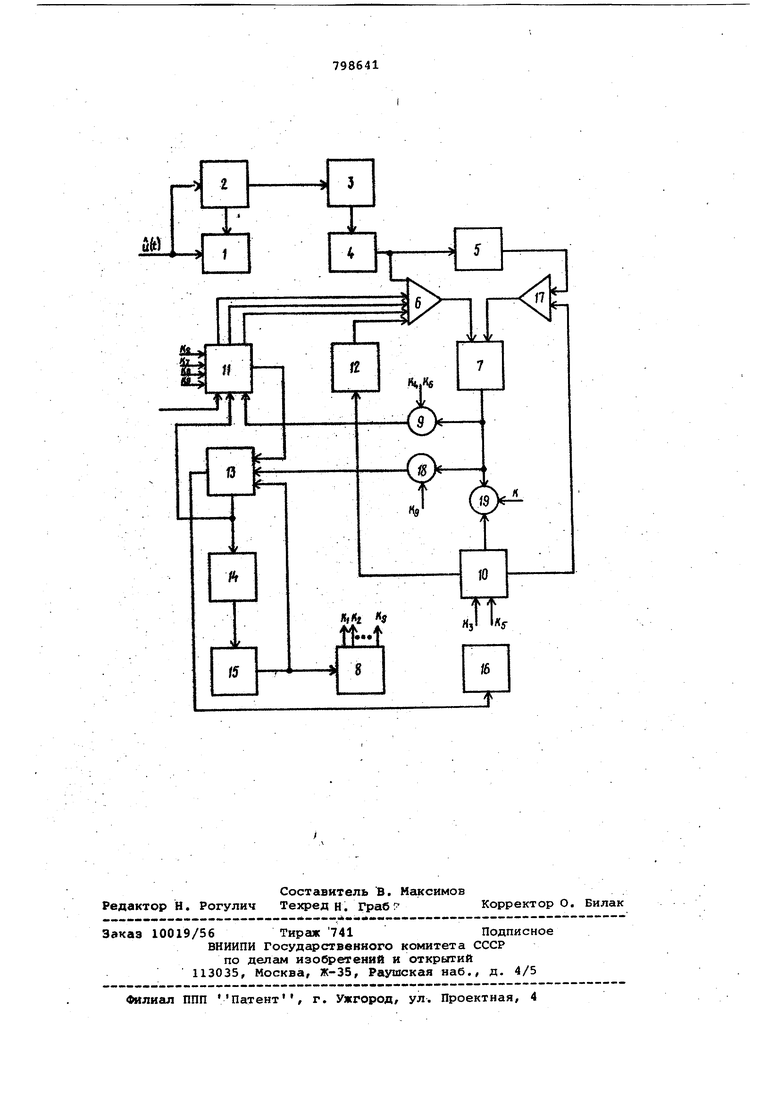

тем, что в устройство для определения требований к параметрам технических устройств, содержащее последовательно соединенные коррелятор, анализатор случайного процесса, вычислительный блок, блок возведения в степень и блок транспонирования матриц, блок управления, первый сумматор, блок памяти, блок произведения, блок обращения матриц, я регистратор, введены три элемента И, два зпе б&ята ИЛИ, блок формирования « Лтрицу, агорой сумматор и блок сравнения,, четыре входа блока п 1мяти соединены с соответствующими выходами блока управления, пятый вход с ВХОДОМ устройства, шестой вход с перзым выходом второго сумматора,, седьмой- вход через первый элемент И - с выходом блока произведения, три выхода через первый элемент ИЛИ - с первым входом блока произведения, а четвертый выход - с первым BxojioM второго сумматора, второй вход которого через второй элемент И соединен с выходом блока произведения, соединенным через третий элемент И с первым входом блока формирования матриц, первый выход которого соединен с первым входом второго элемента ИЛИ, а второй выход - через блок обраияения матриц с четверть ; входом первого элемента ИЛИ, третий вход второго cy iMSTcpa соединен с выходом влсжа сравпеняя, выходы блока управления соединены с входами первого, второго и третьего элементов И н со laToptai и третьим входами блока формирования матриц, а вход - с выходом блока сравнения, вх-од которого соединен через первый сумматор с первим выходом второго сумматора, второй выход которого соединен с регистратором, вход блока транспонирования г матриц соединен с пятым входе первого элемента ИЛИ а выход - со вторьм входом второгоэлемента ИЛИ, подключенного выходом ко второму входу блока произведения. На чертеже представлена блок-схема устройства. Устройство содержит коррелятор 1, анализатор 2 случайного процесса, вычислительный блок 3, блок 4 возведения в степень, блок 5 транспо-; гнирования матриц, первый элемент ИЛИ б, блок 7 произведения, блок 8 управления, первый элемент И 9, блок 10 формирования матриц, блок 11 памяти, блок 12 обращения матриц, второй 13 и первый 14 сумматоры, блок 15 сравнения, регистратор 16, второй элемент ИЛИ 17 и второй 18 и третий 19 элементы И, Устройство аппаратурно,реализует выражение R(n) (x) -агл (X), (1) где R(n) - функция надежности или вероятность того, что за время лГ ни разу внешнее по отношению к .эксплуатируемому устройству воздействие не превышает допустимого; FA(х) - функция распределения сопротивляемости, обоснованная и исчерпывающая характеристика допустиопHb ле ин ус фу РЛ че ал пр пр фо Ч к ТО ал яв оп жи (2 вм ни гд Пе вв ри мого предела величин внешнего воздействия, приводящего устройство к отказу; - наибольшее случайное воздействие на интервале времени, равном периоду корреляции; Рл(и) - функция распределения наибольших значений внешнего воздействия; п - число периодов корреляции внешнего воздействия п t/Atr период корреляции исследуемого сигнала; условная функция распределения внешнего воздействия относительно гипотезы о том, что предельное (допустимое) значение воздействия принадлежит элементарному отрезку x+dx; вероятность элементарной гипотезы, При синтезе свойств ТУ устройство. ределяет из выражения (1) диакретie значения 3Fjj(x) функции распредения сопротивляемости. Исходной формацией в этом случае для работы тройства являются заданные значения нкции надежности R(n) и функции (и) распределения наиболь их знаний внешнего воздействия U, При этом устройство .реализует горитм, вытекающий из следующих: еобразований. 8 уравнении В - Ч г , едставляющем компактную матричную рму записи уравнения (1), вектор Р5{X) характеризует требования синтезируемому ТУ, Эффективным меДСМУ1 решения системы линейных гебргьических уравнений вида (2) ляется метод Зейделя, Для обеспечения положительной еделенности матрицы задачи умнолевую и правую часть уравнения ) на матрицу В. В результате сто уравнения (2) решают уравнеЧ- в- г,(3) В - транспонирования матрица в FU(X) ; г4Кл(п)- вектор правой части уравнения (2) - функция надежности, Введем обозначения В Ф (4) (5) епишем уравнения (3) с учетом денных обозначений Ф- Ч с(6) В векторно-матричной форме алгом решения системы (6) методом Зейделя на {п+1)-ом шаге итерации ц)П+-| д -vf + (7) где искомый вектор приближе ния решения на текущем (п+1)-ом шаге итерации то же, на предБщущем ша ге итерации. 5)« О 0.,.0 -нижняя треугол %1 i... О ная матрица (8 m i VM2L4 v«v J-tvM О О Ф.. . .., -верхняя треу- гольная матрица (9 о о о,, ,0 которые получаются из исходной мат рицы ф , Устройство работает следующим образом. Информация о нагрузках на исследуемое ТУ, представленная в вид сигнала U(t), поступает на вход коррелятора 1 и на вход анализато 2, В корреляторе 1 определяется автокорреляционная функция исследу мого сигнала и по ней вычисляется период его корреляции AT, Период корреляции задается анализатору 2, в котором исследуемый сигнал разбивается на .промежутки й.Ги затем в каждом из полученных промежутков определяется наибольшее значение. По выбранным значениям максимумов из интервалов разбиения исследуемого сигнала блоком 3 опре деляется условная вероятность Р(Л(Х),. которая поступает в блok 4, где возводится в степень п. Информ ция с выхода блока 4 представляет собой матрицу В уравнения (3), кот рая в блоке 5 преобразуется в матрицу в .С выхода блоков 4 и 5 через элементы б -и 17 матрицы В и поступают в блок 7, Полученная в р зультате перемножения матрица Ф по сигналу К1 блока через элемент И 1 засылается в блок 10, где преобразуется в две треугольные матрицы А и D,. Блоки 5 и 10 практически идентичны и выполнены по единой схеме. Они состоят из двух счетчиков (целочисленных сумматоров) для формирования текущих номеров строки i и столбца j матрицы, блока пересьш чисел для выбора чисел из матрицы iK записи этих чисел в матрицу по заданным номерам i и j и блока (бл ков) памяти для хранения исходной и сформированных матриц. Отличие состоит лишь в том, что в блоке 5 достаточно одного блока памяти для матрицы В, так как транспонировани матрицы сводится к тому, что блок пересылки меняет местами симметрич относительно главной диагонали эле , менты матрицы В, т.е. . Ь.- , В блоке 10 требуется два блока паМИТИ, в одном из которых хранится исходная, матрица Ф , преобразованная в результате работы блока пересылки в нижнюю треугольную матрицу, а в другом - сформированная с помощью блока пересылки верхняя треугольная матрица А. , По команде К2 блока 8 из блока 11 вектор г через элемент ИЛИ б пересылается в блок 7, где перемножается с хранимым там значением В . При этом вычисляется вектор С. На следующем этапе работы устройства по управляющему сигналу КЗ блока 8 матрица D через блок 12 и элемент ИЛИ б подается в блок 7, где значение D перемножается со значением С - результатом предыдущей операции. Результатом перемножения является вектор д, который по команде К4 блока 8 через элемент И 9 засылается в блок11, В блок 7 по команде К5 блока .8 через элемент ИЛИ б засылается матрица А, где она перемножается с матрицей D. Полученная .в результате перемножения матрицы Н по команде Кб блока 8 через элемент И 9 пересылается в блок 11, На этом подготовидельные операции по вычислению неизвестной функции Ч методом Зейделя заканчиваются. По команде К7 блока 8 с блока 11 через элементИЛИ 6 в блок 7 засылается значение Н, а по команде КЗ через элемент ИЛИ б в блок 7 - приближенное Ч°значение искомой функции , Если информация о приближенном значении отсутствует, то в качестве первого приближения в блоке 7 записывается значение , В блоке 7 матрица Ни вектор ° перемножаются и произведение по команде К9 через элемент И 18 направляется в сумматор 13, куда по команде КЗ блока 3 из блока 11 поступает вектор д, С выхода сумматора 13 искомое значение первого шага итерации (в дальнейшем п+1 шага) подается на сумматор 14, где определяется разность Д. - и на блок 11, где оно записывается вместо , С сумматора 14 значение Ли поступает в блок 15, где значение й-и сопоставляется с заданной ошибкой вычислений л , В дальнейшем в этом блоке ошибка (п+1)-го шага итерации сравнивается с Л , Если в результате сравнения оказывается, что h--, - Л , то итерационный процесс определения функции Ч по команде блока 15 в блок 8 прекращается и значение искомой функции сумматора 13 по этой же команде выдается в регистр 16, а блок 8 приводится в исходное состояние, в противном случае итерационный процесс вычислений функции требуемой точностью

продолжается, что достигается повторной подачей команд К7-К9 с блока 8

Применение предлагаемого устрой- ства позволяетзначительно повысить точность определения требований и параметров технических устройств.

ФОЕЯлула изобретения

Устройство для определения требований к параметрам технических устройств, ссдержаадее последова- тельно соединенные коррелятор,анализатор случайного процесса, вычис лительный блок, блок возведения в степень и блок транспортирования матриц, блок управления, первый сумматор, блок памяти, блок произведения, блок обращения матриц и регистратор, отличающееся тем, что/ с целью повышения точности устройства, в него введены три элемента И, два элемента ИЛИ, блок формирования матриц, второй сумматор и блок сравнения, четыре входа блсжа памяти соединены соответственно с соответствующими вьаходами блока управления, пятый вход - с входом устройства, шестой вход с первым выходом второго сумматора, седьмой вход через первый элемент И - с выходом блока произведения, три выхода через первый элемент ИЛИ с первым входом блока произведения, а четвертый выход - с первым входом второго сумматора, второй вход .которого через второй элемент И соединен с выходом блока произведения, соединенньм через третий элемент И с первым входом блока формирования матриц, первый внход которого соединен с первым входом второго элемента ИЛИ, а второй выход - через блок обращения матриц с четвертым входом первого элемента ИЛИ, третий вход второго сумматора соединен с выходом блока сравнения, выходы блока управления соединены с вторыми входами первого, второго и третьего элементов И и со вторым и третьим входами блока формирования матриц, а вход - с выходом блока сравнения, вход которого соединен через первый сумматор с первым входом второго сумматора, второй выход которого соединен с регистратором, вход блока транспонирования матриц соединен с Пятый входом первого элемента ИЛИ, а выход - со вторым входом второго элемента ИЛИ, подключенного выходом ко второму входу блока произведения.

Источники информации, принятые во внимание при экспертизе

кл. G 01 R 31/02, 1977.

Авторы

Даты

1981-01-23—Публикация

1979-02-06—Подача