(54) КОМПЕНСАЦИОННЫЙ ИЗМЕРИТЕЛЬ РАЗНОСТИ ФАЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель разности фаз | 1977 |

|

SU711492A1 |

| СВЧ-амплифазометр | 1986 |

|

SU1350627A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Цифровой измеритель емкости и индуктивности | 1973 |

|

SU659993A1 |

| Фазометр | 1979 |

|

SU918880A1 |

| Фазоизмерительное устройство | 1984 |

|

SU1223162A1 |

| Устройство для раздельного приема цифровых радиосигналов с перекрывающимися спектрами | 1982 |

|

SU1081807A1 |

| Скважинный инклинометр | 1967 |

|

SU462019A1 |

| ИЗМЕРИТЕЛЬ СКОРОСТИ | 2011 |

|

RU2492505C1 |

| УСТРОЙСТВО ДЛЯ ПРИВЯЗКИ ШКАЛ ВРЕМЕНИ | 1992 |

|

RU2046393C1 |

Изобретение относится к измерительной технике и может применяться в информационно-измерительных системах, используемых в промьшшенности и научных исследованиях.

известны измерители разности фаз когерентных сигналов, принцип действия которых основан на уравновешивании измеряемого фазового сдвига фазовым сдвигом, создаваемым калиброванным фазовращателем. Отсчет результата производится по шкале фазовращателя Гц .

Однако такие недостатки механических фазовращателей, как узкий частотный диапазон, наличие люфтов и трения, зависимость фазового сдвига от геометрических размеров фазовращателя , погрешности градуировки и считывания, не позволяют обеспечить приемлемый уровень метрологического качества измерений.

Известен автокомпенсационный фазометр с цифровым отсчетом, который состоит из набора фазовргидателей с ключами, фазового детектора, фильтра нижних частот, блока управления ключами, цифрового индикатора, блока определения знака 2.

2

измеряемый фазовый сдвиг поразрядно компенсируется посредством включения набора фазовращателей, номинальные значения вносимого фазового сдвига которых соответствует ряду 180, 90, 45. . .180°/2 Результат измерения визуализируется цифровым индикатором в соответствии с номинальными значениями фазовращателей.

10 Точность измерения определяется точностью калибровки фазовращателей, стабильностью их номинальных значений, паразитным фазовым сдвигом, вносимым ключами и стабильностью этого

15 сдвига. Принципиальные ограничения на точность измерения фазового сдвига накладываются ключами. Число ключей изменяется в диапазоне значений измеряемой величины. Скомпенсировать

2 носимую ключами нестабильную погрешность практически невозможно. Кроме fforo, реализация стабильных фазовращателей 180/2.при п 7 представляет значительные технические трудносjiSти даже при фиксированного значения часто1 ы измерительного сигнала. Частотнее погрешность фазовращателей, соизмеримая с номинальньпу значением . младших разрядов, усу губляет труд30ности высокоточного измерения разности фаз в широком диапазоне частот рассматриваемым фазометром.

Цель изобретения - повышение точности измерений в широком диапазоне частот.

Поставленная цель достигается тем что в компенсационный измеритель разности фаз, содержащий опорный и измерительный каналы, два триггера, триггерный фазовый детектор с фильтром нижних частот, цифровой индикатор, блок определения знака, введены в опорный и измерительный каналы формирователя, соединенные со входными клеммами, двухвходовые коммутаторы, третий триггер, второй фильтр нижних частот, блок вычитания с интегратором на выходе, широтно-импульсный модулятор и цифровой измеритель временных интервалов, причем выходы формирователей соединены со счетными входами триггеров соответственно и с входами блока определения знака, выход которого соединен с входом цифрового индикатора и с управляющим входом коммутатора, введенного в опорный канал, входы коммутаторов соединены с прямым и инверсным выходами триггеров соответственно, а вых ды - со входами триггерного фазового детектора, инверсный выход которого соединен со входом третьего триггера, выходом соединенным через второй фильтр нижних частот с одним из входов блока вычитания, ко второму вход которого подсоединен выход первого фильтра нижних частот, а выход блока вычитания через последовательно соединенные интегратор и широтно-импуль ный модулятор соединен с входом цифрового измерителя временных интервалов и управляющим входом коммутатора, введенного в измерительный канал, -выходы цифрового измерителя временных интервалов соединены со входами цифрового индикатора соответственно.

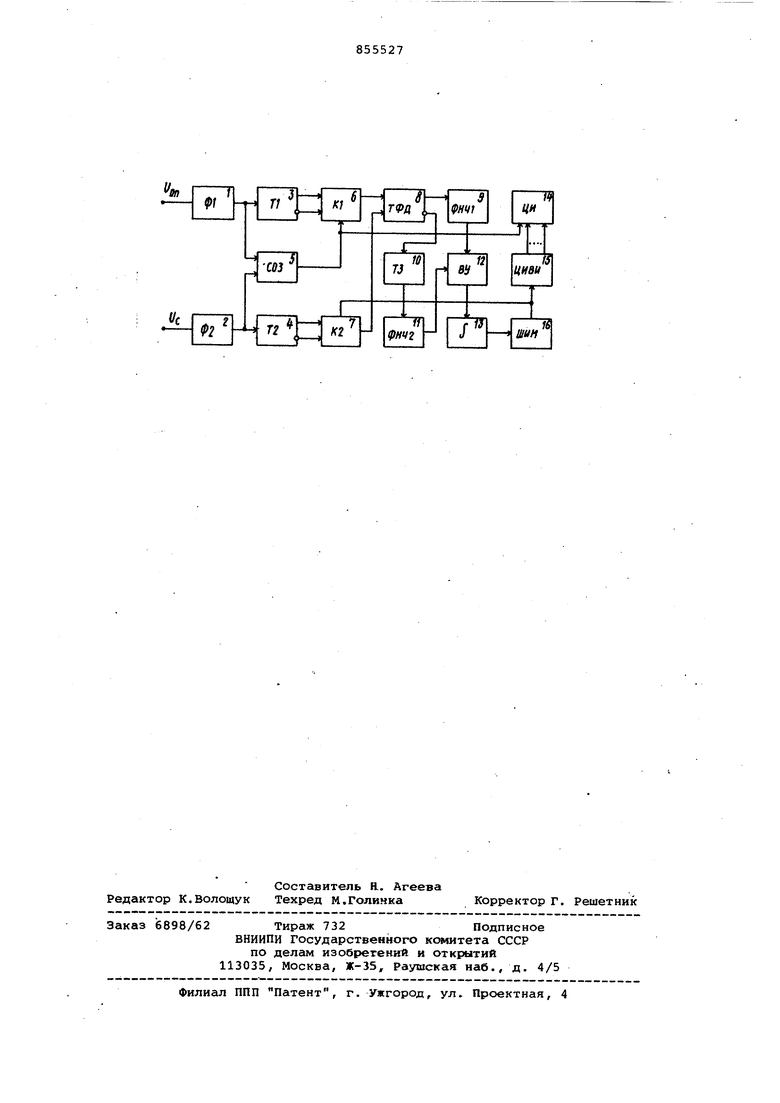

На чертеже представлена блок-схема измерителя разности фаз,

Компенсационный измеритель разности фаз состоит из формирователя 1,2, триггеров 3, 4, блока 5 определения знака, двухвходовых коммутаторов 6, 7, триггерного фазового детектора 8, с фильтром 9 нижних частот, третьего триггера 10, второго фильтра 11 нижних частот, блока 12 вычитания, интегратора 13, цифрового индикатора 1 цифрового измерителя 15 временных интерв лов, широтно-импульсного модулятора 16, Входные клеммы опорного и измерительного каналов соединены с формирователями 1 и 2, Выходы формирователей 1 и 2 соединены со входами триггеров 3, 4 и входами блока 5 определения знака. Прямой и инверсный выходы триггеров 3, 4 соединены со входами соответствующих коммутаторов б, 7. Выход блока 5 определения знака соединен с управляющим входом коммутатора б в опорном канале и входом цифрового индикатора 14, Выходы коммутаторов б, 7 опорного и измерительного каналов соединены со входами триггерного фазового детектора 8, прмой выход которого через фильтр 9 нижних частот соединен с одним входом блока 12 вычитания, а инверсный выход через триггер 10 и фильтр 11 нижних частот с другим входом блока вычитания 12, Выход блока 12 вычитания через интегратор 13 соединен с управляющим входом широтно-импульсного модулятора 16, выход которого соединен с управляющим входом коммутатора 7 в измерительном канале и входом цифрового измерителя 15 временных интервалов, Выходы цифрового измерителя 15 временных интервалов соединены со входами цифрового индикатора 14,

Измерительные сигналы поступают на входные клеммы опорного и измерительного каналов, являющиеся входами формирователей 1, 2. Формирователи вырабатывают прямоугольные импульсы, передние фронты которых привязаны к характерным точкам входных измерительных сигналов, например к моментам перехода через нулевую линию, Входные импульсы формирователей 1, 2 запускают передними фронтами триггеры 3, 4, работающие в режиме деления частоты. Прямой и инвертированный сигналы с выходов триггеров 3, 4 поступают на сигнальные входы коммутаторов 6, 7, В случае положительного фазового сдвига блок 5 определения знака вырабатывает потенциал, размещающий прохождение прямого сигНсша триггера 3 в опорном канале. При отрицательном фазовом сдвиге относительного опорного напряжения блок 5 определения знака вырабатывает потент циал, разрешающий прохождение через коммутатор б инвертированного сигнала триггера 3, внося таким образом фазовый сдвиг для первой гармоники прямоугольного колебания, формируемого триггером 3, В измерительный канал фазовый сдвиг О вводится аналогично посредством триггера 4 и коммутатора 7, Однако управление коммутатором 7 осуществляется выходными импульсами широтно-импульсного модулятора 16, Коммутатор 7 поочередно, с частотой широтно-импульсного модулятора 16 подключает ко входу триггерного фазового детектора 8 прямой или инверсный выходы триггера 4, осуществляя таким образом фазовую модуляцию на два значения 0-1 I сигнала измерительного канала, причем скважность модулирующей прямоугольной последовательности импульсов целенаправленно изменяется. Триггерный фазовый детектор 8 запускается передними фронтами прямоугольных импульсов коммутаторов б, 7, следующих с частотой измерительного и опорного сиг налов. Постоянная составляющая импульсн последовательности на выходе тригге ного фазового детектора 8 модулиров на по величине посредством фазовой модуляции сигнала измерительного ка ла. Фильтр нижних частот 9 выделяет результирующую постоянную составляю щую и подает ее на один из выходов блока 12 вычитания, на другой вход которого подается опорное постоянно напряжение, сформированное триггеро 10и фильтром нижних частот 11. Раз ность постоянного опорного напряжен и результирующей постоянной составляющей интегрируется интегратором 1 и управляет работой широтно-импульс ного модулятора 16. Последний при нулевом напряжении на входе вырабатывает прямоугольную последовательность импульсов со скважностью 2, при положительном управляющем напря жении скважность увеличивается, при отрицательном - уменьшается. Прямоугольное напряжение фиксированной частоты (задающая частота широтноимпульсного модулятора 16) с изменяющейся в процессе уравновешивания скважностью поступает на цифровой измеритель 15 временных интервалов. Результат измерения и знак отображаются на цифровом индикаторе 14. Триггерный фазовый детектор 8, триггер 10, два фильтра нижних частот 9 11и блок 12 вычитания, соединенные описанным способом, имеют пилообразную дискриминационную характерис тику, пересекающую нулевую линий в точке 180 фазового сдвига входных сигналов. Фазовый сдвиг от нуля до 180 преобразуется в положительное постоянное напряжение, от 180° до 360° - в отрицательное. Введение в схему измерителя разности фаз широтно-импульсного модуля тора, управляющего работой коммутатора в измерительном канале, третьего триггера, второго фильтра нижних частот, блока вычитания, интегратора и их соединения указанным образом позволяет значительно повысить точность преобразования фазового сдвига во временной интервал в пределах дву квадратов, а введение коммутатора в опорный канал и соединение его управ ляющего входа с блоком определения знака исключает однозначность измерений в четырех квадрантах. Отсутствие частотнозависимых элементов в трактах преобразования фазового сдви га во временной интервал позволяет перекрыть частотный диапазон от единиц кГц до сотен МГц (верхняя граница зависит от быстродействия триггеров в режиме деления частоты). Точ ность измерения ра-ности фаз определяется cooTHOiueHHGM между периодом выходного сигнала широтноимпульсного модулятора и разрешающей способ- i ностью цифрового измерителя временных интервалов. Использование данного устройства позволяет повысить производительность труда при многократных измерениях, исключить субъективный фактор ограничения точности.измерений, уменьшить затраты на измерительную аппаратуру при работе в широком диапазоне частот и значительно повысить точность измерений. Формула изобретения Компенсационный измеритель разности фаз, содержащий опорный и измерительный каналы, два триггера, триггерный фазовый детектор с фильтром нижних частот, цифровой-индикатор, блок определения знака, о т л и ч а: ющ и и с я тем, что, с целью повышения точности измерения в широком диапазоне частот, в него введены в опорный и измерительный каналы формирователя, соединенные со входными клеммами, двухвходовые коммутаторы, третий триггер, второй фильтр нижних частот, блок вычитания с интегратором на выходе, широтно-импульсный модулятор и цифровой измеритель временных интервалов, причем выходы формировгчтелей соединены со счетными входами триггеров соответственно и со входами блока определения знака, выход которого соединен с входом цифрового индикатора и с управляющим . входом KON TyTaTOpa, введенного в опорный канал, входы коммутаторов соединены с прямым и инверсным выходами триггеров.соответственно, а выходы со входами триггерного фазового детектора, инверсный выход которого соединен со входом третьего триггера, выходом соединенным через второй фильтр нижних частот с одним из входов блока вычитания, ко второму входу которого подсоединен выход первого фильтра нижних частот, а выход блока вычитания через последовательно соединенные интегратор и широтноимпульсный модулятор соединен с входом цифрового измерителя временных интервалов и управляющим входом коммутатора, введеннЪго в измерительный кансш, выходы цифрового измерителя врэменных интервалов соединены со входами цифрового индикатора соответственно. Источники информации, принятые во внимание при экспертизе 1.Кушнир Ф.В. и др. Измерения в технике связи, М., Связь, 1976, с. 239. 2.Авторское свидетельство СССР 278870, кл. G 01 « 25/04, 1968.

Авторы

Даты

1981-08-15—Публикация

1979-07-06—Подача