(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1977 |

|

SU711635A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU903986A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU985828A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1140178A1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Аналоговое запоминающее устройство | 1973 |

|

SU517941A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1005191A1 |

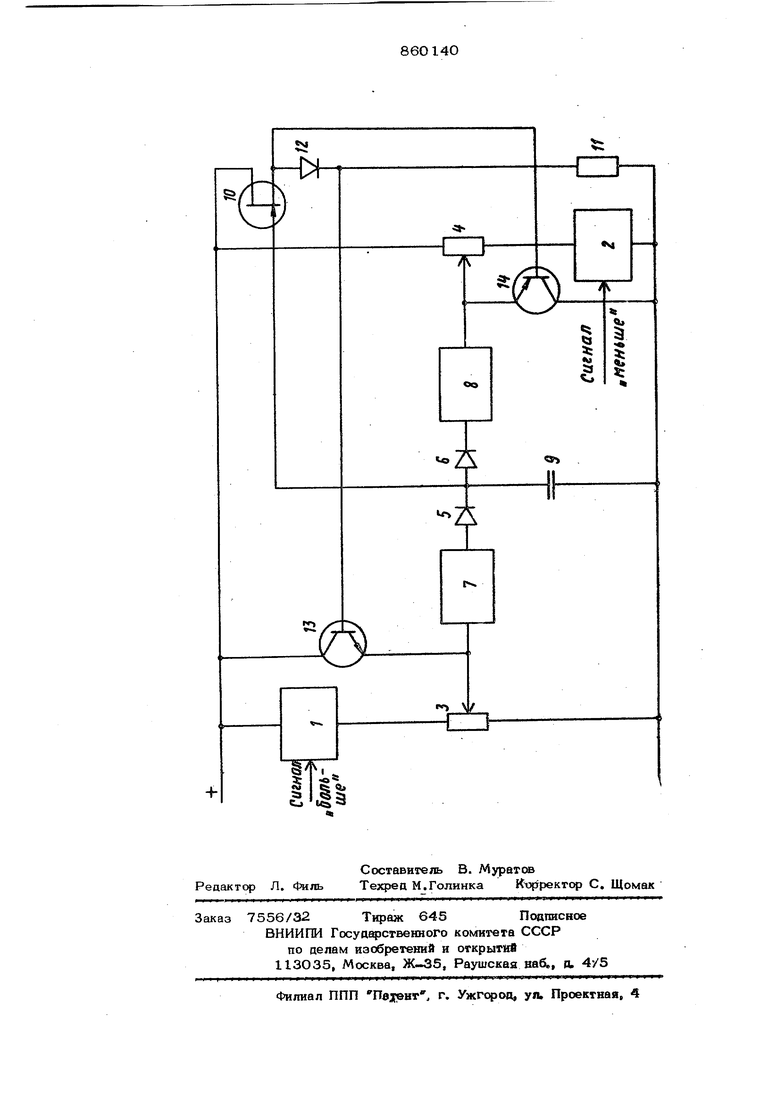

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического регулирования для интегрирования по времени дискретных сигналов, поступающих с трехпозицисжньк регуляторов, а также шште/ьного запоминания результатов интегрирования. По основному авт. св. № 711635 известно аналоговое запоминающее устрой ство, используемое в системах автоматического регулирсжания для интегрирования по времени дискретных сигналов, поступающих с трех позиционных регупятфов, и длительного запоминания результат интегрирования. Это устройство выполнено ,на повторителе напряжения с. большим обратным сопротив;ЕНием управляющего перехода и накопительном элементе, например, высокостабильном коноенсаторе, одна обкладка которого соединена с шиной нулевого потенциала, а между шинами питания введены ключи, пассивные элементы соединенные с шинами питания по мосте вой схеме, в диагонахь которого включены последовательно соединенные заржшый блок, нелинейные элементы и разряшый блок, вход которого соединен с выходом первсго пассивного элемента, другая обкладка конденсатора соединена с выходом первого негашейного элемента , входом второго нелинейного элемента и входом повторителя напряжения, а вход второго зарядного блока подключен к управляющему выходу второго пассивного элемента С Однако для обеспечения длительного запоминания результатов Ш1тегр1фования нелинейные элементы в устройстве оолясны быть с самыми миннмат ными обратными токами, так как они в режиме запоминания находятся под обратным напряжением, причем это напряжение постоянно меняется в зависимости от величины напряжения на обкшдках накопительного элемента, а эна чит и меняются обратные токи через непп нейнью элементы. Эти токи влияют на вепкчяту потенциала на обкладках накопител ного элемента, т.е. авя влияют на длитель386нос-ть (ппомя) крЕкеп.ня информации, и чем болз-.ше будут зти токи, тем больше будет скорость изменения потенциала на обклаоках накопительного элемента, значит меньше будет время хранения информации, Иел1з изобретения - увеличение времени хранения информации. Постйвленная цель достигается тем, что Б аналоговое запоминающее устройство введены шза эмиттерных повторителя, причем вход первого эмиттерного повторителя подключен к вьпсоду повторителя напряжения, а выход подключен к зарядному блоку, вход второго эмиттерного повторителя -подключен к нагрузочному элементу, а выход пооключен к разрядному блоку, и нелинейный элемент, вход которого подключен к выходу повторителя напряншния, а выход - ко входу второго эмиттерного повторителя. На чертеже представлена принципиальная, схема аналогового запоминающего устройства. Аналоговое запоминающее устройство содержит ключи 1 и 2, пассивные элементы 3 и 4, нелинейные элементы 5 и 6, разрядный блок 7, зарядный блок 8, накопительный элемент 9, повторитель 1О напряжения, нагрузочный элемент 11, нелинейный эпемент 12, эмиттерные повторители 13 и 14. Нелинейный элемент 12 введен для того, чтобы снизить начальное напряжение на выходе устройства и сделать его равным или несколько меньше напряжения на обкладках накопительного элемента. Эмит- терные повторители 13 и 14 выполнены на транзисторах разной проводимости вмес то с подключенными к ним пассивными эгегментами 3 и 4, причем эмиттерный повторитель 14 на транзисторе обратной проводимости повторяет выходное напряже ние на нагрузке, которое на незначительну величину меньше напряжегшя на обкладках накопительного элемента, а эмиттерный повторитель 13 на транзисторе прямой 0 проводимости повторяет напряжение стокисток повторителя 1О напряжения. За счет этого вьфавниваются потенциалы входа и выхода нелинейных элементов 5 и 6, т.е. практически уменьшаются в несколько раз обратные напряжения на этих элементах в режиме запоминания, а поэтому уменьшаются обратные токи через эти элементы. Это позволяет увеличить время храения информации в два раза по сравнению с звестным устройством. Погрешность запоинания предлагаемого устройства составяет 0,23 В/ч во всем диапазоне изменеия выходаого напряжения. Использование изобретения позволяет увеличить время хранения информации, а также применять в качестве нелинейньрс элементов вместо дорогостоящих полевых транзисторов, включенных по диооной схеме, более дешевые точечные кремниевые диоды. ла изобретения Аналоговое запоминающее устройство по авт. св. . 711635, отличающееся тем, что, с целью увеличения времени хранения информации, в устройст во введены два эмиттерных повторителя, причем вход первого эмиттерного пситорителя подключен к вькоду повторителя напряжения, а выход подключен к зарядному блоку, вход втфого эмиттерного повторителя подключен к нагрузочному элементу, а выход подключен к разрядному блоку, и нелинейный элемент, вход которого подключен к выходу повторителя напряжения, а выход - ко входу второго эмиттерного повторителя. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 711635, кл. G 11 С 27/ОО.

Авторы

Даты

1981-08-30—Публикация

1978-12-20—Подача