(54) АНАЛОГОВОЕ ЗАПОМИНАКЯЦЕЕ УСТРОЙСТВО Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности, в запоминающих устройствах для компенсации дрейфа нуля электрометричес ких усилителей. Известно аналоговое запоминаизщее устройство (АЗУ) , содержащее зарядны элемент, вход которого соединен со входом устройства, а выход подклю сен к накопительному элементу, например конденсатору, и через коммутатор, за рядочувствительный усилитель - к генератору компенсационного тока, а последний к накопительному элементу. Зарядный элемент, генератор компенсирующего тока и коммутатор управляются с соответствующих выходов генератора тактовых импульсов fl. Однако в известном устройстве время хранения при заданной точности определяется правильностью выбора и стабильностью коэффициента передачи зарядочувствительного элемента и ген ратора компенсирующего тока, которые очень трудно сделать стабильными. Кроме того, данное АЗУ предназначено в основном, для запоминания импульсных напряжений, поскольку в режиме хранения входной сигнал должен отсутствовать .I Наиболее близким к предлагаемому по технической сущности является аналоговое эапомннающее устройство, содержащее два компаратора, первый вход первого и второй вход второго компаратора объединены и подключены ко входу АЗУ, второй вход первого и первый вход второго компараторов также объединены и подключены к выходу входного повторителя напряжения, а вход последнего - к накопительному элементу и выходам генераторов тока и дополнительного генератора тока, выходу разрядного блока и входу выходного повторителя напряжения. Выход последнего является выходом АЗУ. Выход первого компаратора подключен ко входу генератора тока и управляющему входу второго компаратора. Выход второго компаратора подключен ко входу дополнительного генератора тока и первому входу блока управления, а выход последнего к управляющему входу первого компаратора. Второй вход блока управления соединен с шиной управления 2 . Однако такое АЗУ имеет сравнительно невысокую точность и малое

время хранения, время выборки в нем сравнительно вЬлико и, кроме того, оно может запоминать сигналы только одной полярности, а также при наличи на накопительном элементе напряжения меньшего по абсолютной величине, чем входной сигнал.

Цель изобретения - повышение точности и быстродействия устройства, увеличения времени хранения информации устройства и расишрение области его применения за счет запоминания сигналов обеих полярностей.

поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее накопительный элемент/ например конденсатор, одна из обкладок которого соединена с первым входом зарядно-разрядного блока, выход зарядно-разрядного блока подключен к ишне нулевого потенциала, первый повторитель напряжения, выход которого соединен с выходом устройства и с первыми входами первого и второго компаратора, вторые входы которых подключены ко входу устройства, шину управления, введены второй повторитель напряжения, генератор тактовых импульсов, форми-рователь импульсов, элементы И, детектор и дифференциальный усилитель, выход которого соединен с другой обкладкой, конденсатора, выход генератора тактовых импульсов соединен со входом формирователя импульсов, выход которого подключен к первым входам элементов И, вторые входы которых соединены с выходом первого компаратора, выход второго компаратора соединен с третьим входами элементов И, четвертые входы которых подключены к шине управления, выходы первого и второго элементов И соединены соответственно со входги и дифференциального усилителя, выход трет его элемента И соединен со вторым входом зарядно-разрядного блока и с первым входом детектора, второй вход которого соединен с шиной потенциала, третий вход детектора подключен к выходу второго повторителя напряжения, выход детектора соединен со входом первого повторителя напряжения, выход второго повторителя напряжения соединен с третьим входом зарядно-разрядного блока, а также тем, что зарядно-разрядный блок выполнен на первом, втором и третьем МОП-транзисторахJсток первого из коч;орых соединен с первым входом блока, сток второго МОП-транзистора с выходом блока, сток третьего МОПтранзистора подключен к третьему входу блока, затворы МОП-транзисторо соединены со вторым входом блока, а истоки МОП-транзисторов соединены между собой.

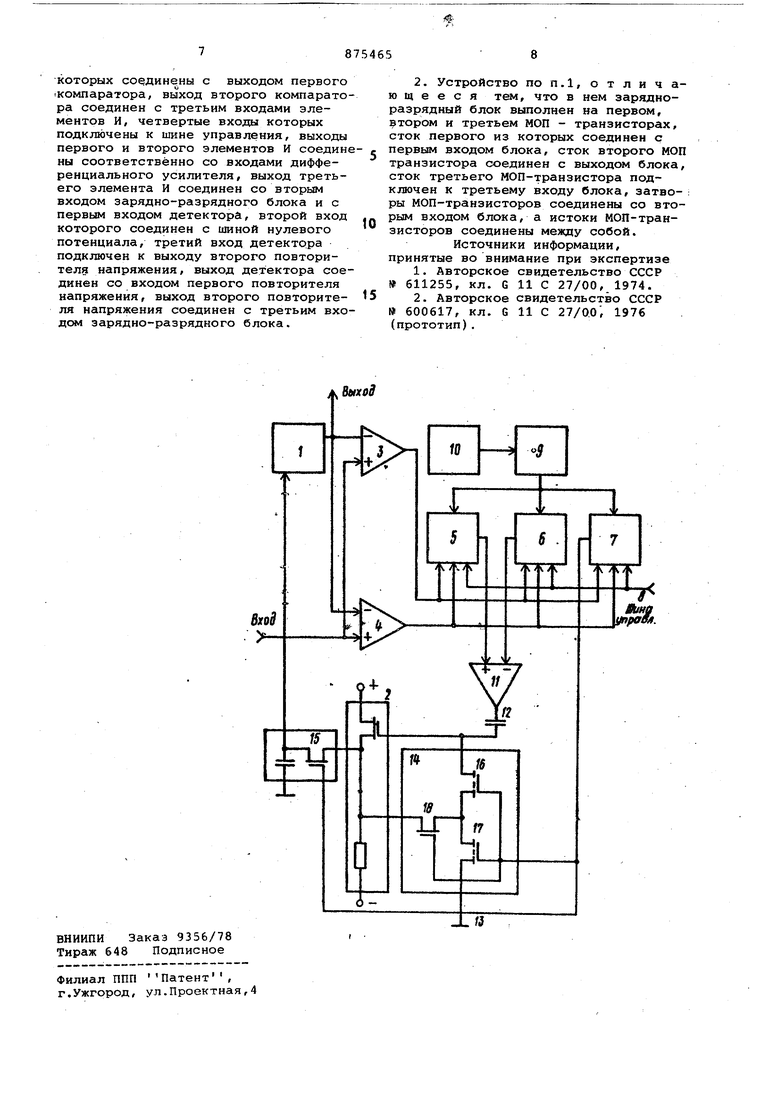

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит повторители 1 и 2 напряжения, компараторы 3 и 4. элементы И 5-7, шину 8 управления, формирователь 9 импульсов, генератор 10 тактовых импульсов, дифференциальный усилитель 11, накопительный элемент, например конденсатор 12, шину 13 нулевого потенциала, зарядно-разрядный блок 14, детектор 15, транзисторы 16-18 зарядно-разрядного блока 14.

Устройство работает следующим образом.

АЗУ имеет два режима работы - реим хранение и режим выборки и работает следующим образом.

Режим выборки.

В этом режиме по шине 8 управления на элементы 5-7 поступает сигнал разрешения, т.е. по четвертым входам всё эти элементы открыты.

Пороги срабатывания компараторов 3 и 4 сигналами смещения выбираются вблизи нуля и алгебраическая разность между ними определяет абсолютную точность запоминания входного сигнала Ug.

Пусть компаратор 3 срабатывает при уменьшении U ниже U , а компаатор 4 - ниже U (j( U U,j) .

До включения питающих напряжений накопительный элемент 12 разряден и поэтому при их включении напряжение на входе повторителя 2 и его выходе, а также на выходе повторителя 1 и, соответственно, на его выходе, равно нулю.

Допустим, что,на вход устройства поступает сигнал .

Компараторы 3 и 4 не срабатывает и своими выходными напряжениями открывают элементы И 5 и 7 и закрывают элемент И 6. Продифференцированные на формирователе 9 импульсы генератора 10 проходят через элементы И 5 и

6.С выхода элемента И 5 они поступают на первый вход дифференциального усилителя 11. На выходе последнего повторяются положительные импульсы,

а на выходе элемента И 7 синфазные им импульсы, открывающие на момент ействия импульсов МОП-транзисторы 16 и 17, и закрывающие МОП-транзистор 18. Накопительный элемент 12, подключенный к выходу усилителя 11, начинает заряжаться. Напряжение на входе и, соответственно, на выходе повторителя 2 увеличивается. Детектор 15, управгляемый по второму входу с выхода элемента 7, отфильтровывает импульсное напряжение и амплитудное значение сигнала с его выхода через повторитель 1 поступает на выход устройства (напряжение ) первые входы компараторов 3 и 4. При достижении значения выходного напряжения компаратор 3 срабатывает и закрывает элементы И 5 и

7.Заряд накопительного элемента 12

прекращается, МОП - транзисторы 16 и 17 закрываются, а МОП - транзистор 48 - открывается. На выходе устройства устанавливается напряжение Ug i allgy с точностью до порога срабатывания компаратора 3.

Если в начальный момент работы АЗУ Ujy Кя/ компараторы 3 Я 4-Cp lбатывают и их выходные напряжении закрывают элемент И 5( открываютэЯ(Вменты И 6 и 7. Теперь продиффе{ енцированные на формирователи 9 импульсы с генератора 10 через элемент И 6 поступают на второй вход дифференциального усилителя 11, а через элемент 7 синфазно с ними открывают МОП транзисторы 16 и 17 и закрывают МОП- транзистор 18. На выходе усилителя 1 появляются отрицательные импульсы и начинают заряжать накопительный Элемент 12 отрицательным напряжением.; Через повторитель 2, детектор 15 и повторитель 1 это н тряжение, как и в первом случае, появляется на выходе устройства и первых входах, компараторов 3 и 4. По достижении Uj,,, Ugx+и/ компаратор 4 возвратается в исходное состояние, а компаратор 3 остается в сработанном состоянии. Элементы И 5-7 закрываются, заряд накопительного элемента 12 прекращается. На выходе .устройства остается напряжение, равное входному W точностью до порога сраг батывания. компаратора 4.

Работа АЗУ протекает аналогично ,и при начальном заряде накопитёль ног элемента 12, т.е. при наличии выходного сигнала напряжение d и в dtO случае устанавливается равнЕЛм U gx 7 точностью до величины порога срабатывания одного из компараторов 3 или

4. „ Режим хранения..

В этом режиме по шине 8 на элементы И 5-7 поступает сигнал запрета, т.е. по четвертым входам э;ти элементы закрыты.

Поэтому независимо от U и состо яния компараторов 3 и 4 выходной сигнал выходе устройства будет равен его значению, имеющемуся в момент предшествующий подаче команды запрета по шине 8, т.е. АЗУ запоминает сигнал Ugyc: U вых и переходит в режим хранение. Время хранения чром АЗУ будет определяться постоянной времени цепи разряда f рдо, накопительного элемента 12

..«,

где С величина емкости накопительного элемента; R - сопротивление цепи разряда

емкости С.

R определяется параллельным соединением входного сопротивления повторителя 2 (более Ом) и сопротивлением зарядно-разрядного блока 14 RP между первым входом и выходом его

Поскольку в режиме хранение элемент 7.закрыт, то МОП-транзисторы зарядно-разрядного блока 14, подключенные затворами к его выходу, 16 и 17 закрыты, а МОП-транзистор 18 открыт. При отсутствии МОП-транзистора 18 последовательнре сопротивление МОП-транзисторов 16 и 17 в закрытом состоянии составляет около

р

Ом (при нормальной температуре

10

и .постояннаяtpor9 CR 0,33-10V0 3,3-10 с, (,33 мкФ,R опрёде-;

|Пяется величиной Нр-Ю Ом), что недостаточно велико.

Для существенного увеличенияГрд выход повторителя 2 через открытое сопротивление МОП-транзистора 18 (около 1 кОм) подключен к точке соединения истоков МОП-транзисторов 16 и 17. Если коэффициент передачи И повторителя 2 К 2Г 1, в цепи разряда конденсатора 12 образуется глубокая отрицательная обратная связь (как бы противоэдс) препятствующая разряду конденсатора 12 и fрд существенно увеличивается.

Предлагаемое. АЗУ может запоминать и хранить напряжения до ...+ +1Q В (определяется выбранной элеме тной базой). При этом время выборки составляет 0,05 ... 0,2 с (зависит от Ugj( и выбранной частоты генератора 10) . Время хранения txpon при заданной относительной точности зависит от величины U и окружающей температуры и может достичь 1 ч

Формула изобретения

1. Аналоговое запоминающее устройство, содержащее накопительный элемент, например, конденсатор, одна из обкладок которого соединена с первым входом эарядио-разрядного блОка, выход зарядно-разрядного блока подключен к шине нулевого потенциала, первый повторитель напряжения, выход которого соединен с выходом устройства и с первыми входами первого и второго компаратора, вторые входы которых подключены ко входу устройства, ишну управления, отличающееся тетл, что, с целью повышет ния точности и быстродействия устройства, увеличения вращения хранения информации и расширения области его применения за счет запоминания сигналов обеих полярностей, в него введены второй повторитель напряжения, генератор тактовых импульсов, формирователь импульсов, элементы И, детектор и дифференциальный усили.тель, выход которого соединен с другой обклгшкОй конденсатора, выход генератора тактовых импульсов соединен со входом формирователя импульсов, выход которого подключен к первым входам элементов И, вторяле входы

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841057A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Пьезополупроводниковый стабилизатор постоянного напряжения | 1980 |

|

SU926636A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| УСТРОЙСТВО ДЛЯ ПИТАНИЯ ИМПУЛЬСНЫХ НАГРУЗОК | 2009 |

|

RU2400013C1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU985828A1 |

| Преобразователь частоты | 1982 |

|

SU1150711A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU963106A1 |

Авторы

Даты

1981-10-23—Публикация

1980-02-11—Подача