1

Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах цифровой обработки сигналов.

Известен цифровой фильтр, использующий принцип накопления вьщеления полезного сигнала и содержащий умножители многоразрядных чисел D3

Однако операция умножения является одной из наиболее длительных по времени и снижает быстродействие устройства, так как многоразрядные умножители весьма громоздки и в определенной степени определяют габариты и параметры цифрового фильтра в целом.

Наиболее близким к предлагаемому устройству по назначению, технической сущности и реализации является цифровой фильтр, состоящий из последовательно соединенных входного запоминающего устройства ЗУ , вычитающеУо устройства, умножителя, сумматора и выходного ЗУ, выход котороГО соединен со вторыми входами вычитающего устройства и сумматора. В качестве умножителя используется регистр сдвига, который эквивалентен умножению на 2 , где к - число сдвигов. При этом достигается сокращение габаритов, потребляемой мощности и времени выполнения операции L2/.

Недостаток устройства - невозможность точной реализации требуемой

10 постоянной времени фильтра и соответственно ухудшение помехоустойчивости, так как с помощью регистра сдвига требуемый код множителя можно реализовать только приближенно.

15

Цель изобретения - увеличение точ-, ности и повышения помехоустойчивости цифрового фильтра путем введения в него счетчика, дешифратора, мультиплексора и дополнительного сумматора.

20

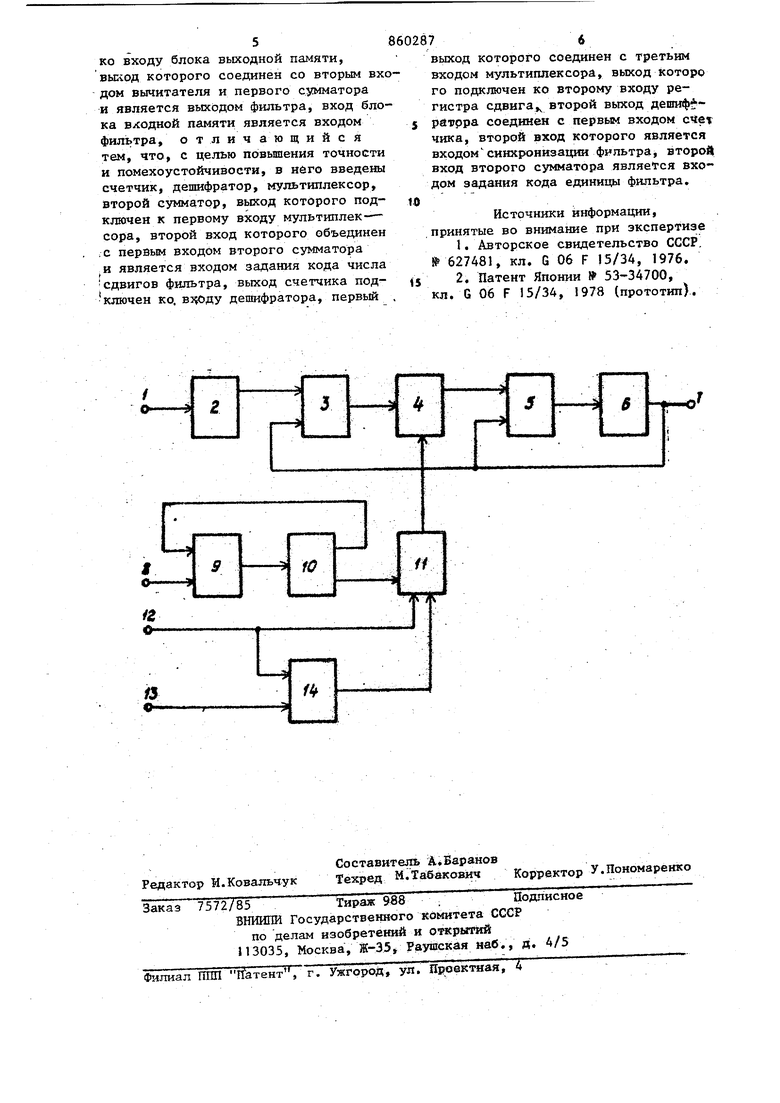

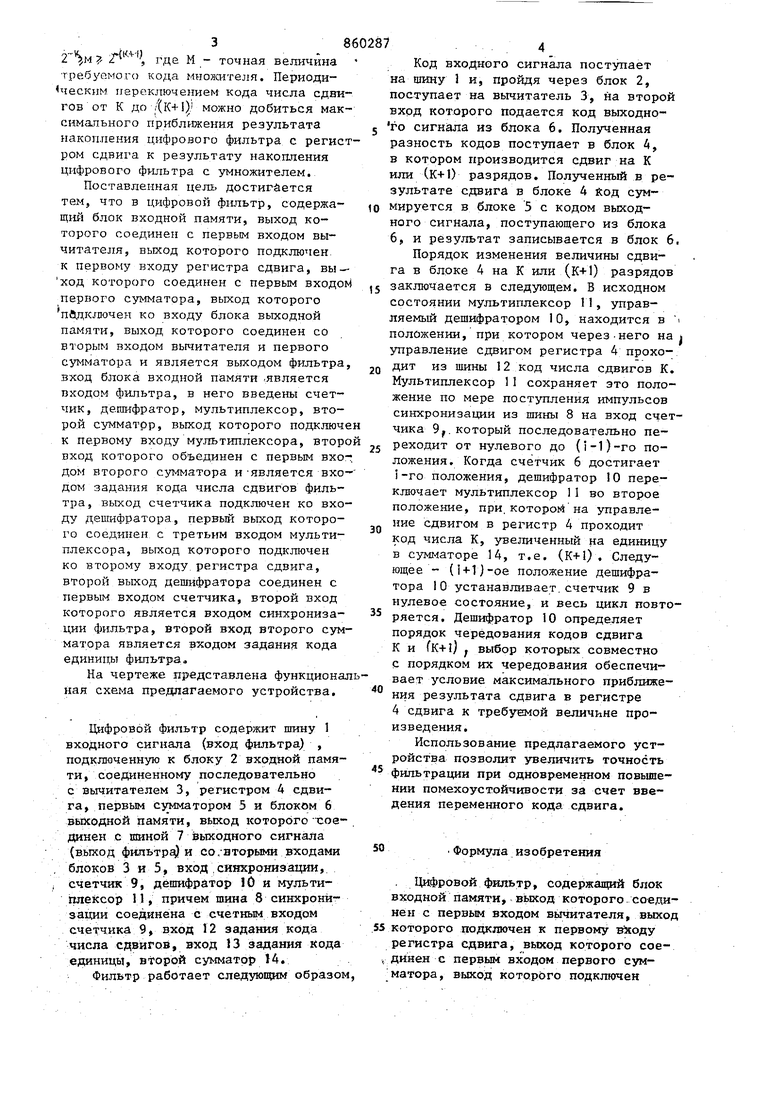

Сущность изобретения заключается в том, что в продессе работы осуществляется периодическое изменение кода 1числа сдвигов от К до К+1, причем 2 , где М - точная величина требуемого кода мнолсителя. Периоди ческим переключением кода числа сдви гов от К до /(K+i)J можно добиться мак симального приближения результата накопления цифрового фильтра с регис ром сдвига к результату накопления цифрового фильтра с умножителем.. Поставленная цель достигается тем, что в цифровой фильтр, содержащий блок входной памяти, выход которого соединен с нервьм входом вычитателя, выход которого подключен. к первому входу регистра сдвига, вы - ход которого соединен с нервым входо первого сумматора, выход которого пад,ключен ко входу блока выходной памяти, выход, которого соединен со вторым входом вычитателя и первого сумматора и является выходом фильтра вход блока входной памяти .является входом фильтра, в него введены счетчик, дешифратор, мультиплексор, второй сумматрр, выход которого подключ к первому входу мультиплексора, втор вход которого объединен с первым вхо дом второго сумматора иявляется вхо дом задания кода числа сдвигов фильтра, выход счетчика подключен ко вхо ду дешифратора, первьй выход которого соединен с третьим входом мультиплексора, выход которого подключен ко второму входу.регистра сдвига, второй выход дешифратора соединен с первым входом счетчика, второй вход которого является входом синхронизации фильтра. Второй вход второго сум матора является входом задания кода единицы фильтра. На чертеже представлена функциона ная схема предлагаемого устройства. Цифровой фильтр содержит шину 1 входного сигнала (вход фильтра) , подключенную к блоку 2 входной памя ти, соединенному последовательно с вычитателем 3, регистром 4 сдвига, первым сумматором 5 и блоком 6 выходной памяти, выход которого-сое динен с шиной 7 1зыходного сигнала (выход фильтра) и со,-аторыми входами блоков 3 и 5, вход;сянхрониз ации,, счетчик 9, дешифратор 10 и мультиплексор 11, причем шина 8 синхронизации соединена с счетным входом счетчика 9, вход 12 задания кода числа СДВИГОВ, вход 13 задания кода единицы, сумматрр 14. Фильтр работает следующим образо Код входного сигнала поступает а шину 1 и, пройдя через блок 2, оступает на вычитатель 3, на второй ход которого подается код выходноо сигнала из блока 6. Полученная азность кодов поступает в блок 4, котором производится сдвиг на К ли (К+1) разрядов. Полученный в реультате сдвига в блоке 4 код сумируется в блоке 5 с кодом выходого сигнала, поступающего из блока , и результат записывается в блок 6, Порядок изменения величины сдвиа в блоке 4 на К или (К+1) разрядов заключается в следующем. В исходном остоянии мультиплексор 11, управяемый дешифратором 10, находится в оложении, при котором через-него на i правление сдвигом регистра 4 проходит из шины 12 код числа сдвигов К, Мультиплексор 11 сохраняет это положение по мере поступления импульсов синхронизации из шины 8 на вход счетчика 9,. который последовательно переходит от нулевого до (1-1)-го положения. Когда счетчик 6 достигает i-го положения, дешифратор 10 переключает мультиплексор 1I но второе положение, при. которой на управление сдвигом в регистр 4 проходит код числа К, увеличенный на единицу в сумматоре 14, т.е. (К+1) , Следующее - (i+lj-oe положение дешифратора 10 устанавливает.счетчик 9 в нулевое состояние, и весь цикл повторяется. Дешифратор 10 определяет порядок чередования кодов сдвига К и (K+I) J выбор которых совместно с порядком их чередования обеспечивает условие максимального приближения результата сдвига в регистре 4 сдвига к требуемой величине произведения. Использование предлагаемого устройства позволит увеличить точность фильтрации при одновременном повьшении помехоустойчивости за счет введения переменного кода сдвига. Формула изобретения . Цифровой фильтр, содержащий блок входной памяти, вькод которого.соединен с первым входом вычитателя, выход которого подключен к первому выходу регистра сдвига, вькод которого соедйнен с первым входом первого сумматора, выход которого подключен

ко входу блока выходной памяти, вьEioд которого соединен со вторым вх дом вычитателя и первого сумматора и является выходом фильтра, вход блока входной памяти является входом фильтра, отличающийся тем, что, с целью повьшения точности и помехоустойчивости, в него введены счетчик, дешифратор, мультиплексор, 1второй сумматор, выход которого подключен к первому входу мультиплексора, второй вход которого объединен С первым входом второго сумматора и является входом задания кода числа сдвигов фильтра, выход счетчика подключен ко. дешифратора, первый

выход которого соединен с третьим входом мультиплексора, выход которо го подключен ко второму входу регистра сдвига, второй выход дешиф рдфрра соединен с первым входом счет чика, второй вход которого является входомсинхронизацш фильтра, в торой вход второго сумматора является входом задания кода единицы фильтра.

)

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР. № 627481, кл. G 06 F 15/34, 1976.

2.Патент Японии 53-34700,

s кл. G 06 F 15/34, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Цифровой формирователь спектра | 1984 |

|

SU1171804A1 |

| Цифровой фильтр | 1980 |

|

SU919054A1 |

| Цифровой фильтр | 1980 |

|

SU904201A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

Авторы

Даты

1981-08-30—Публикация

1979-11-29—Подача