выход синхронизатора подключены соответственно к адресному и управляющему входам второго блока памяти, информационный вьгход адресного счетчика (кроме старшего разряда) поразрядно подключен к адресному входу блока памяти коэффициентов, восьмой выход синхронизатора подключен к входу генератора спорного напряжения и входу синхронизации регистра, информационный выход первого счетчика и девятый выход синхронизатора соответственно подключены к адресному и управляющему входам первого блока памяти, девятьй, десятьй и одиннадцатый выходы синхронизатора и выход

узла сравнения блока управления соответственно подключены к группе входов кода управления регистра сдвига, в5сод запуска синхронизатора блока управления является входом запуска формирователя, информационньй вькод второго блока памяти подключен к ВХОДУ дешифратора, выход которого подключен к управляклцему входу сумматора-вычитателя, информационный выход регистра подключен к второму входу узла сравнения блока управления, второй информационный вход мультиплексора которого подключен к информационному выходу первого блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Генератор широкополосных случайных процессов | 1980 |

|

SU881743A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

Изобретение относится к вычислительной технике и может быть использовано для моделирования случайных процессов при исследовании сложных систем, fe частности для воспроизведения случайньк вибропроцессов с заданной спектральной плотностью мощности при исследовании надежности сложных систем с помощью вибростендо

Цель изобретения - расишрение

функциональных возможностей устройства за счет формирования случайных процессов с произвольной фазочастотной характеристикой.

-h(k) - h(N + k) , если x(n - k) -h(k) +h(N + k), если x(n - k) h(k) - h(N + k) , если x(n - k) h(k) + h(N + k), если x(n - k)

-h(k) - h(N + k), -h(k) + h(N + k), h(k) - h(N + k), h(k) + h(N + k).

Обозначим Z(k, 1) h(k)+ h(N +

k) и Z(k, 2) h(k) - h(N+ k) ,

-ii(k, 1) , еслиx(n - k)

Y, j-ZCk, 2), еслиx(n - k)

Z(k, 2), еслиx(n - k)

Z(k, 1), еслиx(n - k)

В предлагаемом цифровом формирователе спектра применен другой подход к решению задач увеличения быстродействия цифрового нерекурсивного ;фильтра бинарного сигнала с нелинейной фазочастотной характеристикой и увеличения точности задания спектральной плотности мощностц.

Положим Z(k) h(k)x(n - k) + + h.(N + k).x(n - N - k) , тогда для рассчитанной весовой функции цифрового нерекурсивного фильтра с заданной (в общем случае - нелинейной) фазочастотной характеристикой процесс образования будет следующий.

x(n

k),

k) k) k) k) k), x(n

k), x(n k). x(n

тогда процесс образования Z(k) можно представить в виде

-1и х(п - k) х(п- N - k),

-1и х(п - k) х(п- N - k),

1и х(п - k) х(п- N - k),

1и х(п - k) х(п- N - k) ,

3

Если расчет Z(k, j), где j 1,2 произвести на ЭВМ (в блоке задания, коэффициентов), а в блок весовых коэффициентов цифрового фильтра записать рассчитанные значения Z(k,j) формирование одного выходного отсчета уСп) можно осуществить, как и в случае формирования случайного процесса с линейной фазочастотной характеристикой в известном устройстве, за N элементарньт тактов при помощи только одного цифрового нерекурсивного фильтра.

Увеличение точности задания спектральной плотности мощности при одновременном упрощении устройства достигается в предлагаемом цифровом формирователе спектра применением двух умножителей вькодных отсчетов генерируемого .случайного процесса. При этом первый цифровой. , умножитель, реализованньй на регистре сдвига (регистр сдвига выполняет также функции регистра-аккумулятора накапливающего сумматора), осуществляется умножение кодов выходных отсчетов на являющуюся целой степенью числа два величину, такую, что результате умножения кодов выходных отсчетов н-а дайную величину используется полная разрядная сетка цифроаналогового преобразователя. Второй аналоговьпЧ умножитель предназначен для управления уровнем генерируемого процесса..

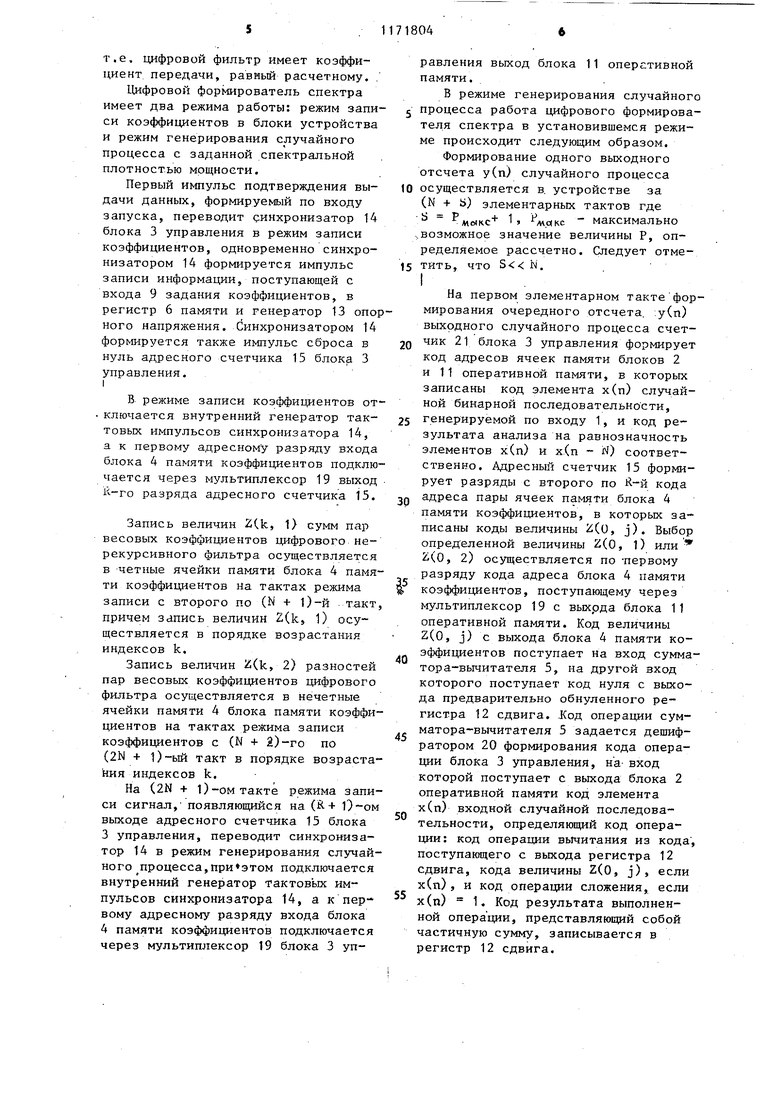

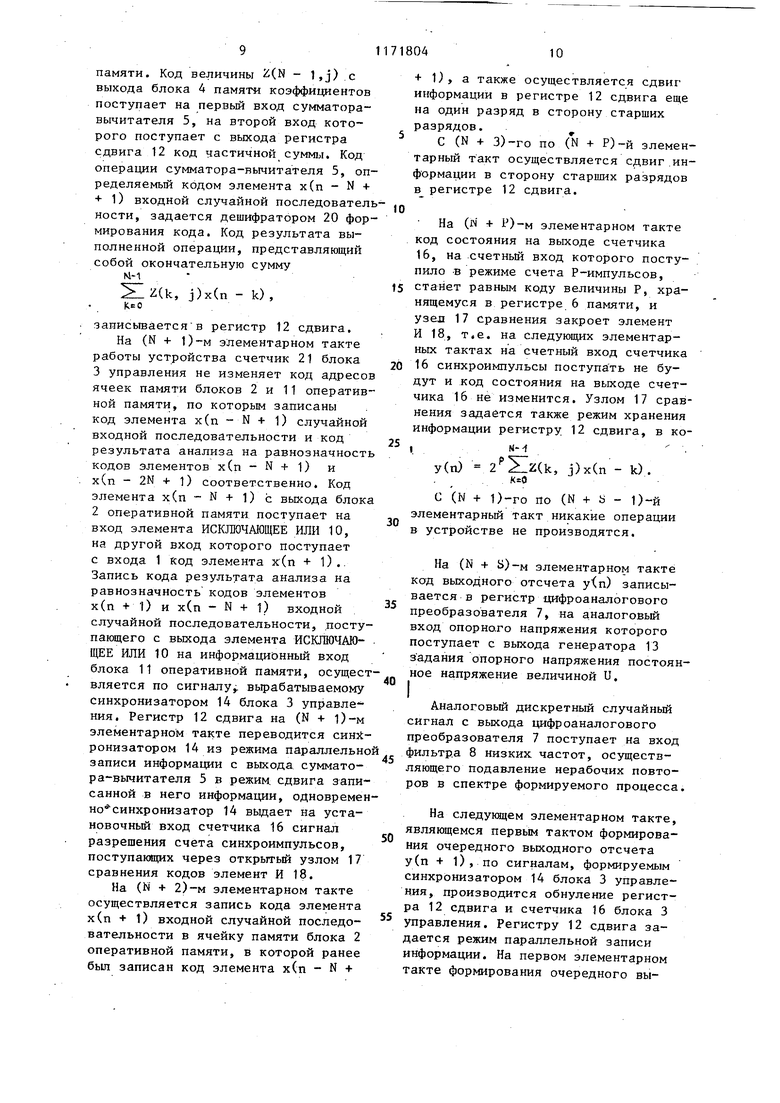

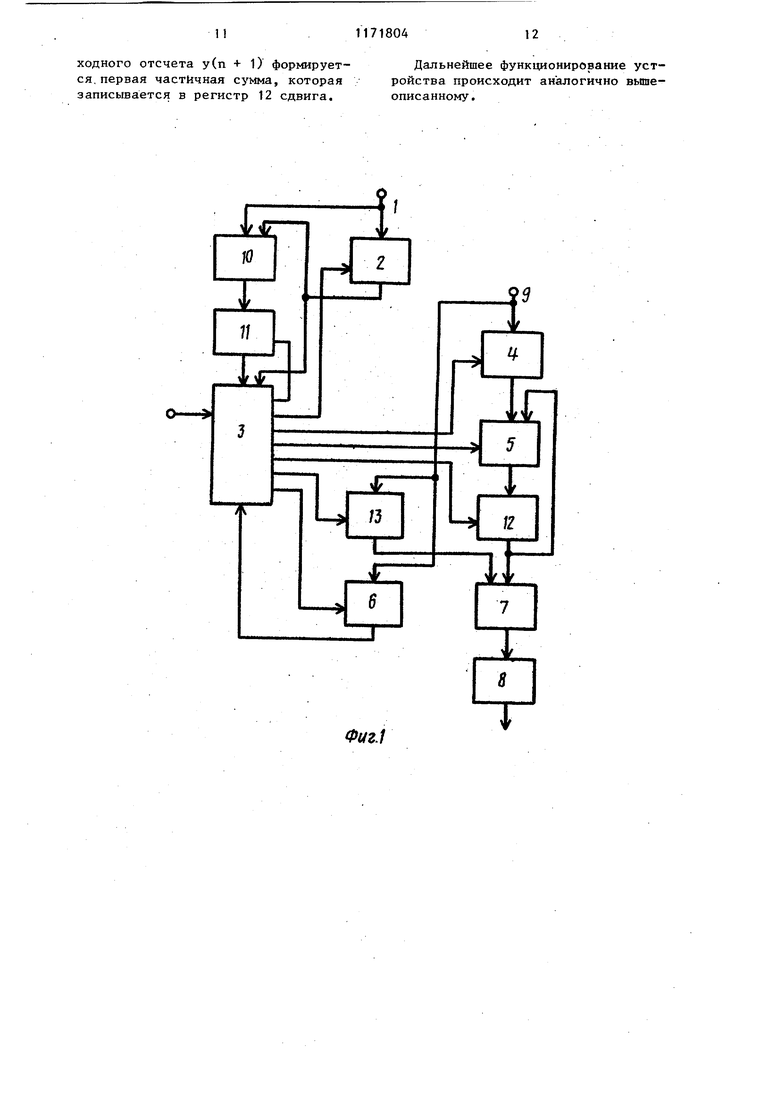

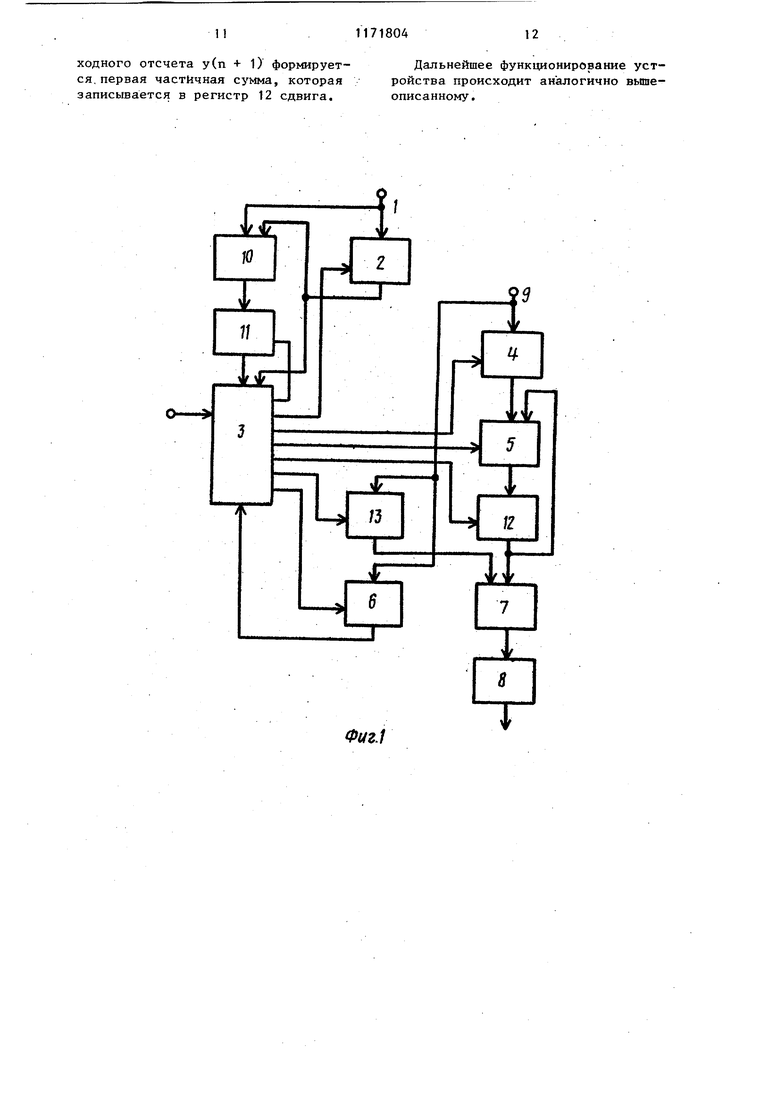

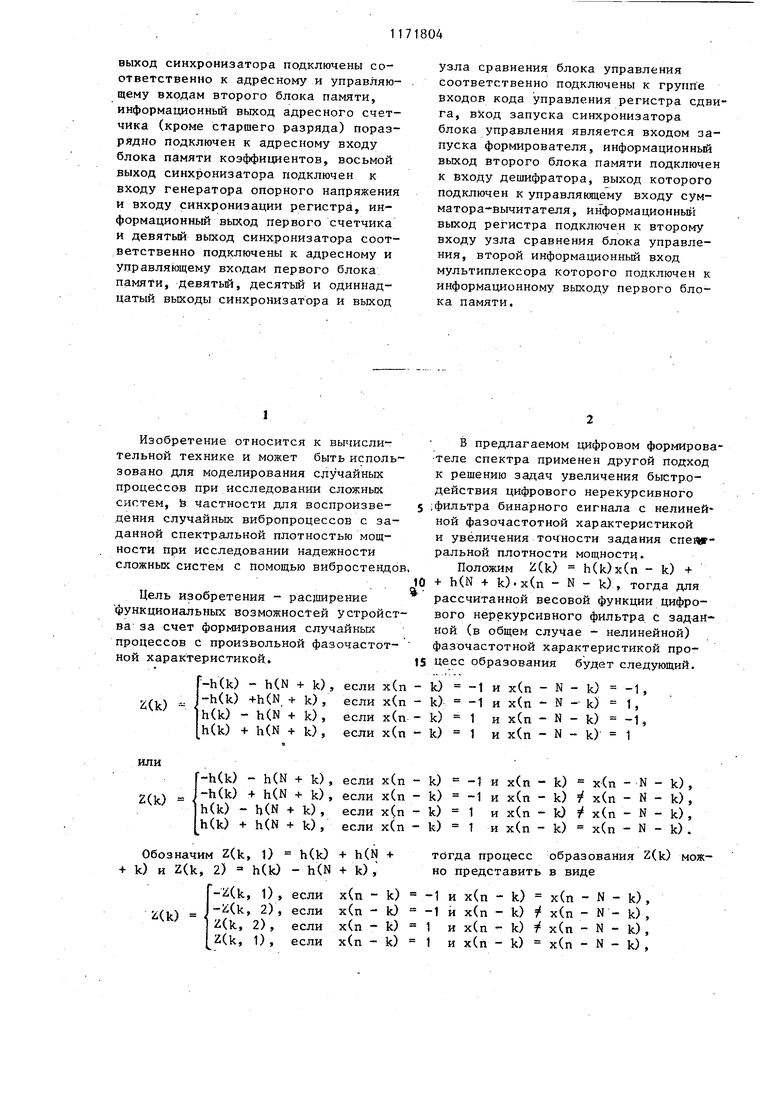

На фиг. 1 представлена схема цифрового- формирователя спектра на фиг. 2 - структурная схема блока управления; на фиг. -3 - временная диаграмма.

Цифровой формирователь спектра содержит информационный вход 1 устройства, блок 2 (оперативной) памяти, блок 3 управления, блок 4 памяти коэффициентов, сумматор-вычитатель 5, регистр (памяти) 6, цифроаналоговый преобразователь 7, фильтр 8 низких частот, вход 9 задания коэффициентов, элемент ИСКЛЮЧАЩЕЁ ИЛИ 10, блок 11 (оперативной) памяти, регистр 12 сдвига, генератор 13 опорного напряжения.

Блок 3 управления содержит синхронизатор 14,адресный счетчик 15, счетчик 16, узел 17 сравнения, элемент И 18, мультиплексор 19, дешифратор 20 (формирования Кода операции) и счетчик 21.

718044

Цифровой формирователь спектра работает следующим образом.

Для обеспечения генерирования цифровым формирователем спектра 5 случайного процесса с заданной спектральной платностью мощности осуществляется расчет весовых коэффициентов h(k) цифрового нерекурсивного фильтра в соответствии с одним 10 из Известных алгоритмов, обеспечиваю1цих максимальную точность задания спектральной плотности мощности. Их массива полученных весовых коэффициентов цифрового фильтра форми15 РУются пары весовых коэффициентов h(k) и h(N + k), где k О, 1, ..., N - 1, и вычисляются их линейные комбинации : сумма

20 k, 1) h(k) + h(N + k) разность

Z-(k, 2) h(k) - h(N + k). Полученный массив величин Z(k,j) 5 масштабируется в соответствии с фор- мулой

Z(k, j)

I r .

2(k, j)

Т

макс {

km, J

Затем осуществляется расчет коэффициента передачи цифрового фильтра без учета выполнения операции сдвига

км

г макс {Z(k, l)/,/Z(k, 2)j.

МО

По полученному значению коэффициента передачи цифрового фильтра определяется величина Р, являющаяся целым числом:

Р L - log |SJ,

где L - разрядность регистра сдвига; означает операцию взятия

ближайшего целого числа, не

меньшего log р.

Величина Р определяет количество сдвигов в регистре сдвига в сторону старших разрядов кодов отсчетов формируемого случайного процесса, при котором старший значащий разряд максимально возможного кода выходного отсчета не выйдет за пределы разрядной сетки регистра сдвига.

Далее осуществляется расчет величины V, записьшаемой в блок задания опорного напряжения, по формуле

V 2макс{/г(тп, j)/j ,

т.е. цифровой фильтр имеет коэффициент передачи, равный расчетному, .

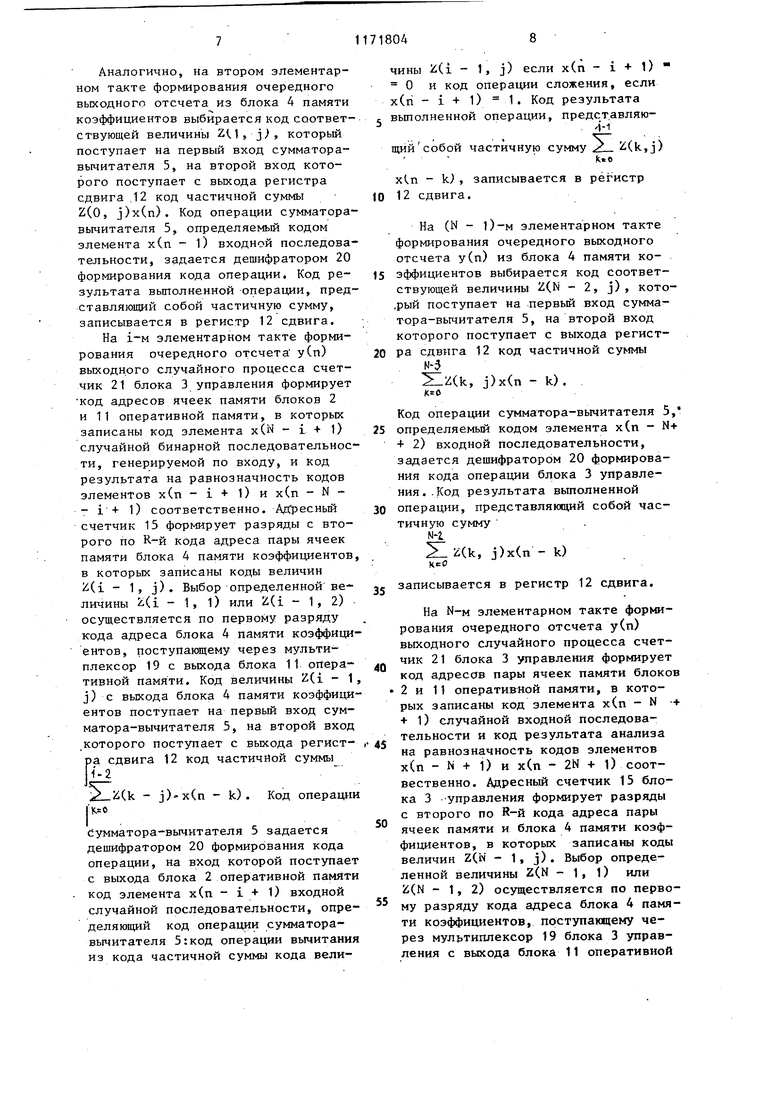

Цифровой формирователь спектра имеет два режима работы: режим записи коэффициентов в блоки устройства и режим генерирования случайного процесса с заданной спектральной плотностью мощности.

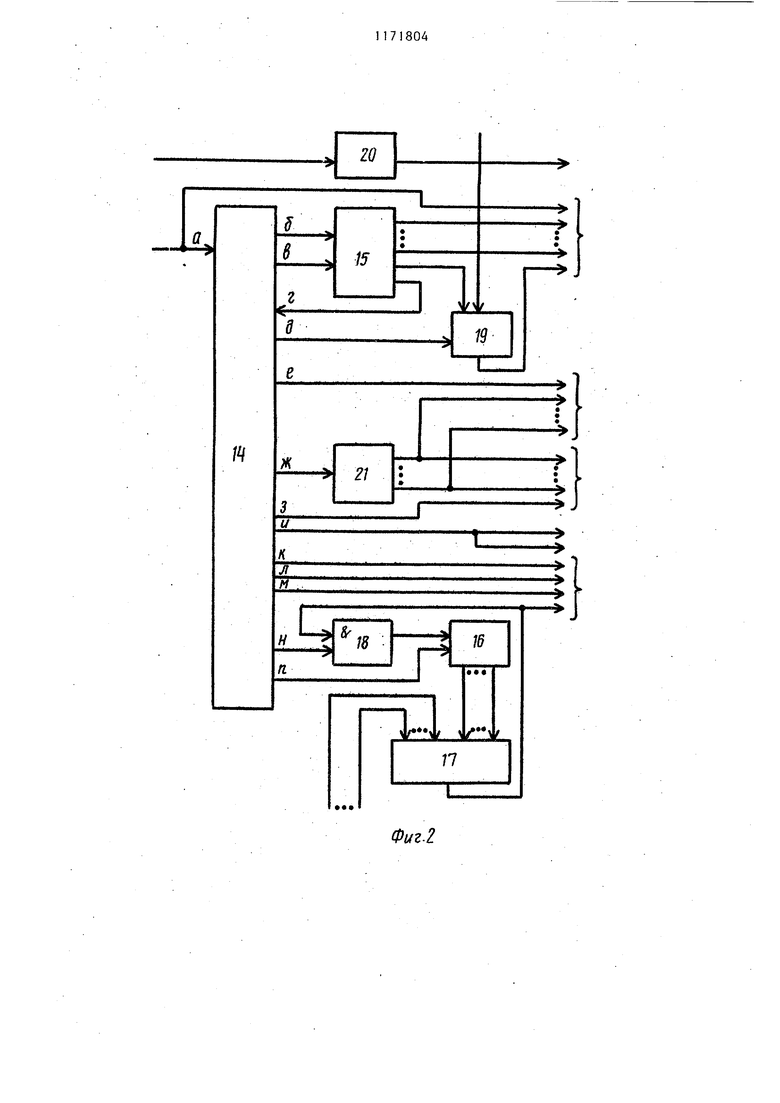

Первый импульс подтверждения выдачи данных, формируемый по входу запуска, переводит синхронизатор 14 блока 3 управления в режим записи коэффициентов, одновременно синхронизатором 14 формируется импульс записи информации, поступающей с входа 9 задания коэффициентов, в регистр 6 памяти и генератор 13 опорного напряжения. Синхронизатором 14 формируется также импульс сброса в нуль адресного счетчика 15 блока 3

управления. I

В режиме записи коэффициентов от ключается внутренний генератор тактовых импульсов синхронизатора 14, а к первому адресному разряду входа блока 4 памяти коэффициентов подключается через мультиплексор 19 выход разряда адресного счетчика 15.

Запись величин Z(.k, 1) пар весовых коэффициентов цифрового нерекурсивного фильтра осуществляется в -четные ячейки памяти блока 4 памяти коэффициентов на тактах режима записи с второго по (N + 1)-й такт причем запись величин Z(kj 1) осуществляется в порядке возрастания индексов k.

Запись величин i;(k, 2) разностей пар весовых коэффициентов цифрового фильтра осуществляется в нечетные ячейки памяти Д блока памяти коэффициентов на тактах режима записи коэффициентов с (N + 2)-го по (2N + 1)-ь1й такт в порядке возрастания индексов k.

На (2N + 1)-ом такте режима записи сигнал, появляющийся на (Й-+ 1)-ом вьпсоде адресного счетчика 15 блока

3управления, переводит синхронизатор 14 в режим генерирования случайного процесса, подключается внутренний генератор тактовых импульсов синхронизатора 14, а к первому адресному разряду входа блока

4памяти коэффициентов подключается через мультиплексор 19 блока 3 управления выход блока 11 оперативной памяти.

В режиме генерирования случайного 5 процесса работа цифрового формирователя спектра в установившемся режиме происходит следующим образом. Формирование одного выходного отсчета у(п) случайного процесса to осуществляется в. устройстве за (N + Ь) элементарных тактов где мо1кс+ 1 м.йкс максимально .возможное значение величины Р, определяемое рассчетно. Следует отметить, что S« N.

На первом элементарном тактеформирования очередного отсчета, у(п) выходного случайного процесса счетчик 21 блока 3 управления формирует

0 код адресов ячеек памяти блоков 2 и 11 оперативной памяти, в которых записаны код элемента х(п) случайной бинарной последовательности, генерируемой по входу 1, и код ре5зультата анализа на равнозначность элементов х(п) и х(п - N) соответственно. Адресный счетчик 15 формирует разряды с второго по Л-й кода адреса пары ячеек памяти блока 4

0 памяти коэффициентов, в которых записаны коды величины ZCu, j). Выбор определенной величины 2(0, 1) или 2i(0, 2) осуществляется по -первому разряду кода адреса блока 4 памяти коэффициентов, поступающему через мультиплексор 19 с выхрда блока 11 оперативной памяти. Код величины Z(0, j) с выхода блока 4 памяти коэффициентов поступает на вход сумматора-вычитателя 5, на другой вход которого поступает код нуля с выхода предварительно обнуленного регистра 12 сдвига. .Код операции сумматора-вычитателя 5 задается дешифратором 20 формирования кода операции блока 3 управления, на- вход которой поступает с выхода блока 2 оперативной памяти код элемента х(п) входной случайной последова0тельности, определяющий код операции: код операции вычитания из кода, поступающего с выхода регистра 12 сдвига, кода величины 2(0, j), если х(п), и код операции сложения, если

5 х(п) - 1. Код результата выполненной операции, представляющий собой частичную , записывается в регистр 12 сдвига. Аналогично, на втором элементарном такте формирования очередного выходного отсчета из блока 4 памяти коэффициентов выбирается код соответ ствующей величины ZUj J), который поступает на первый вход сумматоравычитателл 5, на второй вход которого поступает с выхода регистра сдвига ,12 код частичной суммы 2(0, j)x(n). Код операции сумматора вычитателя 5, определяемый кодом элемента к(п - 1) входной последова тельности, задается дешифратором 20 формирования кода операции. Код результата выполненной операции, пред ставляющий собой частичную сумму, записывается в регистр 12 сдвига. На i-M элементарном такте формирования очередного отсчета у(п) выходного случайного процесса счетчик 21 блока 3 управления формирует КОД адресов ячеек памяти блоков 2 и 11 оперативной памяти, в которых записаны код элемента x(N - i + 1) случайной бинарной последовательнос ти, генерируемой по входу, и код результата на равнозначность кодов элементов х(п - i 1) и х(п - N - i + 1) соответственно. АдГресньй счетчик 15 формирует разряды с второго по R-й кода адреса пары ячеек памяти блока 4 памяти коэффициентов в которых записаны коды величин . - 1, j). Выбор определенной величины (i -1,1) или 2(1 -1,2) осуществляется по первому разряду кода адреса блока 4 памяти коэффици ентов, поступающему через мультиплексор 19 с выхода блока 11 оперативной памяти. Код величины 2(1 - 1 J) с выхода блока 4 памяти коэффици ентов поступает на первый вход сумматора-вычитателя 5, на второй вход .которого поступает с выхода регист|а сдвига 12 код частичной суммы 1-2 2(k - j)-x(n - k). Код операции сумматора-вычитателя 5 задается дешифратором 20 формирования кода операции, на вход которой поступает с выхода блока 2 оперативной памяти код элемента х(п - 1 + 1) входной случайной последовательности, определяющий код операции сумматоравьмитателя 5:код операции вычитания из кода частичной суммы кода велиины - , j) если х(п- 1) 0 и код операции сложения, если (п - 1 + 1) 1. Код результата ьшолненной операции, представляюi-1ийсобой частичную сумму . 2(k,j) х(,п - k) , записывается в регистр 12 сдвига. На (N - 1)-м элементарном такте формирования очередного выходного отсчета у(п) из блока 4 памяти коэффициентов выбирается код соответствующей величины 2(N - 2, j), кото,рый поступает на первый вход сумматора-вычитателя 5, на второй вход которого поступает с выхода регистра сдвига 12 код частичной суммы 5Iz(k, j)x(n - k). Код операции сумматора-вычитателя 5, определяемый кодом элемента х(п - N+ 2) входной последовательности, задается дешифратором 20 формирования кода операции блока 3 управления ..Код результата вьтолненной операции, представляющий собой частичную сумму N-1 X. 2(k, j)K(n - k) записывается в регистр 12 сдвига. На N-M элементарном такте формирования очередного отсчета у(п) выходного случайного процесса счетчик 21 блока 3 управления формирует код адресов пары ячеек памяти блоков 2 и 11 оперативной памяти, в которых записаны код элемента х(п - N -+ 1) случайной входной последовательности и код результата анализа на равнозначность кодов элементов х(п - N + 1) и х(п - 2N + 1) соотвественно. Адресный счетчик 15 блока 3 управления формирует разряды с второго по R-и кода адреса пары ячеек памяти и блока 4 памяти коэффициентов, в которых записаны коды величин Z(bi - 1, j) , Выбор определенной величины Z(N - 1, 1) или 2(N -1,2) осуществляется по первому разряду кода адреса блока 4 памяти коэффициентов, поступающему через мультиплексор 19 блока 3 управления с выхода блока 11 оперативной памяти. Код величины ( ) с выхода блока 4 памяти коэффициентов поступает на первый вход сумматоравычитателя 5, на второй вход которого поступает с выхода регистра сдвига 12 код частичной суммы. Код операции сумматора-вычитателя 5, определяемый кодом элемента х(п - N + 1) входной случайной последователь ности, задается дешифратором 20 формирования кода. Код результата выполненной операции, представляющий собой окончательную сумму м-1 Z(k, j)x(n - k), КеО записываетсяВ регистр 12 сдвига. На (N + 1)-м элементарном такте работы устройства счетчик 21 блока 3 управления не изменяет код адресов ячеек памяти блоков 2 и 11 оперативной памяти, по которым записаны код элемента х(п - N + 1) случайной входной последовательности и код результата анализа на равнозначность кодов элементов х(п - N + 1) и х(п - 2N + 1) соответственно. Код элемента х(п - N + 1) с выхода блока 2 оперативной памяти поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, на другой вход которого поступает с входа 1 код элемента х(п +1).. Запись кода результата анализа на равнозначность кодов элементов х(п +1) и х(п - N + 1) входной случайной последовательности, посту пающего с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 на информационный вход блока 11 оперативной памяти, осущест вляется по сигналу вырабатываемому синхронизатором 14 блока 3 управления. Регистр 12 сдвига на (N + 1)-м элементарном такте переводится CHHJt ронизатором 14 из режима параллельн записи информации с выхода сумматора-вычитателя 5 в режим, сдвига записанной в него информации, одновреме но синхронизатор 14 выдает на установочный вход счетчика 16 сигнал разрешения счета синхроимпульсов, поступающих через открытьй узлом 17 сравнения кодов элемент И 18. На (N + 2)-м элементарном такте осуществляется запись кода элемента х(п + 1) входной случайной последовательности в ячейку памяти блока 2 оперативной памяти, в которой ранее бьт записан код элемента х(п - N + + 1), а также осуществляется сдвиг информации в регистре 12 сдвига еще на один разряд в сторону старших разрядов. С (N + 3)-го по (N + Р)-й элементарный такт осуществляется сдвиг .информации в сторону старших разрядов в регистре 12 сдвига. На (JN + Р)-м элементарном такте код состояния на выходе счетчика 16, На счетный вход которого поступило -в режиме счета Р-импульсов, станет равным коду величины Р, хранящемуся в регистре 6 памяти, и узел 17 сравнения закроет элемент И 18, . на следующих элементарных тактах на счетный вход счетчика 16 синхроимпульсы поступать не будут и код состояния на выходе счетчика 16 не изменится. Узлом 17 сравнения задается также режим хранения информации регистру 12 сдвига, в ко22L.Z(k, j)x(n - k). с (N + 1)-го по (N + 8 - 1)-й элементарный такт никакие операции в устройстве не производятся. На (N + S)-M элементарном такте кад выходного отсчета ) записывается в регистр цифроаналогового преобразователя 7, на аналоговый вход опорного напряжения которого поступает с выхода генератора 13 задания опорного напряжения постоянное напряжение величиной U, Аналоговый дискретный случайный сигнал с выхода цифроаналогового преобразователя 7 поступает на вход фильтра 8 низкик частот, осуществляющего подавление нерабочих повторов в спектре формируемого процесса. На следующем элементарном такте, являющемся первым тактом формирования очередного выходного отсчета у(п + 1), по сигналам, формируемым синхронизатором 14 блока 3 управления, производится обнуление регистра 12 сдвига и счетчика 16 блока 3 управления. Регистру 12 сдвига задается режим параллельной записи информации. На первом элементарном такте формирования очередного выходного отсчета у(п + 1) формируется, первая частичная сумма, которая записывается в регистр 12 сдвига.

О-

Дальнейшее функционирование устройства происходит аналогично вышеописанному.

Фиг.2 Запись кОягкрициентоЙ Геиециуобатк случайного / npovfcca---. й-iP

| Генератор широкополосных случайных процессов | 1978 |

|

SU771652A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Петровский А.А | |||

| Программируемый специализированный процессор для цифровой системы управления спектральной матрицей векторного случайного процессора | |||

| - Кибернетика и вычислительная техника | |||

| Киев | |||

| Наукова думка, 1980, вып | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

Авторы

Даты

1985-08-07—Публикация

1984-02-23—Подача