(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЛИТЕЛЬНОСТИ ФРОНТОВ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения длительности фронтов импульсов | 1983 |

|

SU1167539A2 |

| ИЗБИРАТЕЛЬНОЕ УСТРОЙСТВО ИДЕНТИФИКАЦИИ ВЫЗОВА ОТ АБОНЕНТА | 1998 |

|

RU2136050C1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2005 |

|

RU2292582C1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1981 |

|

SU972497A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Устройство для измерения длительности фронтов импульсов | 1986 |

|

SU1357878A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА ПЕРЕДАЧИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 1986 |

|

SU1840556A2 |

| Цифровой фазометр | 1989 |

|

SU1711090A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОМАТОМ ДЛЯ УКЛАДКИ КИРПИЧА | 1991 |

|

RU2028208C1 |

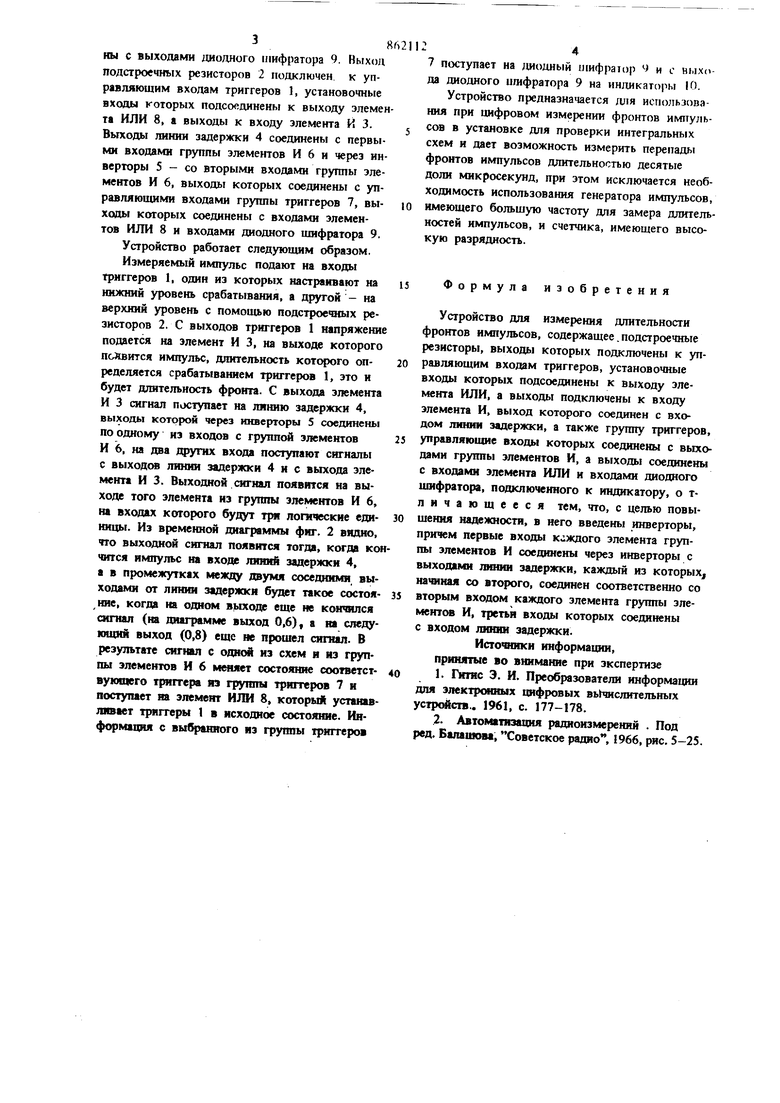

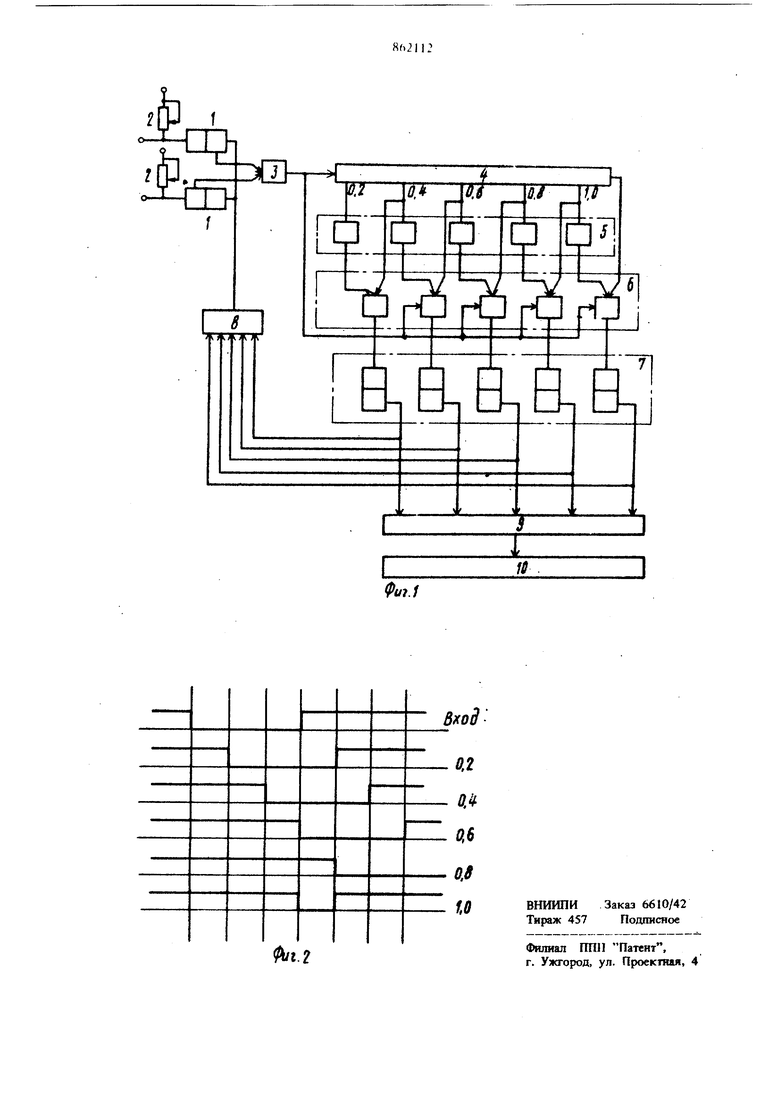

Изобретение относится к области вычислительной техники и может быть использовано в исследовательских колтлексах при проектир вании или исследовании интегральных схем, а также в измерительной технике. Известно устройство для измерения длительностн фронтов импульсов, содержащее две линии задержки, многоразрядный счетчик, вспомогательный счетчик и генератор высокочастотных импульсов 1. Наиболее близким по технической сущности к изобретению является устройство для измерения длительности фронтов импульсов, содержащее подстроечные резисторы, выходы которых подключены к управляющим входамтриггеров, установочные входы которых подсоединены к выходу элемента ИЛИ, а выходы подключены к входу элемента И, выход которого соединен с входом линии задержки, а также группу триггеров, управля1ощие входы которых соединены с выходами группы элементов И, а выходы соединены с входами элемента ИЛИ и входами диодного шифратора, подключенного к индакатору 2). бднако эти устройства недостаточно надежнь и трудно реализуемы. Целью настоящего изобретения является повышение надежности. Цель достигается тем, что в устройство введены инверторы, причем первые входы каждого элемента группы элементов И соединены через инверторы с выходами линии задержки, каждый из которых, начиная со второго, соединен соответственно со вторым входом каждого элемента группы элементов И, третьи входь которых соединены с входом лннни задержки. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временные диаграммы работы группы элементов И. . Устройство содержит: триггеры 1, подстроечные резисторы 2, элемент И 3, линию задержки 4, инверторы 5, группу элементов И б, группу триггеров 7, элемент ИЛИ 8, диодный шифратор 9, ннднкаторы 10. Вход лннин задержки 4 соединен с выходом элемента И 3 и третьими входами группы элементов И 6. Входы индикаторов 10 соедине38

ны с выходами диодного шифратора 9. Ныход подстроечиых резисторов 2 подключен к управляющим входам триггеров 1, установочные входы которых подсоединены к выходу элемента ИЛИ 8, а выходы к входу элемента ИЗ. Выходы линии задержки 4 соединены с первыми входами группы элементов И 6 и через инверторы 5 - со вторыми входами группы элементов И 6, выходы которых соединены с управляющими входами группы триггеров 7, выходы которых соедннены с входами элементов ИЛИ 8 и входами диодного шифратора 9, Устройство работает следуюшим образом. Измеряемый импульс подают иа входы триггеров 1, один из которых настраивают на нижний уровень срабатывания, а другой - на верхний уровень с помощью подстроечных резисторов 2. С выходов триггеров 1 напряжение подается на элемент И 3, на выходе которого появится импульс, длительность которого определяется срабатыванием триггеров 1, это и будет длительность фронта. С выхода элемента И 3 сигнал поступает на линию задержки 4, выходы которой через инверторы 5 соединены по одному из входов с грушюй элементов

И 6, на два fffynvi входа поступают сигналы с выходсл линии задержки 4 и с выхода элемента И 3. Выходной сигнал появится на выходе того элемента из группы элементов И 6, на входах которого будут трт логические единицы. Из временной диаграммы фиг. 2 видно, что выходной сигнал появится тогда, когда кочится импульс иа входе линий задержки 4, а в промежутках между двумя соседними выходами от линии задержки будат такое состояние, когда на одном вь1ходе еще не кончился сигнал (на диаграмме выход 0,6), а на следующий выход (0,8) еще не прошел сигнал. В результате сигнал с одной из схем и из группы элементов И 6 меняет состояние соогветствующего тртггера яэ группы триггеров 7 и поступает на элемент ИЛИ 8, который устанавливает триггеры 1 в исходиое состояние. Информация с выбранного из группы триггеров

7 поступает на диодный игифрагор ч и с ныхо да диодного ишфратора 9 на индикаторы 10.

Устройство предназначается для использования при цифровом измерении фронтов имгтульсов в установке для проверки интегральных схем и дает возможность измерить перепады фронтов импульсов длительностью десятые доли микросекунд, при этом исключается необходимость использования генератора импульсов, имеющего большую частоту для замера длительностей импульсов, и счетчика, имеющего высокую разрядность.

Формула изобретения

Устройство для измерения длительности фронтов импульсов, содержащее. подстроечные резисторы, выходы которых подключены к управляющим входам триггеров, установочные входы которых подсоединены к выходу элемента ИЛИ, а выходы подключены к входу элемента И, выход которого соединен с входом линии задержки, а также грушту триггеров, управляющие входы которых соединены с выходами грутшы элементов И, а выходы соединены с входами элемента ИЛИ и входами диодного шифратора, подключеииого к индикатору, о тличающееся тем, что, с целью повышения надежности, в него введены инверторы, причем первые входы каждого элемента группы элемеитов И соединены через инверторы с выходами ;шшш задержки, каждьт из которых, начиная со второго, соединен соответственно со вторым входом каждого элемента группы элементов И, третьи входы которых соединены с входом линии задержки.

Источники информации,

принятые во внимание при зкспертизе

.2- Автокштизация радиоизмерений . Под ред. Балашон. Советское радио, 1966, рис. 5-25.

Авторы

Даты

1981-09-07—Публикация

1976-09-27—Подача