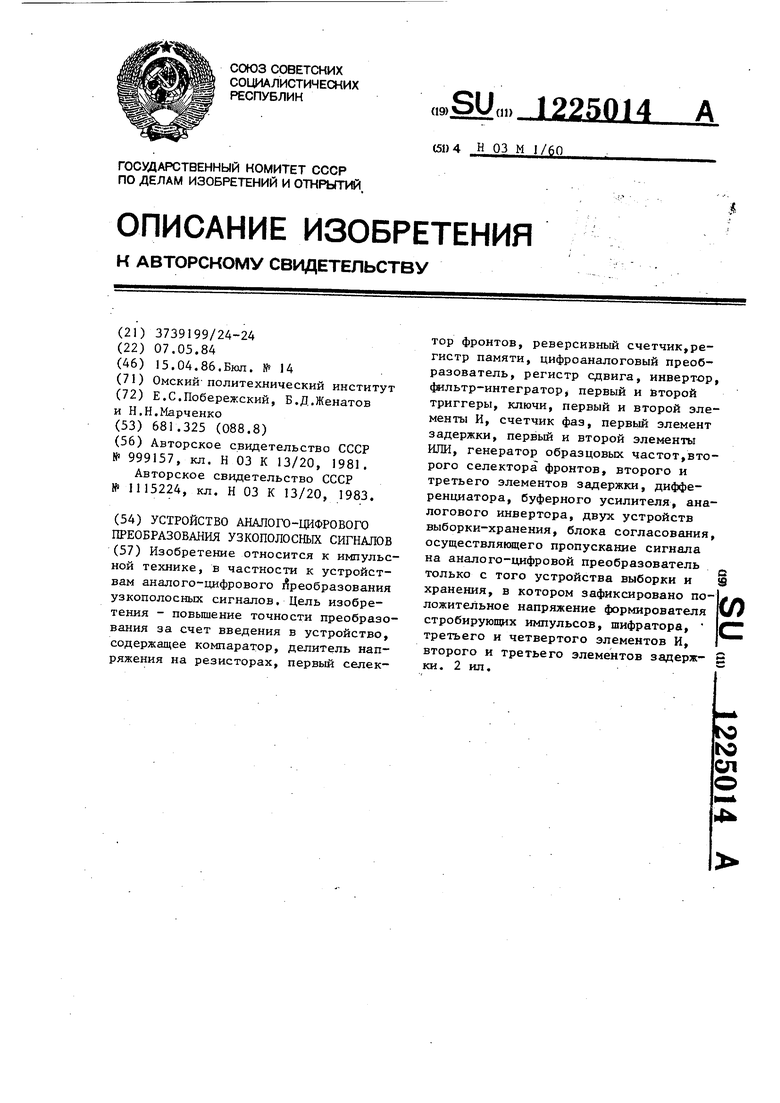

Изобретение относится к импульсной технике и может использоваться при аналого-цифровом преобразовании узкополосных сигналов, у которых ширина спектра много меньше центральной частоты.

Цель изобретения - повышение точности преобразования.

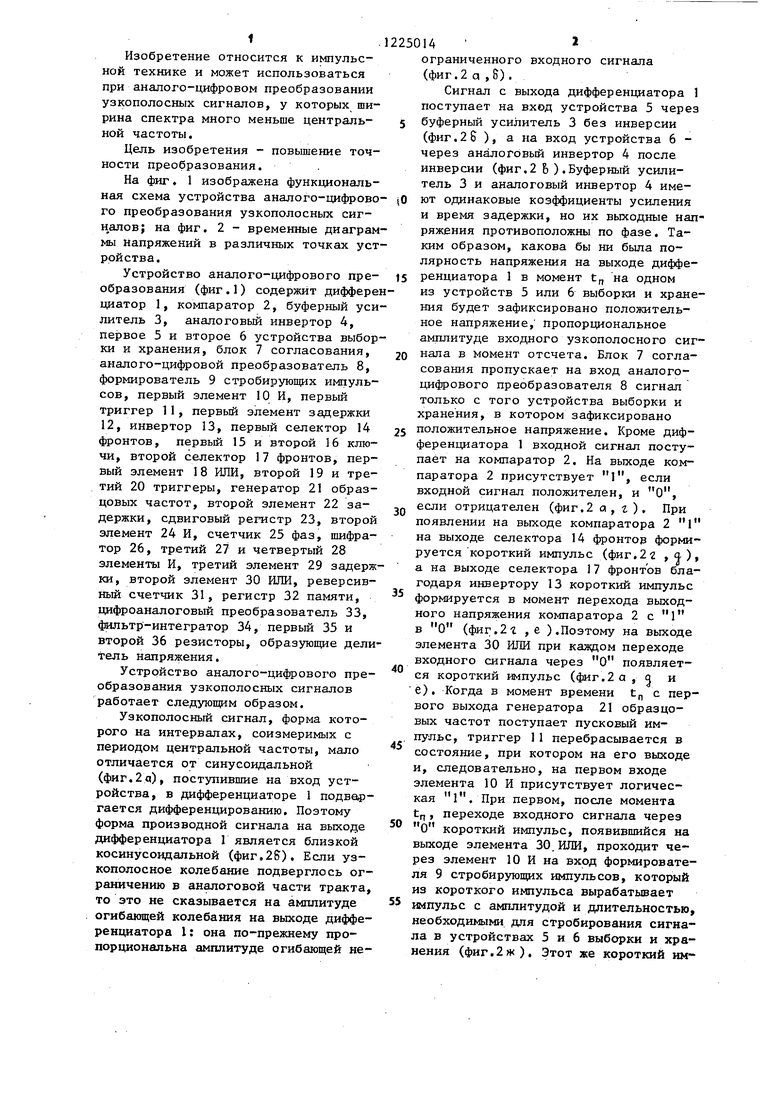

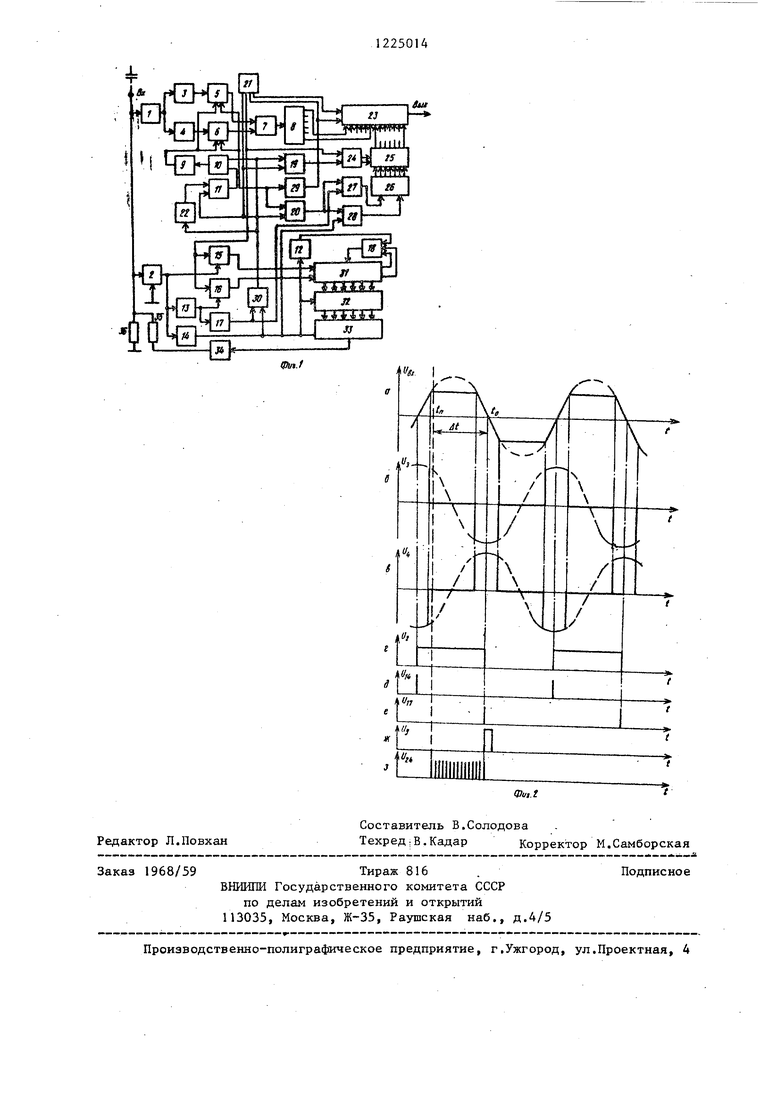

На фиг. 1 изображена функциональная схема устройства аналого-цифрового преобразования узкополосных сиг- н алов; на фиг. 2 - временные диаграммы Напряжений в различных точках устройства.

Устройство аналого-цифрового преобразования (фиг.1) содержит дифферециатор 1, компаратор 2, буферный усилитель 3, аналоговый инвертор 4, первое 5 и второе 6 устройства выборки и хранения, блок 7 согласования, аналого-цифровой преобразователь 8, формирователь 9 стробирующих импульсов, первый элемент 10 И, первый триггер 11, первый элемент задержки 12, инвертор 13, первый селектор 14 фронтов, первый 15 и второй 16 ключи, второй селектор 17 фронтов, первый элемент 18 ИЛИ, второй 19 и третий 20 триггеры, генератор 21 образцовых частот, второй элемент 22 задержки, сдвиговый регистр 23, второй элемент 24 И, счетчик 25 фаз, шифратор 26, третий 27 и четвертый 28 элементы И, третий элемент 29 задержки, второй элемент 30 ИЛИ, реверсивный счетчик 31, регистр 32 памяти, цифроаналоговый преобразователь 33, фильтр-интегратор 34, первый 35 и второй 36 резисторы, образующие делитель напряжения.

Устройство аналого-цифрового преобразования узкополосных сигналов работает следующим образом.

Узкополосный сигнал, форма которого на интервалах, соизмеримых с периодом центральной частоты, мало отличается от синусоидальной (фиг.2я), поступившие на вход устройства, в дифференциаторе 1 подвергается дифференцированию. Поэтому форма производной сигнала на выходе дифференциатора 1 является близкой косинусоидальной (фиг.2&). Если узкополосное колебание подверглось ограничению в аналоговой части тракта, то это не сказывается на амплитуде огибающей колебания на выходе дифференциатора I: она по-прежнему пропорциональна амплитуде огибающей не

ограниченного входного сигнала (фиг.2 а,S).

Сигнал с выхода дифференциатора 1 поступает на вход устройства 5 через буферный усилитель 3 без инверсии (фиг.2& ), а на вход устройства 6 - через аналоговый инвертор 4 после инверсии (фиг.2 Ь).Буферный усилитель 3 и аналоговый инвертор 4 имеют одинаковые коэффициенты усиления и время задержки, но их вьпсодные напряжения противоположны по фазе, Таким образом, какова бы ни была полярность напряжения на выходе дифференциатора 1 в момент t на одном из устройств 5 или 6 выборки и хранения будет зафиксировано положительное напряжение, пропорциональное амплитуде входного узкополосного сигнала в момент отсчета. Блок 7 согласования пропускает на вход аналого- цифрового преобразователя 8 сигнал только с того устройства выборки и хранения, в котором зафиксировано положительное напряжение. Кроме дифференциатора 1 входной сигнал поступает на компаратор 2. На выходе компаратора 2 присутствует 1, если входной сигнал положителен, и О, если отрицателен (фиг.2 а, г). При появлении на выходе компаратора 2 1 на выходе селектора 14 фронтор формируется короткий импульс (фиг,2 г Ч- ) а на выходе селектора 17 фронтов благодаря инвертору 13 короткий импульс формируется в момент перехода выходного напряжения компаратора 2 с 1 в О (фиг,2г ,е ).Поэтому на выходе элемента 30 ИЛИ при каждом переходе входного сигнала через О появляется короткий импульс (фиг.2 а , и е). Когда в момент времени t с первого выхода генератора 21 образцовых частот поступает пусковый импульс, триггер 11 перебрасывается в состояние, при котором на его выходе и, следовательно, на первом входе элемента 10 И присутствует логическая 1. При первом, после момента переходе входного сигнала через О короткий импульс, появившийся на выходе элемента 30. ИЛИ, проходит через элемент 10 И на вход формирователя 9 стробирующих импульсов, который из короткого импульса вырабатывает импульс с амплитудой и длительностью, необходимыми для стробирования сигнала в устройствах 5 и 6 выборки и хранения (фиг,2ж). Этот же короткий имЦ.

п

пульс, задержанный в элементе 22 задержки на время, достаточное для запуска формирователя 9, возвращает триггер I1 в состояние, при котором на его выходе и, следовательно, на первом входе элемента 10 И-логичес- кий . В результате короткие импульсы с выхода элемента 30 ИЛИ не проходят на вход формирователя 9 строби- рующих импульсов до появления- следую- .щего пускового импульса, т.е. до мо-: мента взятия следующей пары отсчетов. При поступлении на управляющие входы устройств, 5 и 6 выборки и хранения стробирующих импульсов с формировате- ля 9 производится выборка, и на вход аналого-цифрового преобразователя 8 благодаря блоку 7 согласования поступает выборка только с того устройства 5 или 6, на входе которого в мо

мент t сигнал имеет положительную полярность. Аналого-цифровой преобразователь 8 переводит эту выборку в цифровой код, поступающий на вторую группу информационных входов сдвигового регистра 23.

Определение отсчетов фазы узкополосного сигнала выполняется путем измерения интервала времени ut от

момента t до момента

t -первого

после- t перехода входного сигнала через нуль (фиг.2 q), Если переход через нуль в момент t положительный (такой переход место, если в момент t входной сигнал отрицателен) , то фаза Ч(Ц) входного сигнала в момент t может быть определена по формуле .

Q(t) 2lt - fit 27f( ut),.

a если переход отрицательный (т.е. входной сигнал в момент t положителен) , то по формуле

l(t) .1- ,ut 2 itf To/2 -ut),

где f - центральная частота входного узкополосного сигнала;

период центральной частоты .

Следовательно, для определения отсчета фазы достаточно отнять число югаульсов, пропорциональное At, от числа, пропорционального Т, ес0

5

0

5

0

5

0

5

0

5

ли в момент t входной сигнал отрицателен, и от числа, пропорционального , если в момент t входной сигнал положителен.

Непосредственно перед поступлением пускового импульса второй триггер 19 находится в состоянии, при котором на его выходе и, следовательно, на первом входе элемента . . 24 И присутствует логический О, а триггер 20 - в состоянии, при котором на его выходе и, следовательно, на первых входах элементов 27 и 28 И присутствует логическая 1. В таком состоянии элемент 24 И не пропускает импульсы заполнения со второго выхода генератора 21 образцовых частот на второй вход счетчика 25 фаз, а элементы 27 и 28 И пропускают на входы шифратора 26 короткие импульсы, поступающие соответственно с выходов селекторов 17 и 14 фронтов. Как указьшалось выще, импульсы на выходе селектора 14 фронтов появляются в начале каждого положительного полупериода входного сигнала (фиг.2 а , а),а импульсы на выходе селектора 17 фронтов - в начале каждого отрицательного полупериода (фиг.2 а, е ). Поэтому шифратор 26 записывает в счетчик 25 фаз при поступлении импульса с выхода селектора 17 фронтов число, пропорциональное Тр, а при поступлении импульса с выхода селектора 14 фронтов - число, пропорциональное Тд/2. Пусковой импульс переводит триггер 19 в сос- тояние, при котором на его выходе и, следовательно, на первом входе элемента 24 И устанавливается логическая 1, а триггер 20 - в состояние, при котором на его вькоде И, следовательно, на первых входах элементов 27 и 28 И устанавливается логический о. В этом состоянии элемент 24 И пропускает импульсы заполнения на второй вход счетчика 25 фаз, работающего в режиме вычитания, а элементы 27 и 28 И не пропускают импульсы с выходов селекторов 17 и 14 фронтов на входы шифратора 26. Таким образом, в момент t, в счетчике 25.фаз оказывается зафиксированным число, пропорциональное Т, если входной импульс поступил в отрицательный полупериод входного сигнала, и число, пропорциональное , если - в положительный полупериод. Из этого числа вычитаются импульсы заполнения.

количество которых пропорционально at (фиг,2 ), так как в момент t импульсом с выхода элемента 20 ИЛИ триггер 19 возвращается в состояние, при котором на его выходе устанавли- Бается логический О, и элемент 24 И перестает пропускать на вход счетчика 25 фаз импульсы заполнения . Таким образом, в счётчике 25 фаз после момента tj, оказывается зафиксированным число, пропорциональное qi(tp) - отс- нету фазы входного сигнала.

Очевидно, что максимальное время измерения, необходимое для взятия па ры отсчетов амплитуды и фазы незначительно превьппает Тд/2, так как измерение фазы заканчивается в момент t а измерение a шлитyды - в момент, за держанный относительно t на -время стробирования, которое мало по сравнению с Тр. Однако, чтобы не предъявлять жестких требований к быстродейсвию аналого-цифрового к быстродействию аналого-цифрового преобразовате- ля 8, считывание информациии с выходов этого преобразователя и счетчика 25 фаз выполняется через несколько периодов центральной частоты после момента окончания измерений. Считывание производится импульсом записи, поступающим с четвертого выхода генератора 21 образцовых частот на управляющий вход сдвигового регистра 23 и на вход элемента задержки 2 При поступлении этого импульса на управляющий вход сдвигового регистра 23 происходит перезапись в регистр цифровых значений отсчетов литуды с выходов аналого-цифрового преобразователя 8 и фазы с выходов разрядов счетчика 25 фаз. После этого импульс записи, пройдя на выход элемента 29 задержки, обнуляет устройства 5 и 6 выборки и хранения, стирая записанную в них информацию, и возвращает триггер 20 в состояние, при котором на его выходе устанавливается логическая 1, и импульсы .с выходов селекторов 17 и 14 фрон- тов через элементы 27 и 28 И проходят на шифратор 26, Тактовые импульсы, поступающе с третьего выхода генератора 21 образцовых частот на соответствующий тактовый вход сдвигового регистра 23, продвигают за- писанные в регистре цифровые значения отсчетов амплитуды на выход устройства.

5

, 55

0

0

5

0

Входной узкополосный сигнал, поступивший на вход, устройства аналого- цифрового преобразования, может быть подвержен не тЬлько двухстороннему симметричному, как это приведено на - фиг.2а, но и одностороннему или двухстороннему несимметричному ограничению по максимуму. При одностороннем или двухстороннем несимметричном ограничении происходит смещение нулевого уровня относительно уровня общей- шины Земля.

Для приведения нулевого уровня к уровню общей шины Земля используются следующие блоки-компаратор 2, инвертор 13, селектор 4 фронтов, ключи 15 и 16, элемент 12 з адержки, элемент 18 ИЛИ реверсивный счетчик 31, регистр 32 памяти, цифроана- логовый преобразователь 33, фильтр- интегратор 34, делитель напряжения на резисторах 25 и 36. Реверсивный счетчик 31 на каждом периоде входного сигнала подсчитывает разность между отрицательным и положительным полупериодами. Цифровое значение этой разности фиксируется в регистре 32 памяти, а затем преобразуется в аналоговую форму с помощью цифро-аналогового преобразователя 33. Фильтр-интегратор 34 накапливает значения разности в течение нескольких периодов сигнала. Выходное напряжение фильтра-интегратора 34, поступающее на входную шину через делитель напряжения на резисторах 35 и 36, компенсирует смещение нулевого уровня.

Формула из обретен и я

Устройство аналого-цифрового преобразования узкополосных сигналов, содержащее генератор образцовьгх частот, счетчик фаз, сдвиговый регистр, первый селектор фронтов, первый элемент задержки, реверсивный счетчик, регистр памяти, цифроаналоговый преобразователь, фильтр-интегратор, делитель напряжения, первый и второй ключи, первый и второй триггеры, инвертор, первый и второй элементы И, два элемента ИЛИ, компаратор, первый вход которого является входной шиной, второй вход соединен с общей шиной, а выход - с входом первого селектора фронтов, с управляющим входом первого ключа и через инвертор с управляющим входом второго ключа, выходы первого и второго ключей соединены соответственно с входами сложения и вычитания реверсивного счетчика, первая группа выходов которого подключе- j на к первой группе входов регистра памяти соответственно, второй вход которого через первый элемент задержки объединен с первым входом первого элемента ИЛИ и непосредственно под- JO ключей к выходу первого селектора фронтов, второй и третий входы первого элемента ИЛИ подключены к второй группе выходов реверсивного счетчика, а выход - к входу сброса ревер- }5 сивного счетчика, выходы регистра памяти подключены соответственно к входам цифроаналогового преобразователя , выход которого через фильтр- интегратор соединен с первым входом 20 делителя напряжения, второй вход которого подключен к общей шине, а выход объединен с первым входом компаратора, первые входы первого и второго триггеров объединены и подключены 25 к первому выходу генератора образцовых частот, выход первого триггера подключен к первому входу первого элемента И, а выход второго триггера подключен к первому входу второго зо элемента И, второй вход которого объединен с информационными входами первого и второго ключей и соединен с вторым выходом генератора образцовых частот, третий выход которого подключен к входу тактовой ча.стоты сдвигового регистра, отличающее- с я тем, что, с целью повышения точности преобразования, в него введены

выходы которых подключены к первым входам соответственно первого и вто рого устройств выборки и хранения, выходы которых подключены соответственно к первому и второму входу блока согласования, выход которого подключен к входу аналого-цифрового преобразователя, вторые входы устройства выборки и хранения объедине ны и подключены к выходу формирователя стробирующих импульсов вход ко торого соединен с выходом первого элемента И, второй вход которого объединен с вторым входом второго триггера, входом второго элемента задержки и подключен к выходу второ го элемента ИЛИ, выход второго элемента задержки соединен с вторым входом первого триггера, первый вход третьего триггера объединен с первы входом первого триггера, второй вход объединен с третьими входами устройств выборки и хранения и соедине с выходом третьего элемента задержки, вход которого объединен с управ ляющим входом сдвигового регистра и соединен с четвертым выходом генера тора образцовых частот, причем первые входы третьего и четвертого эле ментов И объединены и подключены к выходу третьего триггера, а выходы соединены с соответствующими входами шифратора, выходы которого через счетчик фаз подключены соответствен но к первой группе информационных входов сдвигового регистра, вторая группа информационных входов которо го подключена к соответствующим выходам аналого-цифрового преобразова

аналого-цифровой преобразователь, теля, второй вход счетчика фаз соевторой и третий элементы задержки,. второй селектор фронтов, буферный усилитель, аналоговый инвертор, два устройства выборки и хранения, третий и четвертый элементы И, шифратор, блок согласования,.третий триггер, формирователь стробирукнцих им- nyjibco, дифференциатор, вход-которого является входной пшной, а выход соединен с входами буферного усилителя и аналогового инвертора.

45

50

динен с выходом второго элемента И, второй вход третьего элемента И объединен с-первым входом второго элемента ШШ и соединен с выходом второго селектора фронтов вход которого подключен к выходу инвертора, второй вход четвертого элемента И объединен с вторым входом второго элемента ИЛИ и подключен к выходу первого селект ра фронтов.

выходы которых подключены к первым входам соответственно первого и второго устройств выборки и хранения, выходы которых подключены соответственно к первому и второму входу блока согласования, выход которого подключен к входу аналого-цифрового преобразователя, вторые входы устройства выборки и хранения объединены и подключены к выходу формирователя стробирующих импульсов вход которого соединен с выходом первого элемента И, второй вход которого объединен с вторым входом второго триггера, входом второго элемента задержки и подключен к выходу второго элемента ИЛИ, выход второго элемента задержки соединен с вторым входом первого триггера, первый вход третьего триггера объединен с первым входом первого триггера, второй вход объединен с третьими входами устройств выборки и хранения и соединен с выходом третьего элемента задержки, вход которого объединен с управляющим входом сдвигового регистра и соединен с четвертым выходом генератора образцовых частот, причем первые входы третьего и четвертого элементов И объединены и подключены к выходу третьего триггера, а выходы соединены с соответствующими входами шифратора, выходы которого через счетчик фаз подключены соответственно к первой группе информационных входов сдвигового регистра, вторая группа информационных входов которого подключена к соответствующим выходам аналого-цифрового преобразова

динен с выходом второго элемента И, второй вход третьего элемента И объединен с-первым входом второго элемента ШШ и соединен с выходом второго селектора фронтов вход которого подключен к выходу инвертора, второй вход четвертого элемента И объединен с вторым входом второго элемента ИЛИ и подключен к выходу первого селекто ра фронтов.

f™Jeta

Ului.t

Редактор Л.Повхан

Заказ 1968/59Тираж 816

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Составитель В.Солодова

Техред;В,Кадар Корректор М.Самборская

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Устройство для сжатия информации | 1986 |

|

SU1336080A1 |

| ИЗМЕРИТЕЛЬ СПЕКТРАЛЬНЫХ ПАРАМЕТРОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2080608C1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1985 |

|

SU1339892A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1361615A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Устройство для регистрации информации | 1988 |

|

SU1589315A1 |

| Устройство для контроля канала связи | 1987 |

|

SU1478351A1 |

| Устройство для оценки характеристик узкополосного случайного процесса | 1983 |

|

SU1117650A1 |

Изобретение относится к импульсной технике, в частности к устройствам аналого-цифрового преобразования узкополосных сигналов, Цель изобретения - повышение точности преобразования за счет введения в устройство, содержащее компаратор, делитель напряжения на резисторах, первый селектор фронтов, реверсивный счетчик,регистр памяти, цифроаналоговый преобразователь, регистр сдвига, инвертор, фильтр-интеграторj первый и второй триггеры, ключи, первый и второй элементы И, счетчик фаз, первьдй элемент задержки, первый и второй элементы ИЛИ, генератор образцовьк частот,второго селектора фронтов, второго и третьего элементов задержки, дифференциатора, буферного усилителя, аналогового инвертора, двух устройств выборки-хранения, блока согласования, осуществлякяцего пропускание сигнала на аналого-цифровой преобразователь только с того устройства выборки и хранения, в котором зафиксировано положительное напряжение формирователя стробирующих импульсов, шифратора, третьего и четвертого элементов И, второго и третьего элементов задерж- S ки. 2 ил. (Л 4

| Аналого-цифровой преобразователь узкополосных сигналов | 1981 |

|

SU999157A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-15—Публикация

1984-05-07—Подача