(54) ПРИЕМНИК ДВОИЧНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU919139A1 |

| СПОСОБ ПРИЕМА-ПЕРЕДАЧИ ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ И СИСТЕМА ПРИЕМА-ПЕРЕДАЧИ ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 2003 |

|

RU2255425C1 |

| МНОГОФУНКЦИОНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДАННЫХ | 2016 |

|

RU2609128C1 |

| СПОСОБ ПЕРЕДАЧИ КОМАНД УПРАВЛЕНИЯ МЕЖДУ ОБЪЕКТАМИ, РАЗНЕСЕННЫМИ В ПРОСТРАНСТВЕ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2099887C1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ В ПАУЗАХ РЕЧЕВЫХ СИГНАЛОВ | 1993 |

|

RU2054805C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| УСТРОЙСТВО ПРИЕМА КОМАНД УПРАВЛЕНИЯ | 2002 |

|

RU2237287C2 |

| СПОСОБ И УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ВРЕМЕНИ РАСПРОСТРАНЕНИЯ АКУСТИЧЕСКОГО СИГНАЛА МЕЖДУ ПОДВОДНЫМИ ОБЪЕКТАМИ | 2020 |

|

RU2759492C1 |

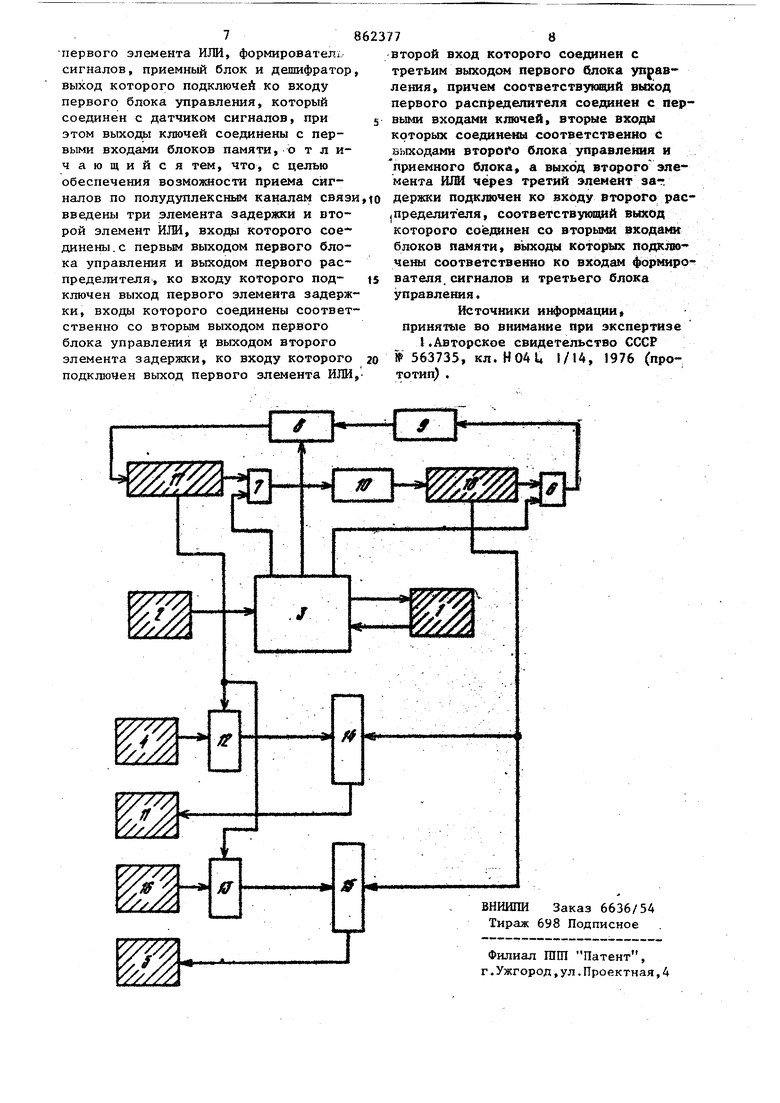

Изобретение относится к технике передачи дискретных данных и может использоваться в аппаратуре передачи дискретной информации, использующ для обеспечения требуемой верности передаваемой информации избыточный блочный код в режиме обнаружения или обнаружения и частичного исправления ошибок и решающую обратную связь. Известен приемник двоичных сигналов, содержаний первый распределитель, два ключа, три блока управления, два блока памяти, второй распре делитель, выход которого подключен к первому входу первого элемента ИЛИ формирователь сигналов, приемный блок и дешифратор, выход которого по ключен ко входу первого блока управления, который соединен с датчиком сигналов, при этом выходы ключей сое динены с первыми входами блоков памя ти ГО . . , Однако известный приемник не позволяет принимать сигналы по полудуплексным каналам связи. Цель изобретения - обеспечение возможности приема сигналов по полудуплексным каналам связи. Для этого в приемник двоичных сигналов, содержащий первый распределитель, два KJB04a, три блока управления, два блока памяти, второй распределитель, вьпсод которого подключен к первому входу первого, элемента ИЛИ, формирователь сигналов, приемный блок и дешифратор, выход которого подключен ко входу первого блока управления, который соединен с датчиком сигналов, а выхода| ключей соединены с первыми входами блоков памяти, введены три элемента задержки и второй элемент ИЛИ, входы которого соединены с первым выходом первого блока управления и выходом первого распределителя, ко входу которого подключен выход первого элемента задержки, входы которого соединены со ответственно со вторьм выходом пернего блока управления и выходом второго элемента задержки, ко входу которого подключен выход первого элемента ИЛИ, второй вход которого соединен с третьим выходом первого блока управления. Соответствующий выход первого распределителя соединен с первыми входами ключей, вторые входы которых соединены соответственно с выходами второго блока управ ления и. приемного блока. Выход второ го элемента ИЛИ через третий элемент задержки подключен ко входу второго распределителя, соответствующий выход которого соединен со вторыми вхо дами блоков памяти, выходы которых подключены соответственно ко входам формирователя сигналов и третьего блока управления. На чертеже представлена структурная электрическая схема предложенного приемника. Приемник двоичных сигналов содержит датчик сигналов 1, дешифратор 2, первый, второй и третий блоки,управления 3,4,5 соответственно, первый и второй элементы ИЛИ 6,7 соответствен но, первый, второй и третий элементы задержки 8,9,10, формирователь П сигналов, два ключа 12,13,два блока памяти 14,15, приемный блок 16, первый и второй распределители 17,18 соответственно. Приемник работает следующим образом. Передача и прием кодовых комбинаций по полудуплексным каналам связи осуществляется так же, как и по дуплексным каналам связи, только время на передачу информации и служебных команд предоставляется поочередно сначала в одну сторону, потом в другую, и при этом также изменяется режим вхождения в связь. Вхождение в связь на вызывающей станции начинается с передачи команды Начало работы. Эта команда должна включать синхропоследовйтельност и ф$зирукядую последовательность (а также адрес вызываемой станции и свой адрес, если станции работают в сети). Команда Начало работы формирует ся в датчике сигналов 1. После передачи этой команды в первом блоке управлет1Я 3 делается отме ка о начале измерения задержки, учи74тьшающей распространение сигнала в прямом и обратном каналах связи. На вызываемой станции после приема команды Начало работы с выхода дешифратора 2 на первый блок управления 3 выдается сигнал для переключения станции в режим передачи. Причем сигнал на переключение с выхода первого блока управления 3 выдается с задержкой относительно входного сигнала, равной ёмкости линии задержки на переключение (хотя включение передатчика радиостанции может произойти и ранее),а разрешение на передачу с .выхода датчика сигналов 1 команды Начало работы вьщается ближайшим тактовым импульсом второго распределителя 18. На вызываемой станции после приема команды НаЧало работы будет установлена фаза по импульсу и фаза по циклу распределителя 17, а также в блоке управл,ения 3 будет сделана отметка о начале отсчета задержки команды при передаче ее по прямому и обратному каналам связи. Если станции работают .в сети, то передатчики других станций сети, приняв команду Начало работы с чужим адресом, блокируются. На вызываемой станции после приема команды Начало работы кроме установления фазы по импульсу и по циклу в блоке управления 3 будет определено время, соответствующее задержке сигнала во время его передачи по прямому и обратному каналам связи. Это время будет определено из общей задержки, определяемой в блоке управления 3 с момента окончания передачи команды Начало работы до момента окончания приема этой команды, путем вычитания из нее задержки на переключение и времени приема команды Начало работы. После приема команды Начало работы с выхода дешифратора 2 выдается сигнал на блок управления 3, с выхода которого вьщается сигнал для установки емкости элемента задержки 8, а затем с задержкой, равной емкости второго элемента задержки , запускается датчик сигналов И в канал связи выдается команда Готов к работе. На вызьшаемой станции после приема команды Готов к работе в блоке управления 3 определяется и сигналом с его выхода устанавливается емкость гпервого элемента задержки Я, затем с задержкой, определяемой вторым элементом задержкиj ближайшим тактовым импульсом второго распределителя запускается датчик сигналов 1 и вьщает в канал связи команду Готов к работе. Команда Готов к работе содержит в себе сведения о длине цикла второго распределителя в зависимости от того, будет ли от станции передаваться информация или только служебные сигналы Запрос или Подтверждение. В зависимости от этого будет устанавливаться длина цикла первого распределителя противоположной станции. Вызывающая станция после приема командь Готов к работе передает в канал связи первый пакет из ко довых комбинаций; (. соответствует .использованию всех -имеющихся в блоках памяти регистров). После пе редачи, пакета из (, кодовых комбинаций станция переключается в режим приема, но разрешение на прием выдается с задержкой по отношению к концу передачи, равной емкости всех элементов задержки. На вызывающей станции осуществляется прием h сигналов обратной связи, затем вызывающая станция снова переключается в режим передачи очередного пакета из t rAcivtc кодовых комбинаций. При этом в очередном пакете на местах, соответствующих приему сигнала Подтверждение, так же, как и при передаче по дуплексному каналу связи, передается очередная кодовая комбинация соответ ствующей последовательности, а на местах соответствующих приему сигнала Запрос, повторно передается, комбинация данной подпоследовательности, переданная в предыдущем пакете. В процессе обмена информацией во время приема очередного пакета в бл:ж памяти 14 через ключ 12 поочере но записываются данные с выхода блока управления 4 о наличии или отсутcf ВИИ ошибок в каждой из Н|лау:.с приня тых кодовых комбинаций, а в блок памяти 15 через ключ 13 - данные с выхода приемного блока 16. Во время передачи данные этих блоков памяти поочередно считываются в формирователь 11 сигналов и в блок управления 5 для передачи в каждой подпоследова тельности или следующей кодовой комбинации из соответствующего регистра блока памяти или запрашиваемой комбинации из повторителя.j В дуплексном режиме первый и второй распределители работают непрерывно и обеспечивают поочередную запись кодовых комбинаций в соответствующие регистры блока памяти и поочередное считьшание кодовых комбинаций из соответствующих регистров другого блока памяти. В полудуплексном режиме распределители выполняют те же функции, но из-за поочередности работы необходимо обеспечить своевременный запуск и остановку этих распределителей. С этой целью в процессе обмена данными распределители запускаются поочередно друг от друга с учетом задержек запуска, определяемых включенными между ними линиями задержки. Емкость второго и третьего элементов задержки устанавливается такой, чтобы время задержки сигнала в линии было не меньше мак- симально возможного времени переключения радиостанции с приема на передачу (или с передачи на прием). В этом случае колебания времени переключения станции не изменяют фазу передаваемого сигнала при переключении по сравнению с фазой сигнала, передаваемого до переключения. В том случае, если время задержки сигнала второго и третьего элементов задержки не кратно длительности передачи кодо1вой комбинации при переключении станции с приема на передачу сигна/IOM с выхода линии задержки, необходимо устанавливать фазу второго распределителя, а при переключении станции с передачи на прием - фазу первого распределителя.Сдвиг фазы распределителей в этом случае производится на заранее известную постоянную величину, так что оба распределителя, обменивающихся информацией станций, остаются в фазе. Таким образом обеспечивается прием сигналов по полудзшлексным каналам связи. Формула изобретения Приемник двоичных сигналов, содержащий первый распределитель, два ключа, три блока управления, два блока Памяти, второй распределитель, В1.гход оторого подключен к первому входу

Авторы

Даты

1981-09-07—Публикация

1979-10-30—Подача