(54) УСТРОЙСТВО ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка временной задержки импульсов | 1980 |

|

SU945967A1 |

| Линия задержки | 1981 |

|

SU1046911A1 |

| Логический вентиль | 1980 |

|

SU940308A1 |

| Распределитель на транзисторах | 1973 |

|

SU504302A1 |

| Устройство электропитания постоянного напряжения для радиоэлектронного комплекса | 1977 |

|

SU651330A1 |

| РАСПРЕДЕЛИТЕЛЬ—СЧЕТЧИК | 1972 |

|

SU332577A1 |

| Релейный коммутатор | 1980 |

|

SU921111A1 |

| Стабилизированный источник электропитания постоянного напряжения | 1979 |

|

SU769514A1 |

| Устройство для управления шаговым двигателем | 1984 |

|

SU1293701A1 |

| Коммутатор импульсных сигналов | 1980 |

|

SU940302A1 |

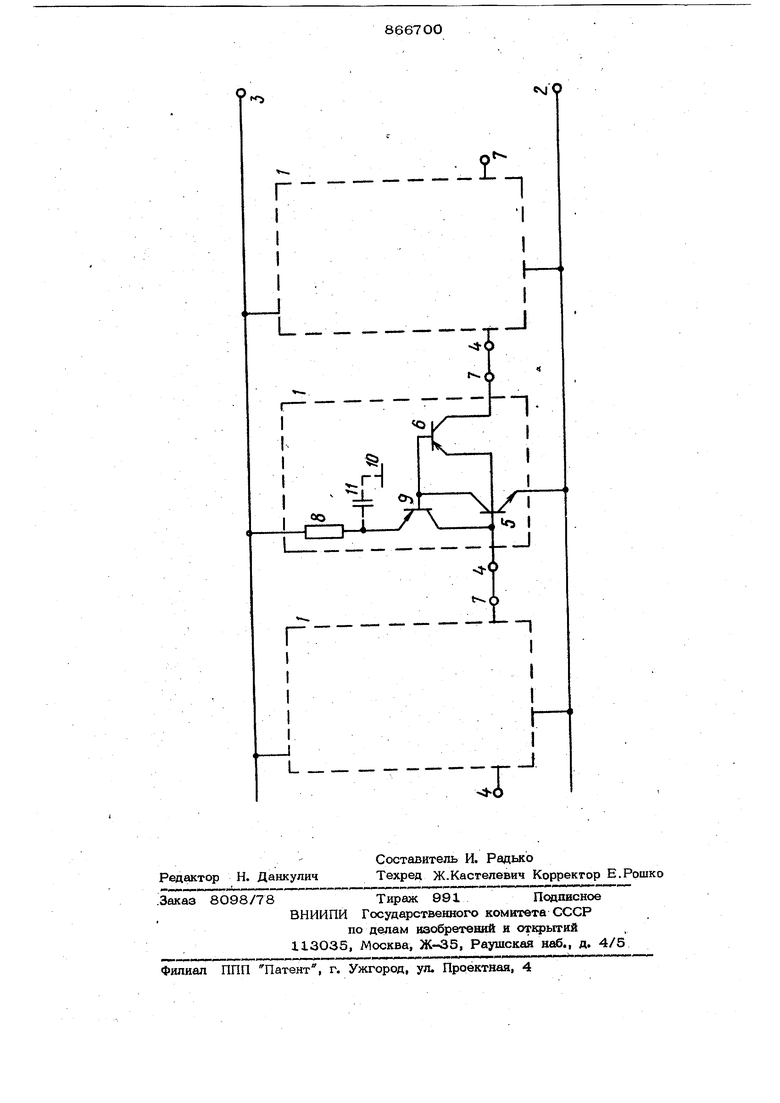

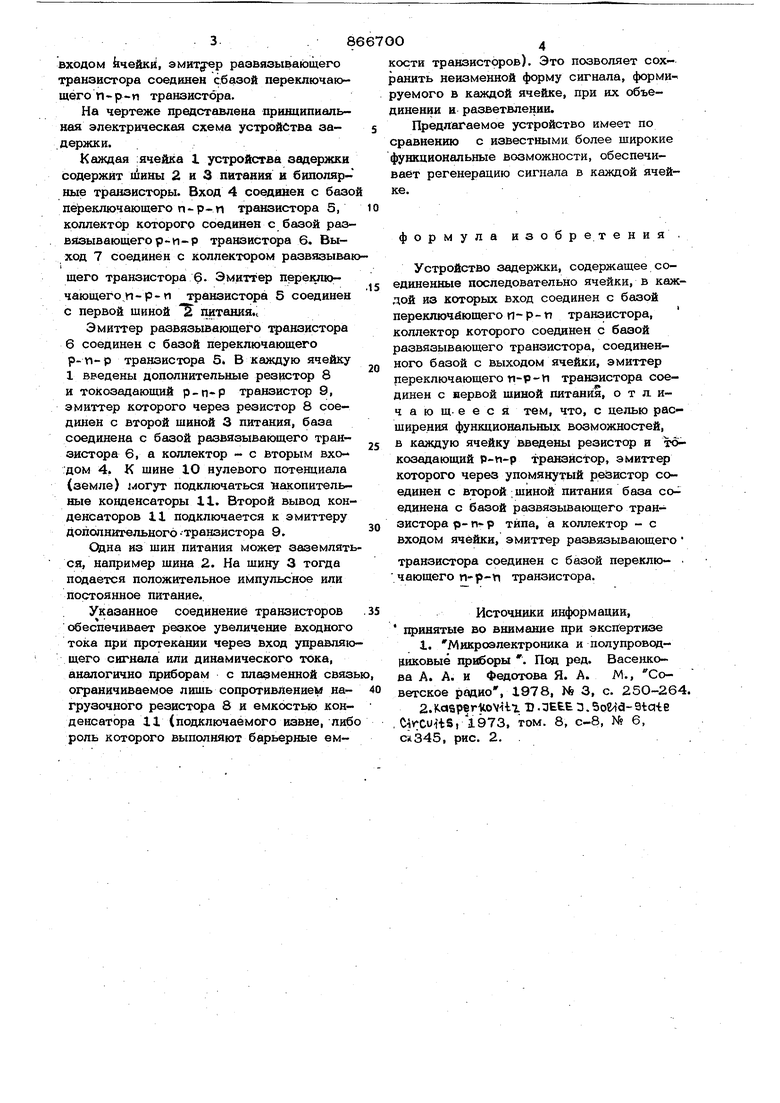

Изобретение относится к импульсной технике и может найти применение при 1фоект1фовании и производстве линий задержки незатухающих двоичных сигналов п(х:тоянной формы, используемых, например, в дешифраторах, кодирующих устройст вах, приемной и передающей радиоаппаратуре. Известны линии задержки на биполяргных транзисторах, которые имеют просты ячейки (соответствующие одному разряду) например, содержащие лишь один транзистор ti. . Опнако такие линии задержки имеют низкую помехоустойчивость и невысокие функциональные возможности вследствие изменения ффмы сигнала при последовательном, соединении ячеек и особенно при разветвлении и объединении задерживаемо .го сигнала. Известы устройства задержки, со держаише соединенны ТГоследовательно ячейки, каждая из которьрс выполнена на пе реключающем и развязывающем гран зисторах Г2}. ,, Нед остатками известнойлшшв ааа. кк являются отсутствие регенераоив сигнала и. невысокие функциональные возможности. Цель изобретения - расширение функциональньи возможностей линии задержки. , Для достижения указанной цели в устройство, содержащее соединенные последовательно ячейки, в каждой из которых вход соедвшен с базой переключающего И - р- п трананстора, коолектор которого соединен с базой развязывающего транзистора, соединенного базой с выходом ячейки, эмиттер переключающего транзистора соединен с первой щиной питания, вкаждую ячейку введены резистор и токозадающий р - и-р резистор,: эмитг тер которого через упомянутый резистор соединен с второй шиной питания, база соединена с базой развязывающего тран зисторар-п-0 типа, а коллектор - с входом k4.euKfi, развязывающего транзистора соединен сбазой переключающего п-р-п транзистора. На чертеже представлена принципиальная электрическая схема устройства за.держки. Каждая :ячейка 1 устройства задержки содержит шины 2 и 3 питания и биполярные транзисторы. Вход 4 соединен с базо переключающего трешзистора 5, коллектор которого соединен с базой развязывающего р- и- р транзистора 6. Выход 7 соединен с коллектором развязыва щего транзистора 6. Эмиттер переключающего ,п-р-п транзистора 5 соединен с первой ЩИНОЁ питания.1 Эмиттер развязывающего транзистора 6 соединен с базой переключающего р-п-р транзистора 5 В каждую ячейку 1 введены дополнительные резистор 8 и токозадающий р-п-Р транзистсф 9, эмиттер которого через резистор 8 соединен с второй щиной 3 питания, база соединена с базой развязывающего транзистора 6, а коллектор - с вторым входом 4. К щине 1О нулевого потенциала (земле) jHoryT подключаться накопительные конденсаторы И. Второй вывод конденсаторов Ц подключается к эмиттеру дополнительного-транзистора 9. Одна из щин питания может заземлять ся, например щина 2. На шину 3 тогда подается положительное импульсное или постоянное питание. Указанное соединение транзисторов обеспечивает резкое увеличение входного тока при протекании через вход управляю щего сигнала или динамического тока, аналогично приборам с плазменной связ ограничиваемое лишь сопротивлением нагрузочного резистора 8 и емкостью конденсатора Ц (подключаемого извне, либ роль которого выполняют барьерные емости транзисторов). Это позволяет соханить неизменной форму сигнала, формиуемого в каждой ячейке, при их объеинении и разветвлении. Предлагаемое устройство имеет по сравнению с известными более широкие функциональные возможности, обеспечивает регенерацию сигнала в каждой ячейке. формула изобр е т е н и я . Устройство задержки, содержащее соединенные последовательно ячейки, в каждой из которых вход соединен с базой переключающего п-р-п транзистора, коллектор которого соединен с базой развязывающего транзистора, соединенного базой с выходом ячейки, эмиттер переключающего n-P-tt транзистора соединен с первой щиной питания, о т я ичающ-ееся тем, что, с целью расширения функциональных возможностей, в каждую ячейку введены резистор и токозадающий Р-п-р транзистор, эмиттер которого через упомянутый резистор соединен с второй;шиной питания база соединена с базой развязывающего транзистора р- tv- р типа, а коллектор - с входом ячейки, эмиттер развязывающего транзистора соединен с базой переклю- . чающего п-р-ш транзистора. Источники информации, принятые во внимание при экспертизе 1. Микроэлектроника и полупровод(1иковые приборы . Под ред. Васенкова А. А. и Федотова Я. А. М., Советское радио , 1978, № 3, с. 250-264. 2.K-asperllOVilT. D. ЗЕЕЕ 3. ЗоМа- Staie , Circuits,l973, том. 8, с-8, № 6, , рис. 2,,

Г

evjp

П

I 7

Г

L

o

ID I

J

П

Авторы

Даты

1981-09-23—Публикация

1979-12-26—Подача