(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля качества канала связи | 1988 |

|

SU1543554A2 |

| Устройство для контроля качества каналаСВязи | 1979 |

|

SU836801A2 |

| Устройство для контроля качества канала связи | 1987 |

|

SU1418918A2 |

| Устройство для контроля качества канала связи | 1979 |

|

SU866759A2 |

| Устройство для контроля качества канала связи | 1982 |

|

SU1078641A1 |

| Анализатор качества канала связи | 1983 |

|

SU1088139A1 |

| Устройство приема контрольной информации | 1989 |

|

SU1672581A1 |

| Устройство для контроля качестваКАНАлА СВязи | 1979 |

|

SU815928A2 |

| Устройство для оценки состояния канала связи | 1986 |

|

SU1438012A1 |

| Преобразователь перемещения в код | 1987 |

|

SU1438001A1 |

Изобретение относится к радиотехнике и может использоваться в системах передачи данных. По основному.авт.св. 634463 известно устройство для контроля ка честна канала связи, содержащее ко паратор, первый вход которого соедин с выходом интегратора, второй вход с первым выходом хронизатора, счетчик информационных символов, выход которого подключен к первым входам первого и второго элементов сравнения соответственно, элемент задержк и элемент ИЛИ, при этом второй выхо хронизатора подключен к вторым входам первого и второго элементов сра нения, выход каждого из которых подключен к соответствующим входам элемента ИЛИ и входу элемента задер ки, выход которого подключен к первому входу счетчика информационных символов, второй вход которого соединен с выходом компаратора. Однако в известном устройстве не достаточная точность контроля. Цель изобретения - повышение точ ности контроля. Для достижения поставленной цели в устройство для контроля качества канала связи, содержащее компаратор первый вход которого соединен с выходом интегратора, второй вход с первым выходом хронизатора, счетчик информационных символов, выход которого подключен к первым входам первого и второго элементов сравнения соответственно, элемент задержки и элемент ИЛИ, при этом второй выход хронизатора подключен к вторым входам первого и второго элементов сравнения, выход каждого из которых подключен к соответствующим входам элемента ИЛИ и входу элемента задержки, выход которого подключен к первому входу счетчика информационных символов, второй вход которого соединен с выходом компаратора, введен блок анализа временных искажений, содержащий первый пороговый блок и последовательно соединенные второй пороговый блок, инвертор, элемент И, счетчик ошибок и блок сравнения, причем первые входы пороговых блоков объединены и соединены с выходом интегратора, вторые входы пороговых блоков объединены и соединены с первым выходом хронизатора,второй выход которого соединен с другим входом блока сравнения, выход которого соединен с дополнительным входом элемента ИЛИ, выход элемента задержки соединен с другим входом счетчика ошибок, а выход первого порогового блока соединен с другим входом элемента И.

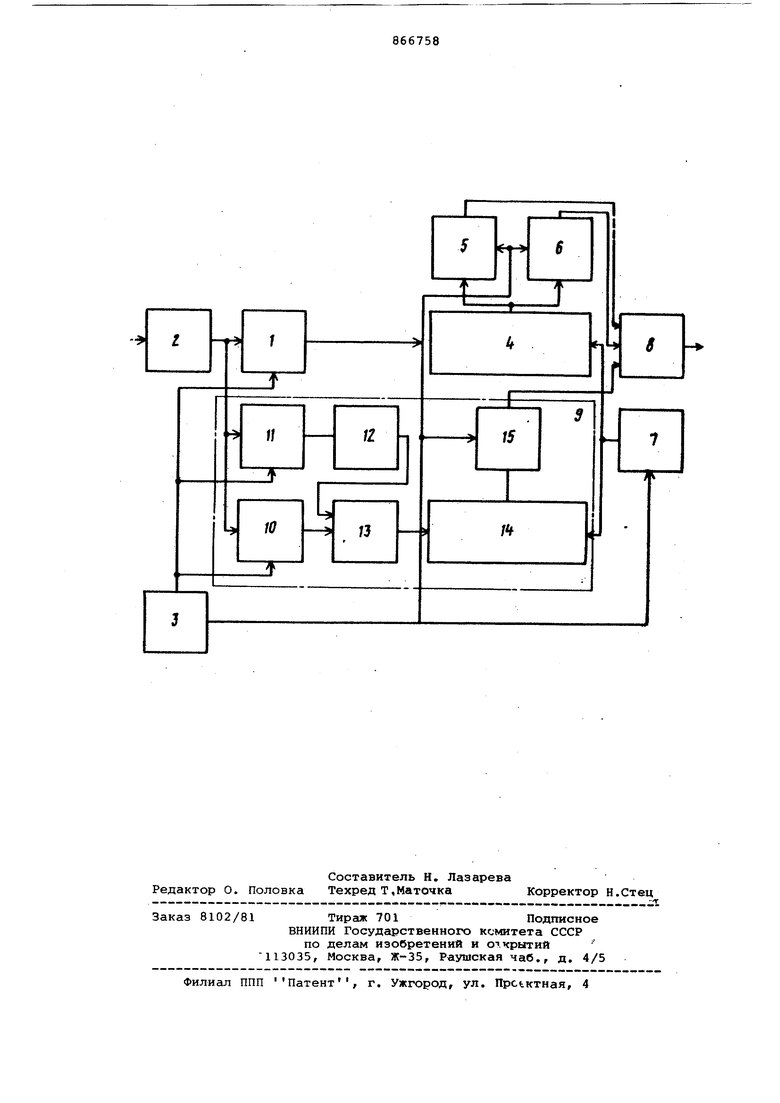

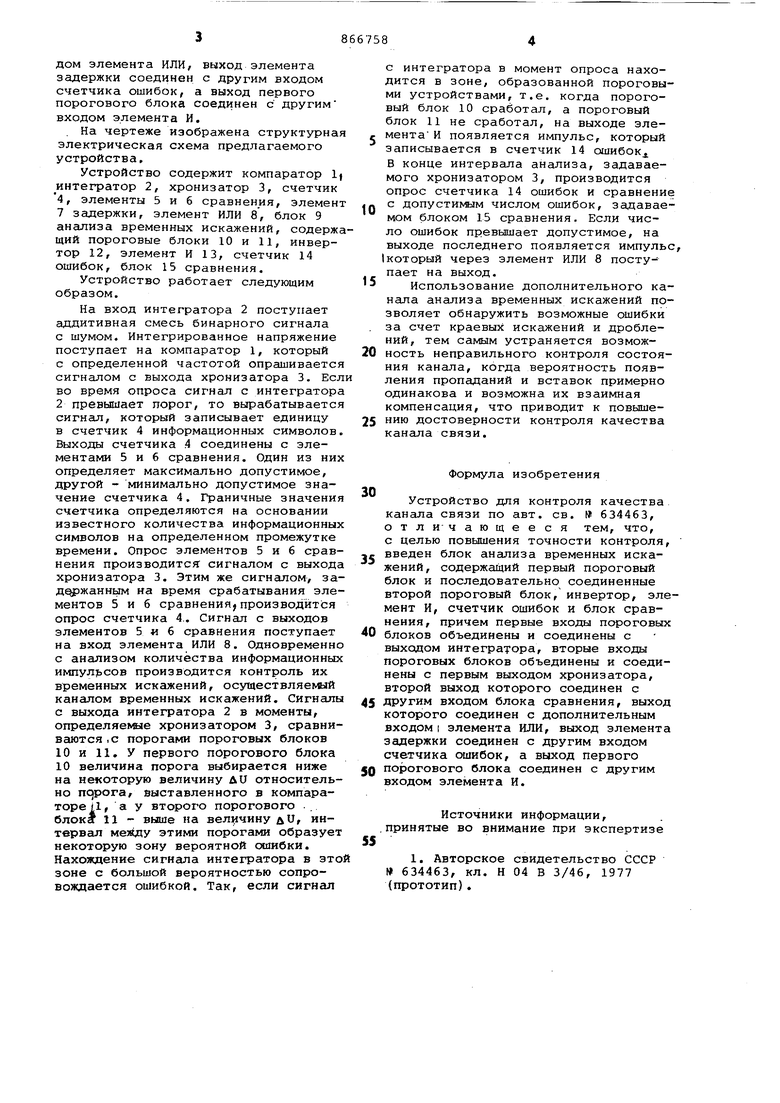

. На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит компаратор If интегратор 2, хронизатор 3, счетчик 4, элементы 5 и 6 сравнения, элемент 7 задержки, элемент ИЛИ 8, блок 9 анализа временных искажений, содержащий пороговые блоки 10 и 11, инвертор 12, элемент И 13, счетчик 14 ошибок, блок 15 сравнения.

Устройство работает следующим образом.

На вход интегратора 2 поступает аддитивная смесь бинарного сигнала с шумом. Интегрированное напряжение поступает на компаратор 1, который с определенной частотой опрашивается сигналом с выхода хронизатора 3. Есл во время опроса сигнал с интегратора 2 превышает порог, то вырабатывается сигнал, который записывает единицу в счетчик 4 информационных символов. Выходы счетчика 4 соединены с элементами 5 и 6 сравнения. Один из них определяет максимально допустимое, другой - минимально допустимое значение счетчика 4. Граничные значения счетчика определяются на основании известного количества информационных символов на определенном промежутке времени. Опрос элементов 5 и 6 сравнения производится сигналом с выхода хронизатора 3. Этим же сигналом, зад жанньгм на время срабатывания элементов 5 и б сравнения,производится опрос счетчика 4.. Сигнал с выходов элементов 5 и 6 сравнения поступает на вход элемента ИЛИ 8. Одновременно с анализом количества информационных импульсов производится контроль их временных искажений, ocyщecтвляe ый каналом временных искажений. Сигналы с выхода интегратора 2 в моменты, определяелеле хронизатором 3, сравниВсоотся iC порогами пороговых блоков 10 и 11. У первого порогового блока 10 величина порога выбирается ниже на некоторую величину ли относительно nqpora, выставленного в компараторе, а у второго порогового . блокзг 11 - выше на величину ди, интервал мезйду этими порогами образует некоторую зону вероятной сяяибки. Нахоящение сигнала интегратора в это зоне с большой вероятностью сопровождается ошибкой. Так, если сигнал

с интегратора в момент опроса находится в зоне, образованной пороговыми устройствами, т.е. когда пороговый блок 10 сработал, а пороговый блок 11 не сработал, на выходе элее мента И появляется импульс, который записывается в счетчик 14 ошибок, В конце интервала анализа, задаваемого хронизатором 3, производится опрос счетчика 14 ошибок и сравнение

Q с допусти им числом ошибок, задаваемом блоком 15 сравнения. Если число ошибок превышает допустимое, на выходе последнего появляется импульс, Iкоторый через элемент ИЛИ 8 поступает на выход.

5 Использование дополнительного канала анализа временных искажений позволяет обнаружить возможные ошибки за счет краевых искажений и дроблений, тем самым устраняется возможность неправильного контроля состояния канала, когда вероятность появления пропаданий и вставок примерно одинакова и возможна их взаимная компенсация, что приводит к повышению достоверности контроля качества кансша связи.

Формула изобретения

Устройство для контроля качества канала связи по авт. св. № 634463, отл и-чающееся тем, что, с целью повышения точности контроля,

введен блок анализа временных искажений, содержащий первый пороговый блок и последовательно соединенные второй пороговый блок, инвертор, элемент И, счетчик ошибок и блок сравнения, причем первые входы пороговых

блоков объединены и соединены с выходом интегратора, вторые входы пороговых блоков объединены и соединены с первым выходом хронизатора, второй выход которого соединен с

другим входом блока сравнения, выход которого соединен с дополнительным входом I элемента ИЛИ, выход элемента задержки соединен с другим входом счетчика ошибок, а выход первого

порогового блока соединен с другим входом элемента И.

Источники информации, .принятые во внимание при экспертизе

Авторы

Даты

1981-09-23—Публикация

1979-12-12—Подача