Изобретение относится к электросвязи и может использоваться в системах передачи данных с кодами с постоянным весом и для их контроля.

Цель изобретения - повышение точности приема.

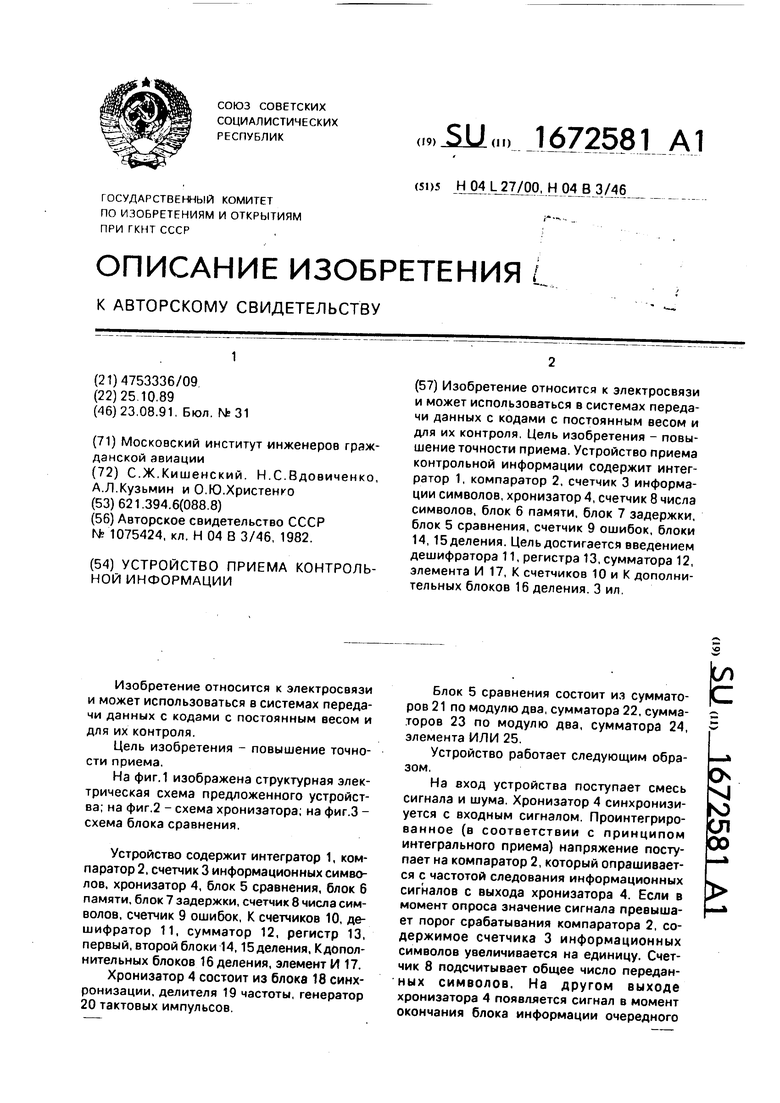

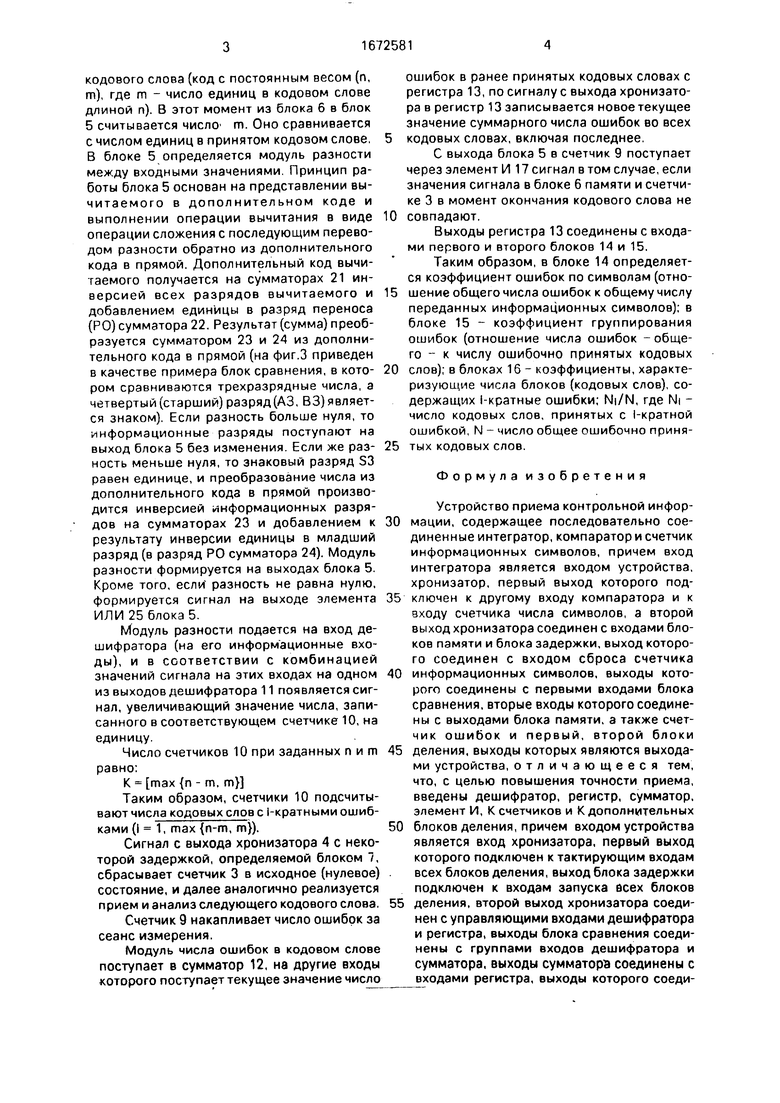

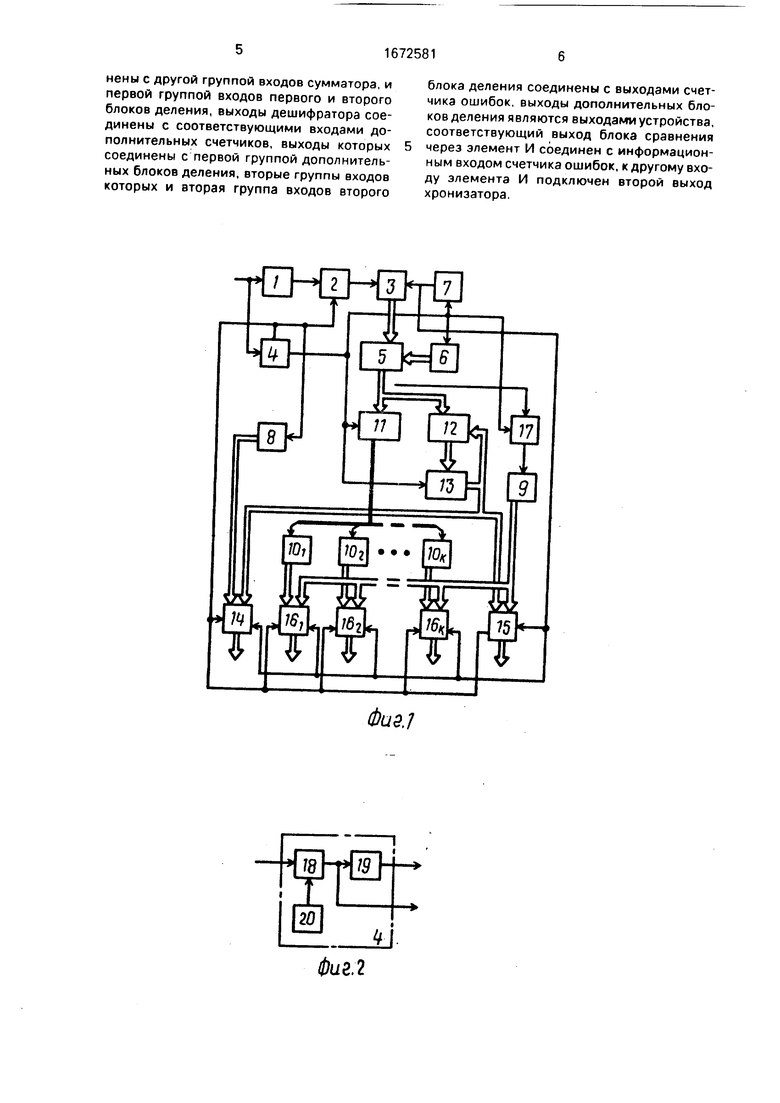

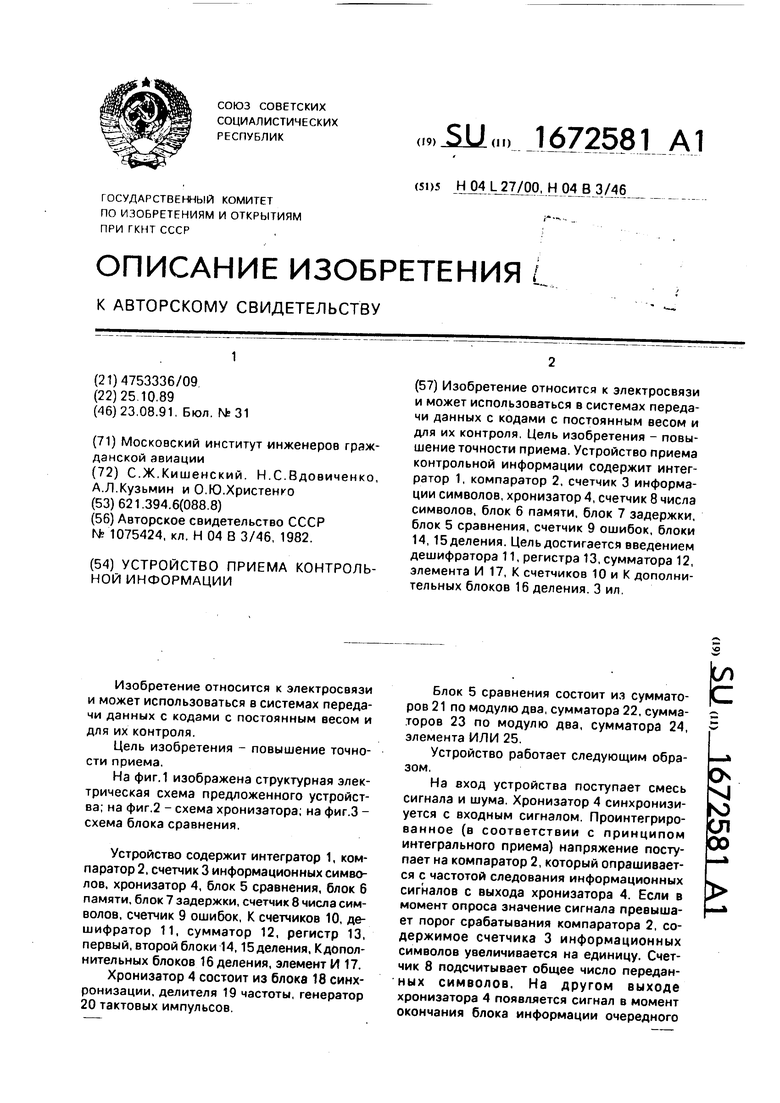

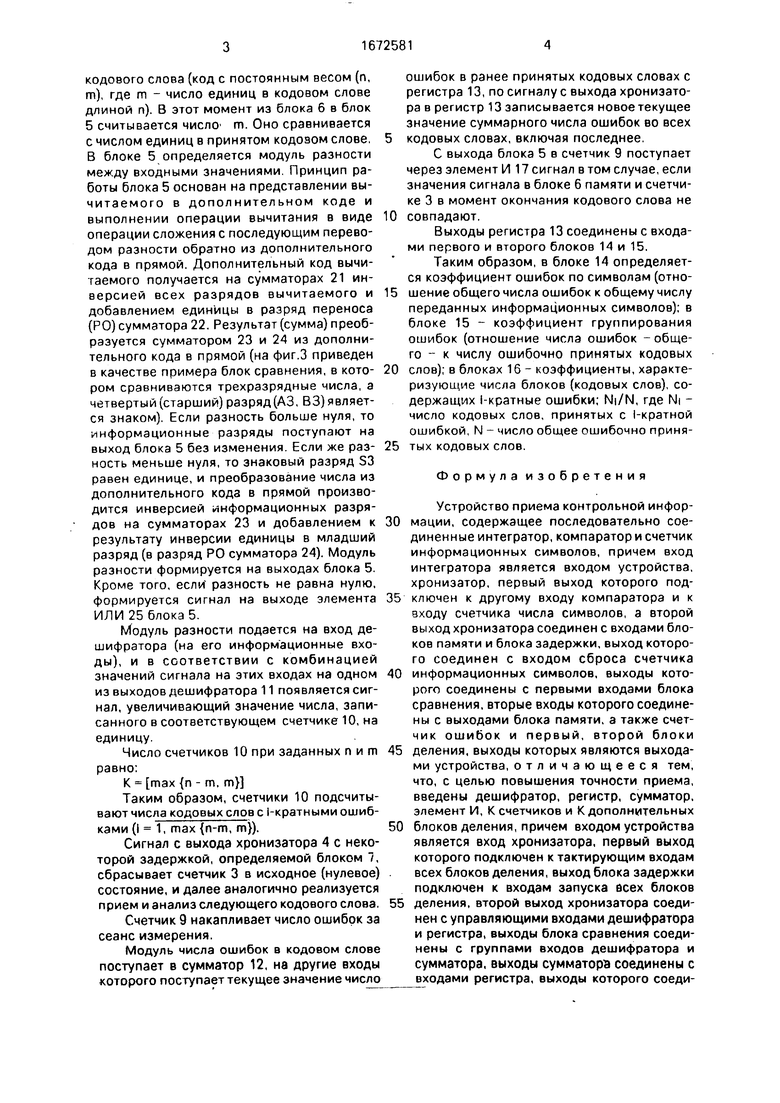

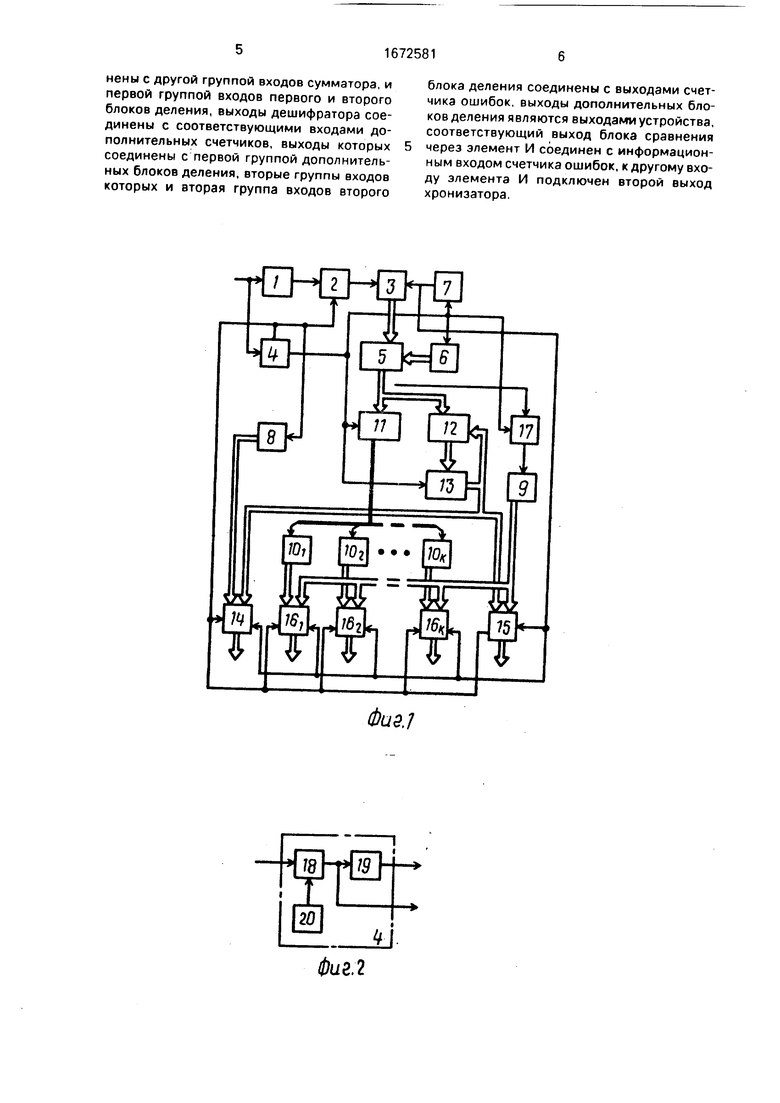

На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг.2 - схема хронизатора; на фиг.З - схема блока сравнения.

Устройство содержит интегратор 1, компаратор 2, счетчик 3 информационных символов, хронизатор 4, блок 5 сравнения, блок 6 памяти, блок 7 задержки, счетчик 8 числа символов, счетчик 9 ошибок, К счетчиков 10, дешифратор 11, сумматор 12, регистр 13, первый, второй блоки 14,15 деления, Кдопол- нительных блоков 16 деления, элемент И 17.

Хронизатор 4 состоит из блока 16 синхронизации, делителя 19 частоты, генератор 20 тактовых импульсов.

Блок 5 сравнения состоит из сумматоров 21 по модулю два, сумматора 22, сумматоров 23 по модулю два, сумматора 24, элемента ИЛИ 25.

Устройство работает следующим образом.

На вход устройства поступает смесь сигнала и шума. Хронизатор 4 синхронизи- уется с входным сигналом. Проинтегрированное (в соответствии с принципом интегрального приема) напряжение поступает на компаратор 2, который опрашивается с частотой следования информационных сигналов с выхода хронизатора 4. Если в момент опроса значение сигнала превышает порог срабатывания компаратора 2, содержимое счетчика 3 информационных символов увеличивается на единицу. Счетчик 8 подсчитывает общее число переданных символов. На другом выходе хронизатора 4 появляется сигнал в момент окончания блока информации очередного

fe

кодового слова (код с постоянным весом (п, т), где т - число единиц в кодовом слове длиной п). В этот момент из блока 6 в блок 5 считывается число т. Оно сравнивается с числом единиц в принятом кодовом слове, В блоке 5 определяется модуль разности между входными значениями. Принцип работы блока 5 основан на представлении вычитаемого в дополнительном коде и выполнении операции вычитания в виде операции сложения с последующим переводом разности обратно из дополнительного кода в прямой. Дополнительный код вычитаемого получается на сумматорах 21 инверсией всех разрядов вычитаемого и добавлением единицы в разряд переноса (РО) сумматора 22, Результат (сумма) преобразуется сумматором 23 и 24 из дополнительного кода в прямой (на фиг.З приведен в качестве примера блок сравнения, в котором сравниваются трехразрядные числа, а четвертый (старший) разряд (A3, ВЗ) является знаком). Если разность больше нуля, то информационные разряды поступают на выход блока 5 без изменения. Если же разность меньше нуля, то знаковый разряд S3 равен единице, и преобразование числа из дополнительного кода в прямой производится инверсией информационных разрядов на сумматорах 23 и добавлением к результату инверсии единицы в младший разряд (в разряд РО сумматора 24). Модуль разности формируется на выходах блока 5. Кроме того, если разность не равна нулю, формируется сигнал на выходе элемента ИЛИ 25 блока 5.

Модуль разности подается на вход дешифратора (на его информационные входы), и в соответствии с комбинацией значений сигнала на этих входах на одном из выходов дешифратора 11 появляется сигнал, увеличивающий значение числа, записанного в соответствующем счетчике 10, на единицу.

Число счетчиков 10 при заданных пит равно:

К max {n - т, т}

Таким образом, счетчики 10 подсчитывают числа кодовых слов с 1-кратными ошибками (1 1, max {n-m, m}).

Сигнал с выхода хронизатора 4 с некоторой задержкой, определяемой блоком 1, сбрасывает счетчик 3 в исходное (нулевое) состояние, и далее аналогично реализуется прием и анализ следующего кодового слова. Счетчик 9 накапливает число ошибок за сеанс измерения.

Модуль числа ошибок в кодовом слове поступает в сумматор 12, на другие входы которого поступает текущее значение число

ошибок в ранее принятых кодовых словах с регистра 13, по сигналу с выхода хронизатора в регистр 13 записывается новое текущее значение суммарного числа ошибок во всех

кодовых словах, включая последнее.

С выхода блока 5 в счетчик 9 поступает через элемент И 17 сигнал в том случае, если значения сигнала в блоке 6 памяти и счетчике 3 в момент окончания кодового слова не

совпадают.

Выходы регистра 13 соединены с входами первого и второго блоков 14 и 15.

Таким образом, в блоке 14 определяется коэффициент ошибок по символам (отношение общего числа ошибок к общему числу переданных информационных символов); в блоке 15 - коэффициент группирования ошибок (отношение числа ошибок - общего - к числу ошибочно принятых кодовых

слов); в блоках 16 - коэффициенты, характеризующие числа блоков (кодовых слов), содержащих 1-кратные ошибки; Ni/N, где NI - число кодовых слов, принятых с 1-кратной ошибкой, N - число общее ошибочно принятых кодовых слов.

Формула изобретения

Устройство приема контрольной информации, содержащее последовательно соединенные интегратор, компаратор и счетчик информационных символов, причем вход интегратора является входом устройства, хронизатор, первый выход которого подключей к другому входу компаратора и к входу счетчика числа символов, а второй выход хронизатора соединен с входами блоков памяти и блока задержки, выход которого соединен с входом сброса счетчика

информационных символов, выходы которого соединены с первыми входами блока сравнения, вторые входы которого соединены с выходами блока памяти, а также счетчик ошибок и первый, второй блоки

деления, выходы которых являются выходами устройства, отличающееся тем, что, с целью повышения точности приема, введены дешифратор, регистр, сумматор, элемент И, К счетчиков и К дополнительных

0 блоков деления, причем входом устройства является вход хронизатора, первый выход которого подключен к тактирующим входам всех блоков деления, выход блока задержки подключен к входам запуска всех блоков

5 деления, второй выход хронизатора соединен с управляющими входами дешифратора и регистра, выходы блока сравнения соединены с группами входов дешифратора и сумматора, выходы сумматора соединены с входами регистра, выходы которого соединемы с другой группой входов сумматора, и первой группой входов первого и второго блоков деления, выходы дешифратора соединены с соответствующими входами дополнительных счетчиков, выходы которых соединены с первой группой дополнительных блоков деления, вторые группы входов которых и вторая группа входов второго

блока деления соединены с выходами счетчика ошибок, выходы дополнительных блоков деления являются выходами устройства, соответствующий выход блока сравнения через элемент И соединен с информационным входом счетчика ошибок, к другому входу элемента И подключен второй выход хронизатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Анализатор качества канала связи | 1983 |

|

SU1088139A1 |

| Декодер кодов Рида-Соломона | 1988 |

|

SU1690202A1 |

| Устройство для контроля качества канала связи | 1982 |

|

SU1078641A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Устройство для приема информации | 1988 |

|

SU1550562A1 |

| Устройство для приема дискретной информации | 1982 |

|

SU1030829A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАНАЛА СВЯЗИ | 2007 |

|

RU2352072C1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

Изобретение относится к электросвязи и может использоваться в системах передачи данных с кодами с постоянным весом и для их контроля. Цель изобретения - повышение точности приема. Устройство приема контрольной информации содержит интегратор 1, компаратор 2, счетчик 3 информации символов, хронизатор 4, счетчик 8 числа символов, блок 6 памяти, блок 7 задержки, блок 5 сравнения, счетчик 9 ошибок, блоки 14, 15 деления. Цель достигается введением дешифратора 11, регистра 13, сумматора 12, элемента И 17, K счетчиков 10 и K дополнительных блоков 16 деления. 3 ил.

фиг.2

Фиэ.1

Фие.з

| Устройство для контроля качества канала связи | 1982 |

|

SU1075424A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-08-23—Публикация

1989-10-25—Подача