(54) УСТРОЙСТВО ДИНАМИЧЕСКОГО ПРИОРИТЕТА Изоьретение относится к вычислительной технике и может быть использовано преимущественно в асинхронных многопроцессорных ЭВМ с общей памятью, общими внешними устройствами ил устройствами управления. Известно устройство переменного приоритетного обращения к блоку оперативной памяти в многопроцессорнс5й ЭВМ, содержащее узел управления, элементы И и ИЛИ, счетчик, дешифраторы, регистр приоритета 1. Основной недостаток данного устройства - низкое его быстродействие вследствие использования счетчика и дешифратора для определения приоритета абонента. Наиболее близким к предлагаемому является приоритетное устройство, содержащее регистры заявок и приоритета, счетчики, элементы И и ИЛИ, триггер управления и выходной регистр 2 . Недостаток устройства - низкое быстродействие, обусловленное применением генератора импульсов и суммирующего (вычитающего) счетчика дл выбора наиболее приоритетного сигнала на обслуживание. Цель изобретения - повышение быстродействия устройтсва. Поставленная цель достигается тем, что в устройство динамического приоритета, содержащее группу регистров приоритетов, регистр заявок, первую и вторую группы элементов И, четыре элемента ИЛИ, триггер, выходной регистр, группу счетчиков, причем информационные входы регистров приоритетов группы являются группой кодовых входов устройства, разрядные выходы регистров приоритетов группы соединены с первыми входами соответствующих элементовИ первой группы, выходы элементов И первой группы соединены с первыми входами соответствующих счетчиков группы, группа разрядных выходов выходного регистра является группой информационный выходов устройства, выход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ и с запросным выходом устройства, второй вход второго элемента ИЛИ и первый вход третьего элемента ИЛИ соединены с входом сброса устройства, второй вход третьего элемента ИЛИ и первый вход четвертого элемента ИЛИ соединены с ответным входом устройства.

второй вход четвертого элемента ИЛИ соединен с входом пуска устройства, группа информационных входов регистра заявок является группой информационных входов устройства, выходы регистра заявок соединены с первыми входами соответствующего элемента И второй группы, вторые входы элементов И второй группы соединены с единичным выходом триггера, выход второго элемента ИЛИ соединен с нулевым входом триггера, введены буферныл регистр, группа элементов ИЛИ, третья и четвертая группа элементов И и узел анализа приоритета, причем первый выход каждого счетчикагруппы соединен с первым входом соответствующего элемента ИЛИ группы, второй вход каждого элемента ИЛИ группы соединен с разрешающим входом устройства, второй вход каждого элемент И первой группы соединен с выходом соответствующего элемента ИЛИ группы второй выход каждого счетчика группы соединен с первым входом соответствующего элемента И третьей группы, второй вход каж;цого элемента И третьей группы соединен с соответствующим разрядным выходом буферного регистра выходы элементов И третьей группы содинены с входами узла анализа приоритета, выходы элементов И второй группы соединены с группой информационны входов буферного регистра, управляющий вход буферного ре гистра соединен с выходом второго элемента ИЛИ,группа управляющих входов регистра заявок соединена с выходами элементов И четвертой группы, информационные входы выходного регистра соединены соответственно с выходами элементов И четвертой группы и с первого элемента ИЛИ, выход каждого элемента И четвертой группы соединен со вторы входом соответствующего счетчика группы, управляющий вход выходного регистра соединен с выходом третьего элемента ИЛИ, каждый выход узла анализа приоритета соединен с первым входом соответствующего- элемента И четвертой группы, вторые входы элементов И четвертой- группы соединены с нулевым выходом триггера, выход четвёртого элемента ИЛИ соединен с единичным входом триггера.

Кроме того, узел анализа приоритета, содержит блок элементов ИЛИ, и-каналов, а в каждом канале, кроме П-Г(}), элемент И, блок элементов НЕ, блой элементов И и дешифратор, в м-м канале блок элементов И, блок элементов НЕ и дешифратор, причем каждый i -и выход ptti-n) каждого дешифратора канала, кроме п -го выхода дешифратора п -го канала и первого выхода дешифратора первого канала соединен с i -м входом блока элементов НЕ -го канала и с -ым входом блока элементов И i-го канала, первый выход дешифратора первого канала соединен с первым входом блока элементов. НЕ первого канала, с входом элемента ИЛИ, п -и выход дешифратора w-ro канала соединен с п -ым входом блока элементов И м -го канала, группа выходов блока элементов НЕ каждого канала, кроме и -го, соединена с группой входов блока элементов И канала и с группой входов элемента И канала , выход элемента И канала соединен с управляющим входом, блока элементов следующего канала, группа выходов блока элементов И каждого канала соединена с соответствующей группой входов блока элементов ИЛИ, группа выходов блока элементов ИЛИ является группой выходов узла, групп выходов блокаэлементов НЕ м -го канала соединена с группой входов блока элементов И и -го канала.

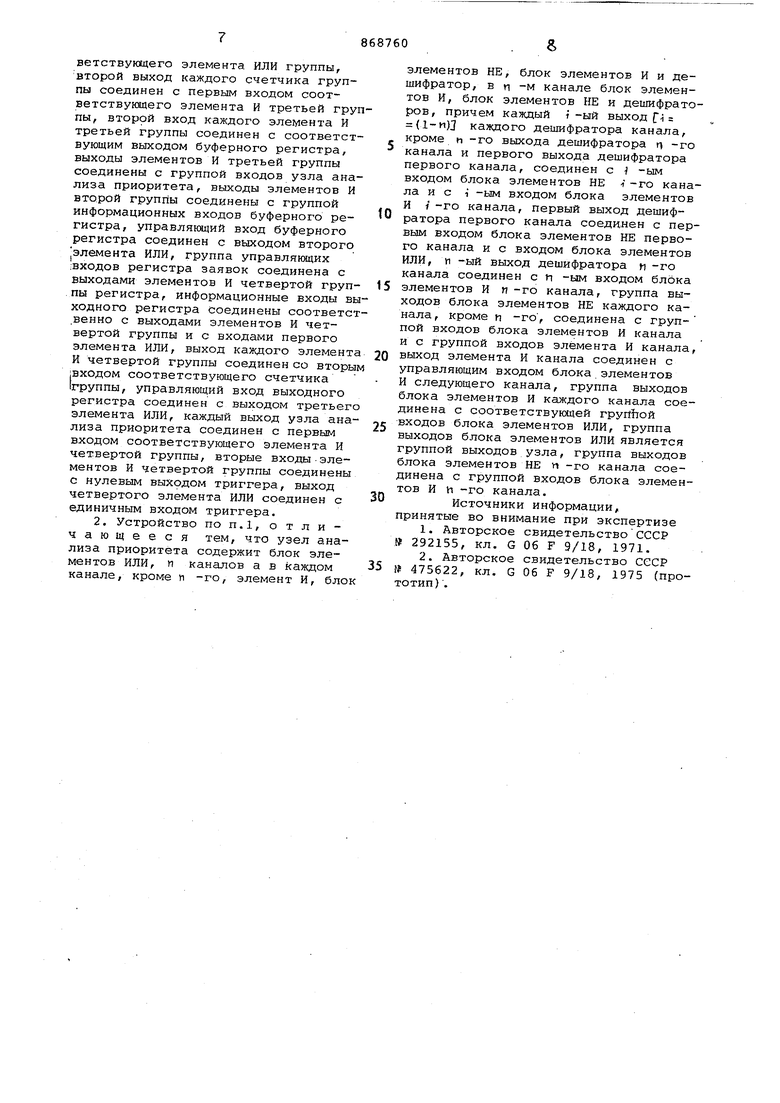

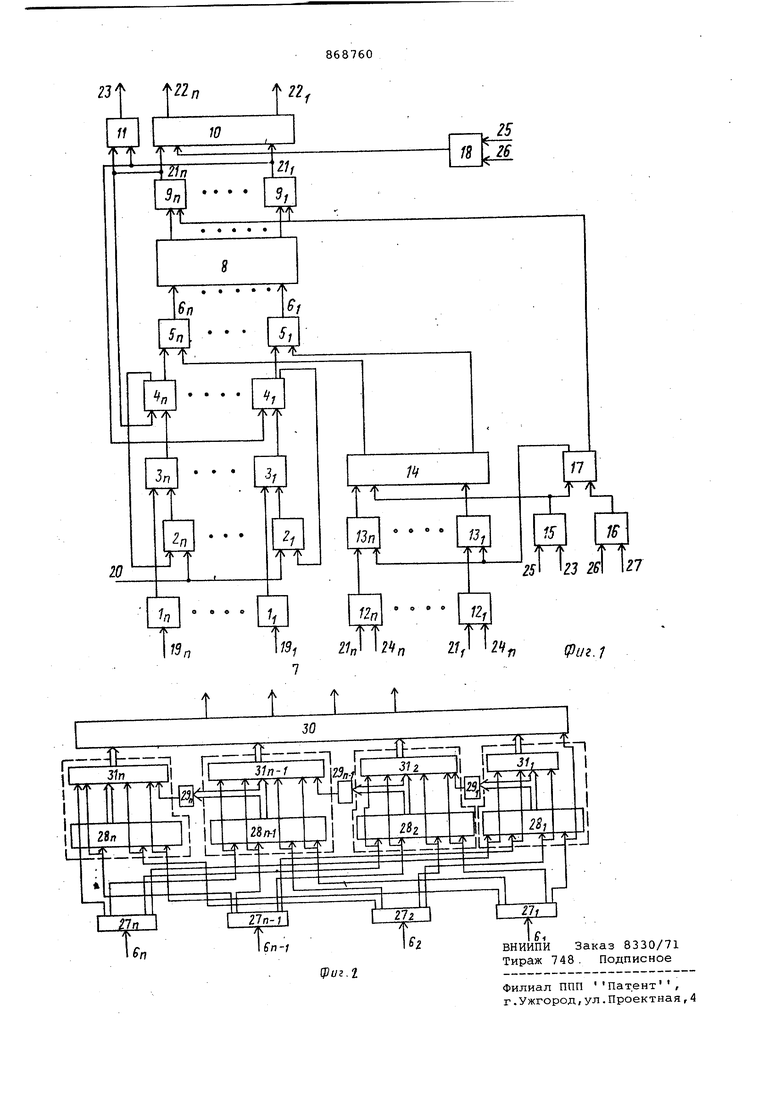

Схема устройства приведена на фи г. 1.

Устройство содержит группу регистров приоритетов, группу элементов ИЛИ , элементьР И 3-i-З первой группы, группу счетчиков 4-|-4 элементы И третьей группы,входы блока анализа приоритета, выходы блока анализа приоритета, узел 8 анализа приоритета, элементы И четвертой группы, выходной регистр 10, первый элемент ИЛИ 11, регистр заявок ,, элементы И , второй группы, буферный регистр 14, второй элемент ИЛИ 15, четвертый элемент ИЛИ 16, триггер 17, третий элемент ИЛИ 18, кодовые входы 19 устройства, разрешающий вход 20 устройства, выходы 21.,-2If, элементов И четвертой группы, выходные шины регистра,информационные выходы устройства, запросный выход 23, информационные входы 24i-24n, вход 25 сброса, ответный вход 26.

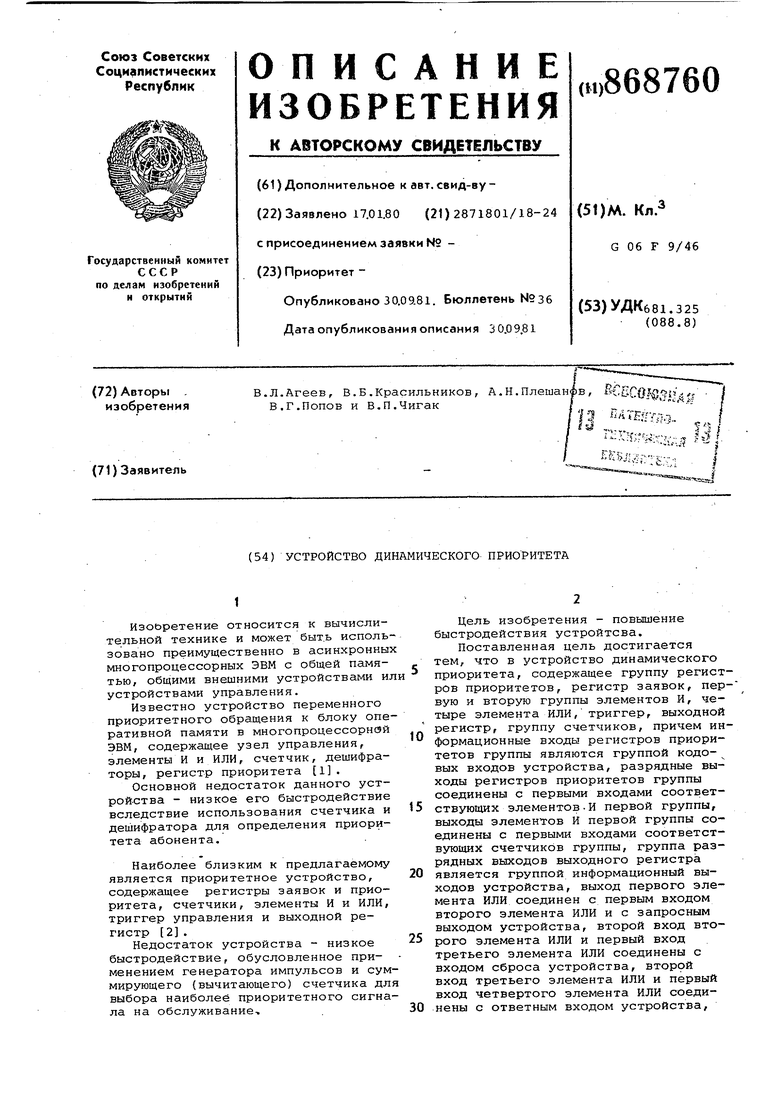

Структурная схема узла анализа приоритетов приведена на фиг.2.

Узел анализа приоритетов содержит дешифраторы , блоки элементов НЕ , элементы И 29i-29n, блоки элементов ИЛИ 30, блоки элементов И 31i-31rt .

Узел 8 анализа приоритетов работает следующим образом.

Пусть наименьший приоритетный код находится во втором счетчике 4, т.е. на втором„выходе дешифратора 27f будет единичный сигнал. При этих условиях все первые выходы всех дешифраторов, а также вторые выходы, кроме 2-го дешифратора, нулевые. Тогда выходы элементов НЕ блока первого канала 28 будут единичными, элемент И 29 разрешает анализ элементов И 31,2 второго канала, открывая по первым входам все элементы 5 И этой группы. Второй выход первого дешифратора - нулевой, поэтому единичный сигнал с выхода первого элемента НЕ блока 28-2 второго канал анализа открывает по второму входу все элементы И блока 31 , начиная со второго. На входе второго элемен та НЕ блока 28 и на третьем входе второго элемента И 31 действует единичный сигнал. Нулевой сигнал с выхода второго элемента НЕ блока 28 закрывает все элементы И блока 31 начиная с третьего, по третьему входу. С. выхода второго элемента И бло ка 31 а единичный сигнал через элемент ИЛИ 30 -2 поступает на выходную шину 72. узла анализа. Устройство работает следунвдим образом. . Запросы от абонентов поступают п входам .24„ и принимаются в соответствующие разряды регистра заявок. Приоритетность абонентов задается приоритетными кодами, занесен ными в регистры приоритетов ,, а затем по сигналу приема приоритетных кодов, поступающему по входу 20, через элементы И записываются в счетчики ,. Сигналом начального гашения, поступающим njo входу 25, через второй элемент ИЛИ 15 устанавл ваются в нулевое состояние триггер 17 управления, б гферный регистр 14 и через четвертый элемент ИЛИ 18 выходной регистрЮ. Сигнал с нулево го выхода триггера 17 разрешает перепись заявок из регистра заявок буферного регистра 14, единичные состояния которых обеспечивают выдачу приоритетных кодов из счетчиков в узел 8 анализа приоритетов через соответствующие элементы И . По сигналу пуска, поступающему по вхЬду 27,.триггер 17 через третий элемент ИЛИ 16 устанавливается в единичное состояние. Сигнал с единич ного выхода триггера 17 разрешает прием выделенного приоритетного сигнала блоком анализа приоритетов через элементы И у выходного регистра 10. В результате появляется сигнал на одном из выходов 21.-21, устройства. Одновременно этот сигнал через первый элемент ИЛИ 11 по выходу 23 поступает в йиде сигнала запроса к абоненту, устанавливает через второй элемент ИЛИ 15 в нулевое состояние триггер 17 управления и буферный регистр 14, а также произво дит установку в нулевое состояние и триггеры , регистра заявок, снимая тем самым из очереди выбранную заявку. Кроме .того, выделенный сигнал блоком анализа приоритетов изменяет значение.приоритетного кода в соответствующем счетчике 4.-4у,. Если в процессе обслуживания абонентов произойдет переполнение одного из счетчиков , то сигнал переполнения с выхода счетчика обеспечивает перепись приоритетного кода соответству ющего абонента из регистра приоритета , в данный счетчик. При необходимости изменения приоритетного кода абонента в процессе функционирования ЭВМ новый код записывается в соответствующий регистр приоритета по соответствующему входу , а затем по сигналу приема приоритетного кода, поступающему по входу 20, переписывается в соответствующий счетчик , перед началом нового цикла работы устройства. Формула изобретения 1. Устройство динамического приоритета, содержащее группу регистров приоритетов, регистр заявок,, первую и вторую группы элементов И, четыре элемента ИЛИ, триггер, выходной регистр, группу счетчиков, причем ий- формационные входы регистров приоритетов группы являются группой кодовых входов устройства, выходы регистров приоритетов группы соединены с пегЗвыми входами соответствующих элементов И первой группы, выходы элементов и первой группы соединены с первыми входами соответствующих счетчиков.группы, группа выходов выходного регистра является.группой информационных выходов устройства, выход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ и с запросным выходом устройства, второй вход второго элемента ИЛИ и первый вход третьего элемента ИЛИ соединена с входом сброса устройства, второй вход третьего элемента ИЛИ и первый вход четвертого элемента ИЛИ соединены с ответным входом устройства, второй вход четвертого элемента ИЛИ соединен с входом пуска устройства, группа информационных входов регистра заявок является группой информационных входом устройства, выходы регистра заявок соединены с первыми входами соответствующего элемента И второй группы, вторые входы элемен.тов И второй группы соединены с единичным выходом триггера,выход второго элемента ИЛИ соединен с нулевым входом триггера, отличающееся тем, что, с целью повышения быстродействия, устройство содержит буферный регистр, группу элементов ИЛИ, третью и четвертую группы элементов И и узел анализа приоритета, причем первый выход каждого счетчика группы соединен с первым входом соответствующего элемента ИЛИ группы, второй вход каждого элемента ИЛИ группы соединен с разрешающим входом устройства, второй вход каждого элемента И первой группы соединен с выходом соответствующего элемента ИЛИ группы, второй выход каждого счетчика группы соединен с первым входом соответствующего элемента И третьей группы, второй вход каждого элемента И третьей группы соединен с соответствующим выходом буферного регистра, выходы элементов И третьей группы соединены с группой входов узла анализа приоритета, выходы элементов И второй группы соединены с группой информационных входов буферного регистра, управлякиций вход буферного регистра соединен с выходом второго элемента ИЛИ, группа управляющих входов регистра заявок соединена с выходами элементов И четвертой группы регистра, информационные входы выходного регистра соединены соответст.венно с выходами элементов И четвертой группы и с входами первого элемента ИЛИ, выход каждого элемента И четвертой группы соединен со вторым ВХОДОМ соответствующего счетчика (группы, управляющий вход выходного регистра соединен с выходом третьего элемента ИЛИ, каждый выход узла анализа приоритета соединен с первым входом соответствующего элемента И четвертой группы, вторые входы-элементов И четвертой группы соединены с нулевым выходом триггера, выход четвертого элемента ИЛИ соединен с единичным входом триггера.

2. Устройство ПОП.1, отличающееся тем, что узел анализа приоритета содержит блок элементов ИЛИ, п каналов а в каждом канале, кроме п -го, элемент И, блок

элементов НЕ, блок элементов И и дешифратор, в п -м канале блок элементов И, блок элементов НЕ и дешифраторов, причем каждый i -ый выход fi (l-n)J каждого дешифратора канала, кроме h -го выхода дешифратора г) -го канала и первого выхода дешифратора первого канала, соединен с 1 -ым входом блока элементов НЕ -f -го канала и с 1 -ым входом блока элементов И f -го канала, первый выход дешифратора первого канала соединен с первым входом блока элементов НЕ первого канала и с входом блока элементов ИЛИ, м -ый выход дешифратора ц -го канала соединен с п -ым входом блока элементов И н-го канала, группа выходов блока элементов НЕ каждого канала, кроме п -го, соединена с группой входов блока элементов И канала и с группой входов элемента И канала выход элемента И канала соединен с управляющим входом блока.элементов И следующего канала, группа выходов блока элементов И каждого канала соединена с соответствующей группой входов блока элементов ИЛИ, группа выходов блока элементов ИЛИ является группой выходов узла, группа выходов блока элементов НЕ м -го канала соединена с группой входов блока элементов И п -го канала.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельствоСССР № 292155, кл. G Об F 9/18, 1971.

2.Авторское свидетельство СССР

№ 475622, кл, G 06 F 9/18, 1975 (прототип) .

t

гз

22.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для сопряжения абонентского пункта с цифровой вычислительной машиной | 1980 |

|

SU941981A1 |

| Многоканальное приоритетное устройство | 1981 |

|

SU972510A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1460725A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1777140A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Многоканальное устройство переменного приоритета | 1983 |

|

SU1125627A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ ЗАПРОСОВ | 2000 |

|

RU2157561C1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1368887A1 |

| Устройство для обслуживания запросов | 1983 |

|

SU1126958A1 |

13nЩ Jln 2/Д|2 „

7

t t t

(flu. 7

Авторы

Даты

1981-09-30—Публикация

1980-01-17—Подача