Изобретение относится к вычислис гельной технике и может быть приме.нено, например в мультипроцесЬоЕ ных вычислительных системах с общей оперативной памятью.

Известно приоритетное устройство, содержащее блоки, в состав котбрых ; входят деЬМфраторы, элементы И, ;НЕ и регистры .

Недостатком этого устройства является статическое назначение приоритетов группам объектов, что услож.няет.организацию вычислений в системе. .. .

Наиболее близким техническим ре: шением к предложенному является уст-4 ройство, содержащее блок управления, генератор импульсов, выходной элемент ИЛИ, п-разрядный регистр заяВоЛ, п-разрядный выходной регистр, К .логических блоков, а калсдый из которых входят регистр приоритета,, первая группа элементов И, счетчик, элемент И, элемент КШ, вторая Группа элементов И и .узел анализа приоритетной 3

Недостатком устройства является низкое быстродействие и недостаточная надежность.

Цель изобретения - повышение быст родействия и надежности.

Поставленная цель достигается тем, что многокайальное приоритет- . ное устройство, содержащее блок управления, первый элемент ИЛИ, N каналов (где N - число источников заявок), каждый из которых содержит регистр приоритета, регистр заявок,

10 :узел анализа заявок, две группы элементов И, выходной регистр, причем выход первого элемента ИЛИ соединен с ввосодом конца цикла устройства и с входом сброса блока управления,

15 вход пуска которого соединен с вхог-; дом пуска устройства, сигнальный вход блока х.правл ения соединен с входом ответа абонента .устройства, информационные входы регистра заявок

20 каждого канала соединены с входа№J соответствунвдей группы входов заявок устройства, входы регистра приоритета соединены с входами соот ветствующей ГРУППЫ входов приорите25та устройства, выходы регистра заявок каждого канала соединены с группой информационных входов блока управления и с первой::::группой входов узла анализа заявок своего канала,

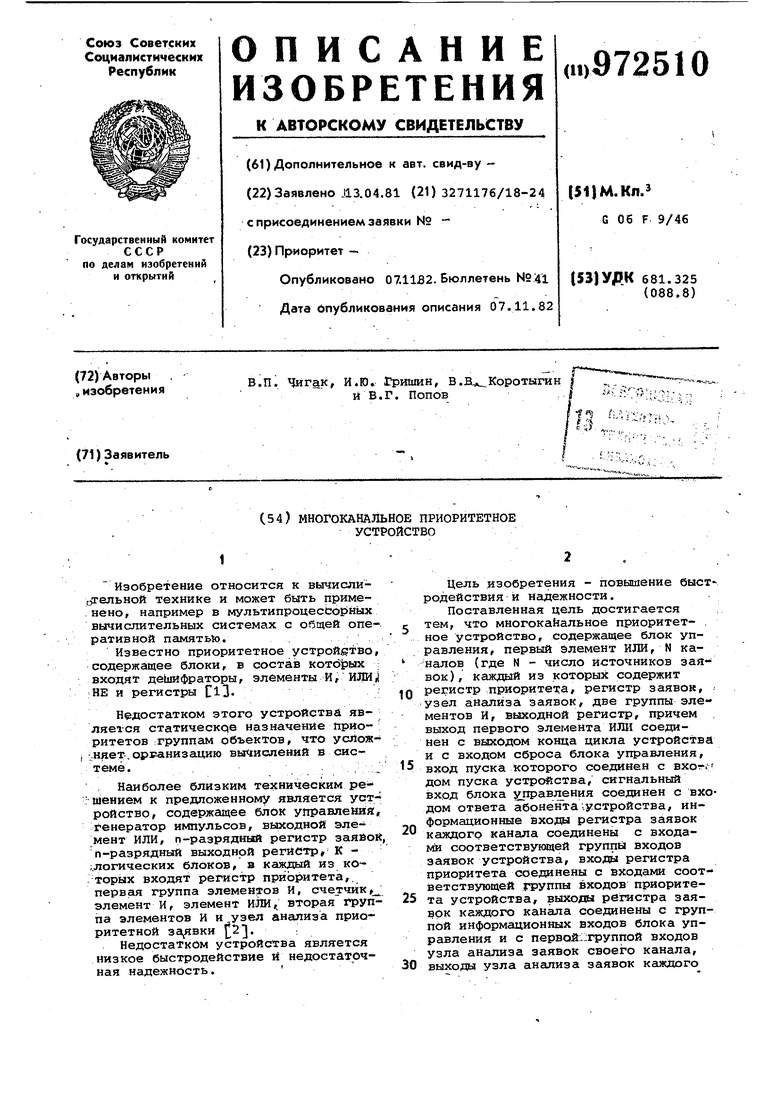

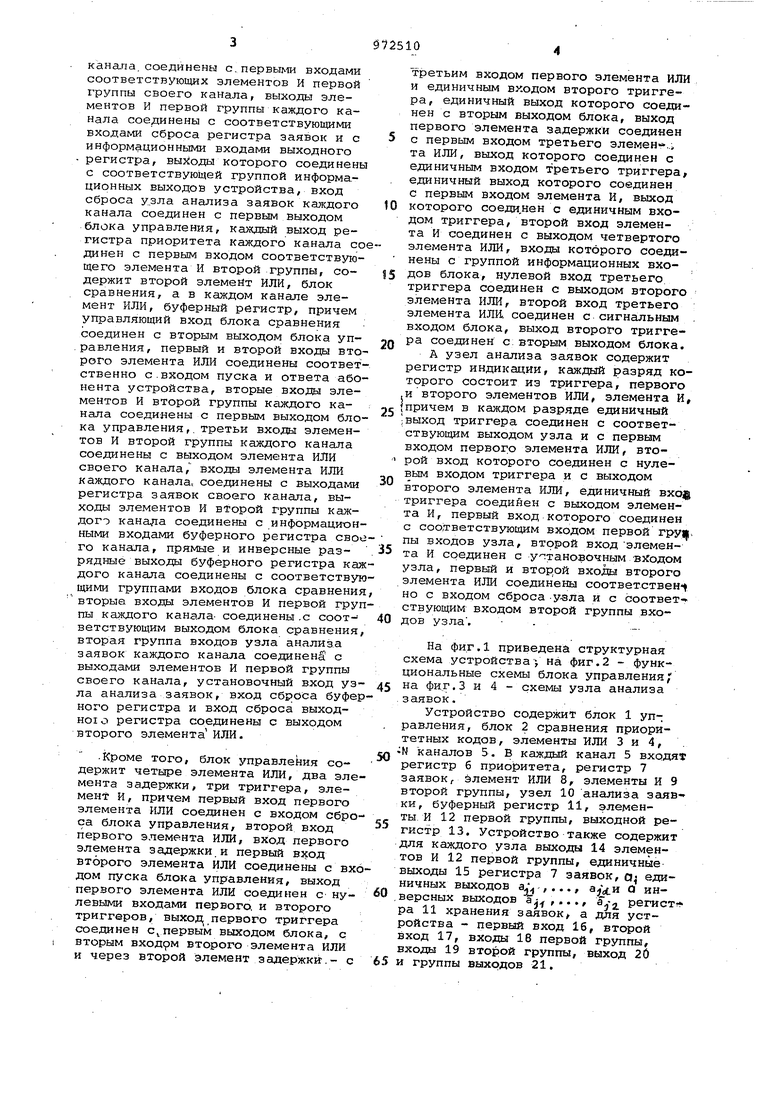

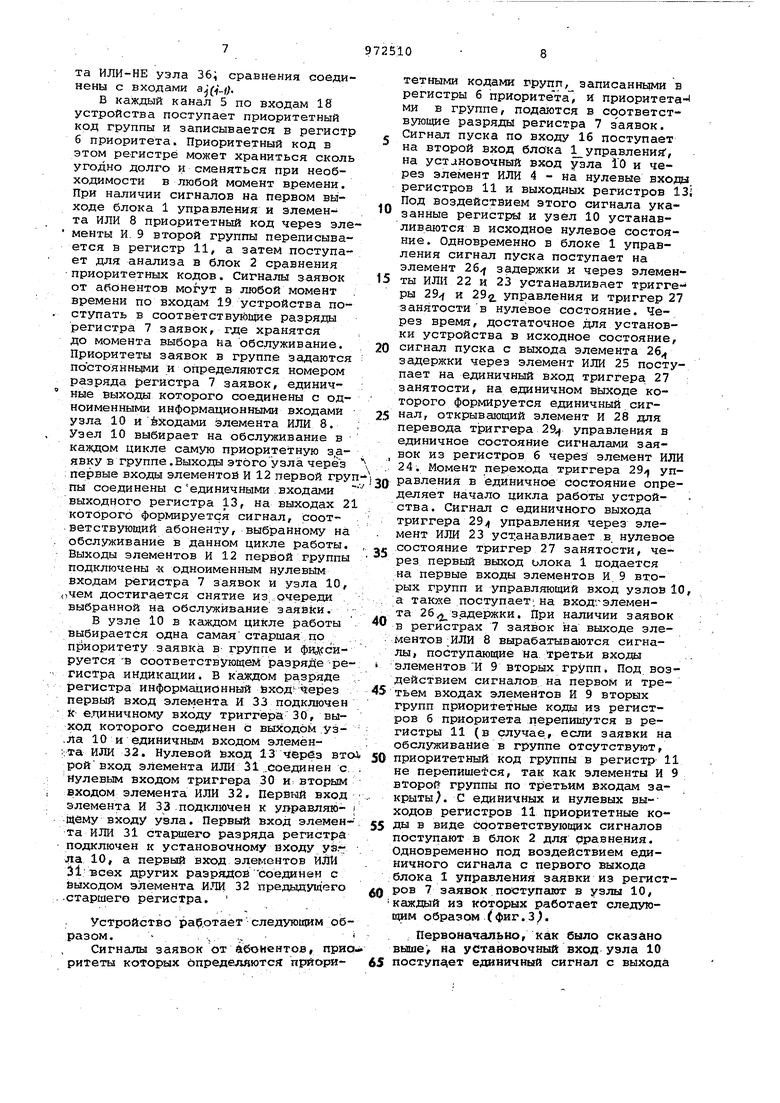

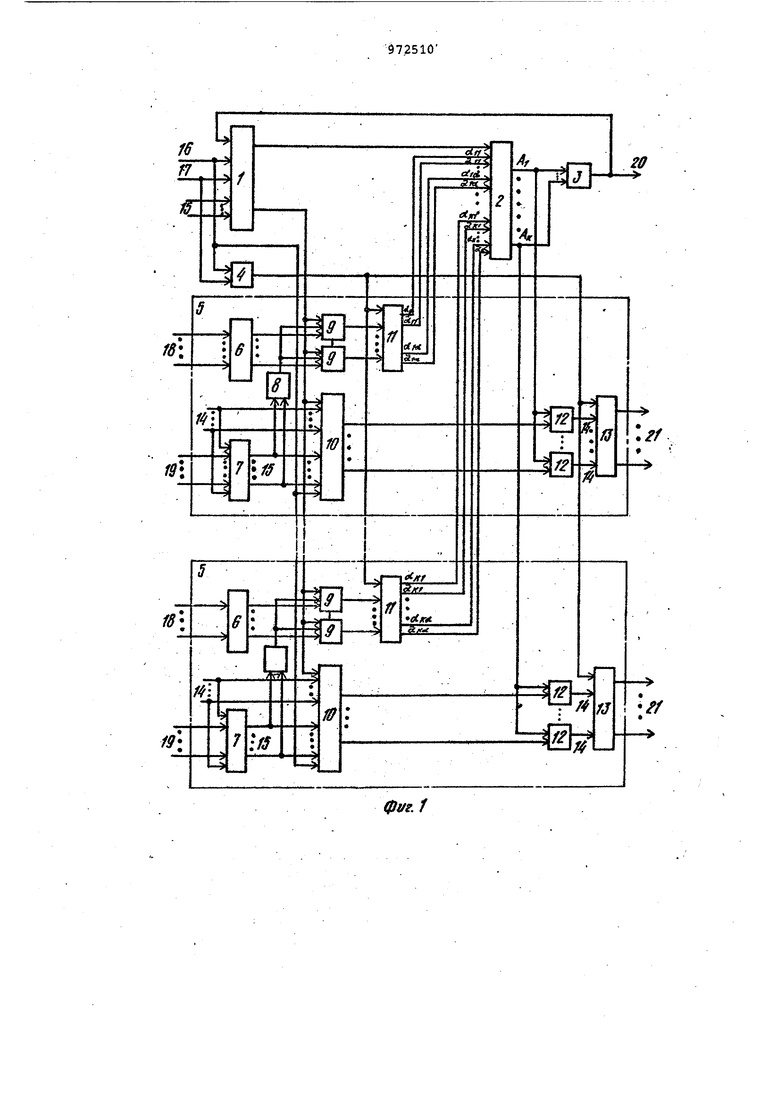

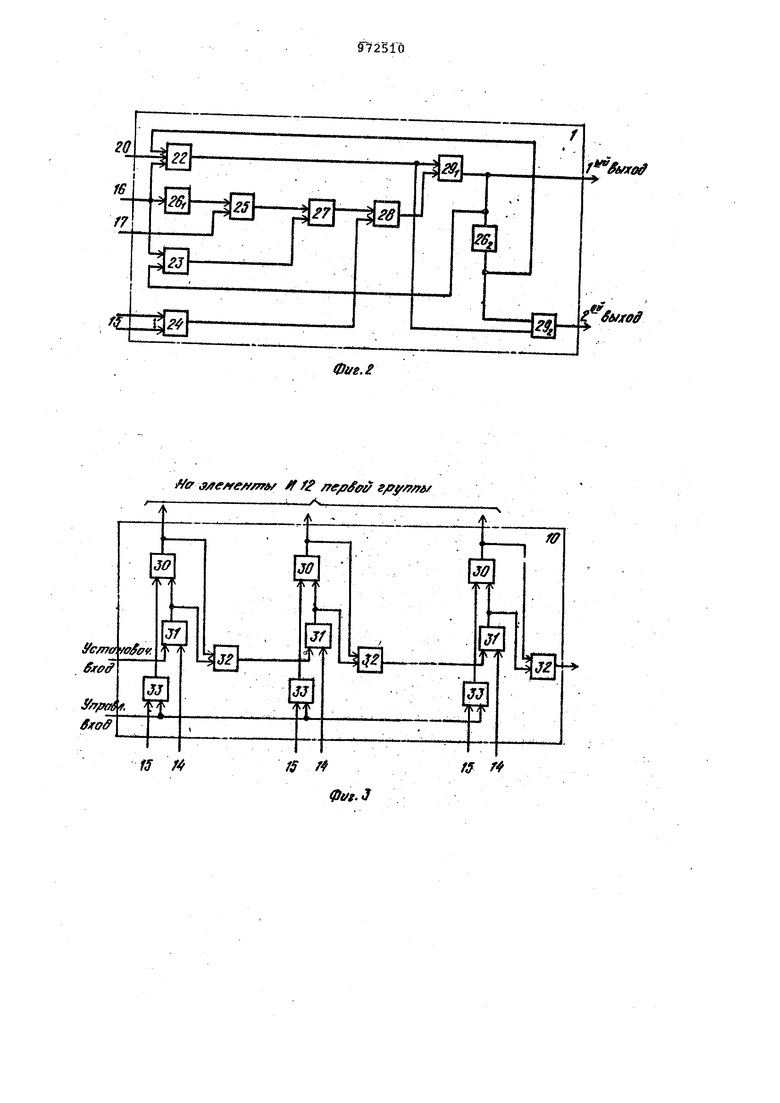

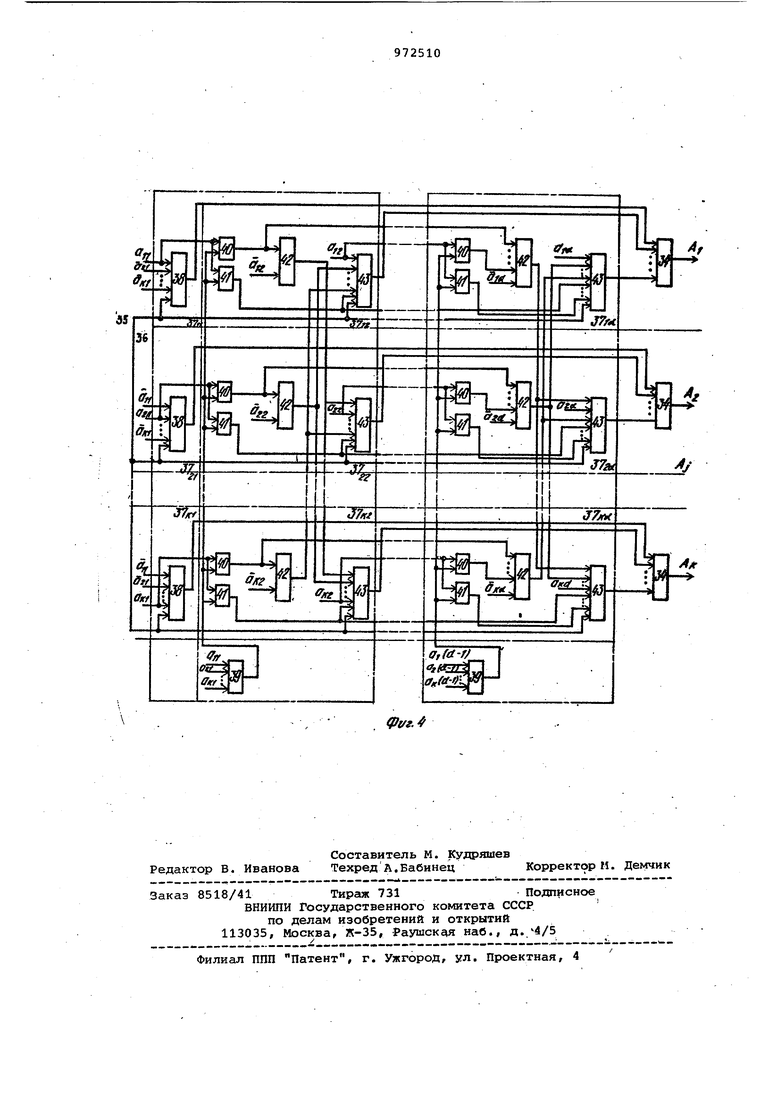

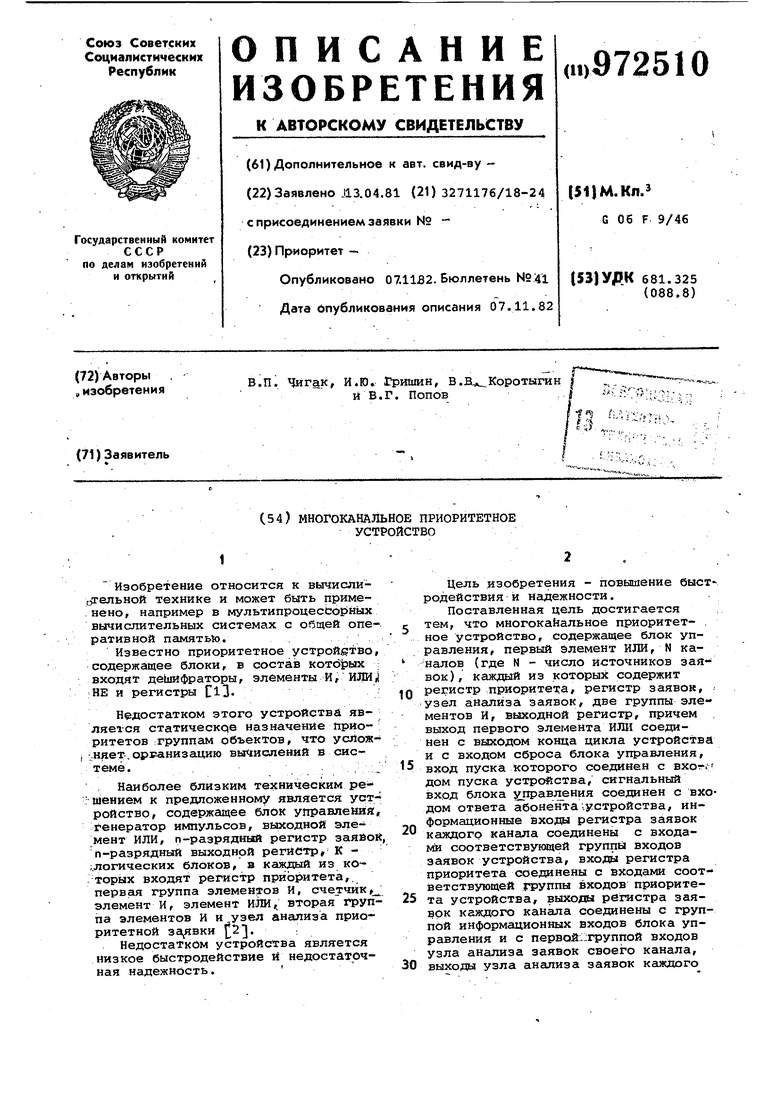

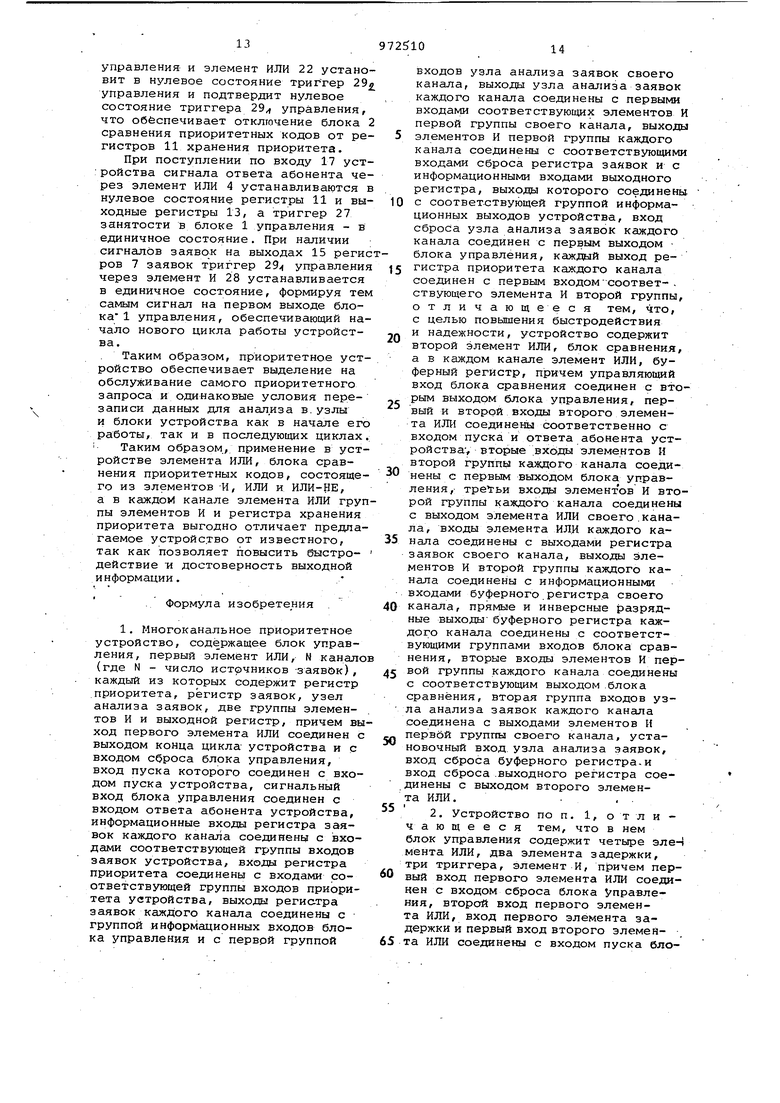

30 выходы узла анализа заявок каждого канала, соединены c.пepвы 1и входами соответствующих элементов И первой группы своего канала, выходы элементов И первой группы каждого канала соединены с соответствующими входами сброса регистра заявок и с информационными входами выходного регистра, выходы которого соединены с соответствующей группой информационных выходов устройства, вход сброса анализа заявок каждого канала соединен с первым выходом блока управления, каждый выход регистра приоритета каждого канала со дивен с первым входом соответствующего элемента И второй группы, содержит второй элемейт ИЛИ, блок сравнения, а в каждом канале элемент ИЛИ, буферный регистр, причем управляющий вход блока сравнения соединен с вторым выходом блока управления, первый и второй входы вто рого элемента ИЛИ соединены соответ ственно с.входом пуска и ответа або нента устройства, вторые входы элементов И второй группы каждого канала соединены с первым выходом бло ка управления,, третьи входы элементов И второй группы каждого канала соединены с выходом элемента ИЛИ своего канала, входы элемента ИЛИ каждого канала, соединены с выходами регистра заявок своего канала, выходы элементов И второй группы каждого канала соединерлл с информацион ными входами буферного регистра сво го канала, прямые и инверсные разрядные выходы буферного регистра ка дого канала соединены с соответству щими группами входов блока сравнени вторые входы элементов И первой гру пы каждого канала- соединены .с соответствующим выходом блока сравнения вторая группа входов узла анализа заявок каждого канала соединен с выходами элементов И первой группы своего канала, установочный вход уэ ла анализа заявок, вход сброса буфе ного регистра и вход сброса выходHOIо регистра соединены с выходом второго элементаИЛИ. .Кроме того, блок управления содержит четыре элемента ИЛИ, два эле мента задержки, три триггера, элемент: и, причем первый вход первого элемента ИЛИ соединен с входом сбро са блока управления, второй вход первого элемента ИЛИ, вход первого элемента задержки.и первый вход второго элемента ИЛИ соединены с вх дом пуска блока управления, выход первого элемента ИЛИ соединен с нулевыми входами первога и второго триггеров, выхоД|,первого триггера соединен с первым выходом блока, с вторым ВХОД9М второго элемента ИЛИ и через второй элемент задержки-.- с третьим входом первого элемента ИЛИ и единичным входом второго триггера, единичный выход которого соединен с вторым выходом блока, выход первого элемента задержки соединен с первым входом третьего элемеН.. та ИЛИ, выход которого соединен с единичным входом третьего триггера, единичный выход которого соединен с первым входом элемента И, выход которого соеди.нен с единичным входом триггера, второй вход элемента И соединен с выходом четвертого элемента ИЛИ, входы которого соединены с группой информационных входов блока, нулевой вход третьего триггера соединен с выходом второго элемента ИЛИ, второй вход третьего элемента ИЛИ, соединен с сигнальным . входом блока, выход второго триггера соединен с; вторым выходом блока. А узел анализа заявок содержит регистр индикации, каждый разряд которого состоит из триггера, первого и второго элементов ИЛИ, элемента И, причем в каждом разряде единичный выход триггера соединен с соответствующим выходом узла и с первым входом первого элемента ИЛИ, второй вход которого соединен с нулевым входом триггера и с выходом второго элемента ИЛИ, единичный вхо$ триггера соедийен с выходом элемента И, первый вход которого соединен с соо;тветствующим входом первой rpyij. пы входов узла, второй вход элемента И соединен с установочным -вггодом узла, первый и втор1Ой входы второго элемента ИЛИ соединены соответственно с входом сброса -у-зпа и с соответ- ствующим входом второй группы входов узла . На фиг.1 приведена структурная схема устройства V на фиг.2 - функциональные схемы блока управления, на фиг.З и 4 - схемы узла анализа .заявок. Устройство содержит блок 1 управления, блок 2 сравнения приоритетных кодов, элементы ИЛИ 3 и 4, . -N каналов 5. В каждый канал 5 входят регистр 6 приоритета, регистр 7 заявок, элемент ИЛИ 8, элементы И 9 второй группы, узел 10 анализа заявки, буферный регистр 11, элементы И 12 первой группы, выходной регистр 13. Устройство также содержит для каждого узла выходы 14 элементов И 12 первой группы, единичные выходы 15 регистра 7 заявок, а единичных выходов ал , ..., О ин.версных выходов а,..., s-y ретс-г ра 11 хранения заявок а для устройства - первьай вход 16, второй вход 17, входы 18 первой группы, входы 19 второй группы, выход 20 и группы выходов 21. Блок 1 управления содержит элементы ИЛИ 22 - 25,элементы 26 и 26 задержки, триггер 27 занятости, элемент И 28, триггеры 29 и 29- уп равления . Узел 10 анализа приоритетной зая ки содержит многоразрядный регистр индикации, каждый разряд которого состоит из триггера 30, первого эле мента ИЛИ 31, второго элемента ИЛИ элемента И 33. Блок 2 сравнения приоритетных ко дов содержит Kj -входных элементов ИЛИ 34,1 К выходов A riiAj,, Кд вхо дов и К at, входов , где j 1,2,...,Ки 1 1, 2,...,с, а также управляющий вход 35 и oi, поразрядных узлов ..., 36 сравне йия. Узел 364 сравнения состоит из К схем 37.; (j 1, 2,..., К, и1 1) анаЛиза, каждая из которых пре ставляет tK + 1)-входовой элемент И 38.УЗЛЫ Зб2, ..., 36 сравнения сог держат К-входовой элемент ИЛИ-НЕ 39 К схем анализа 37 , где j 1, 2,. .., К, ( 2, . .., оС . Каждая схема 37 анализа в своем составе имеет ;лвухвходовой элемент ИЛИ-НЕ 40, пер :вый двухвходовой элемент ИЛИ 41, второй t-входовой элемейт ИЛИ -42 и (К + 1)-входовой элемент. И 43. Блок 1 управления обеспечивает устойчивую работу устройства в первом и последующих циклах работы. Для этого на его первый вхоД с вы-хода элемента ИЛИ 3 поступает сигнал конца цикла работы, на второй вход с первого входа 16 устройства подается сигнал пуска, а на третий вход с второго входа 17 устройства сигнал ответа абонента. Группа вхо;,дов 16 соединена с единичными входа ми регистров 7 заявок. Сигнал с пер вого выхода управления работой каналов , для чего он подается на первые входы элементов И 9 второй груп пы и на управляющие входы узлов 10, сигнал с второго выхода через управляющий вход 35 блока 2 сравнения приоритетных кодов обеспечивает устойчивую работу последнего. Эле- .. мент ИЛИ 4 своим выходом соединен с нулевыми входами регистра 11 и выходного регистра 13, а также с установочным входом узла 10, а входами подключен к входам 16 и 17 устройства.. В блоке 1 управления сигнал конца цикла работы с выхода 20 устройства через первый вход блока 1 и первый вход элемента ИЛИ 22 поступает на нулевые входы триггеров 29 и 29- управления. Сигнал с единичного выхода триггера 29 управления подается на первый выход блока 1 и на второй вход элемента ИЛИ 23, а также через элемент 26 задержки поступает на третий вход элемента ИЛИ 22 и единичный вход триггера 29, управления, единичный выход которого соединен с вторым выходом блока 1 управления. Сигнал пуска с первого входа 16 устройства через второй вход блока 1 подается на второй вход элемента ИЛИ 22, вход элемента 26 задержки и первый вход элемента ИЛИ 23 выход которого подключен к нулевому входу триггера 27 занятости. Выход элемента 26 задержки и третий вход блока 1, на который подается сигнал ответа абонента с входа 17 устройства, через элемент ИЛИ 25 соединены с единичным входом триггера 27 занятости, единичный выход которого через первый вход элемента И 28 соединен с единичным входом триггера 29 управления. На второй вход элемента И 28 через элемент ИЛИ 24 подаются сигналы заявок с группы входов блока 1 управления. Блок 2 сравнения приоритетных кодов определяет в каждом цикле самую приоритетную группу абонентов путем анализа приоритетных кодов групп. Входы и соединены соответственно с единичным и нулевым выходом i-ro разряда регистра 11j -го канала 5, где J 1 ,..., К и i 1, .. ., oi.- Выходы А , ..., АИ сое- . динены с вторыми входами элементов И 12 первых соответствующих групп. В самом блоке 2 сравнения приоритетных кодов j-и вход элемента И 38 схемы анализа узла 36 анализа соединен с входом а.- (jfil 1 Kj) ;(К + 1)-и вход подключен к управляющему входу 35, а все остальные - к входам , где 1 1,..., К и 1 . j. В каждой схеме 37,- анализа узлов 36,,..., 36 сравнения первые входы элементов ИЛИ-НЕ 40 и ИЛИ 41 соединены с j-ым входом элемента И j-й схемы 37.jy анализа предыдущего узла сравнения, а вторые входы этих элементов подключены к выходу элемента ИЛИ-НЕ 39 данного узла 36 сравнения. Выход элемента ИЛИ 41 подключен к (К 4- - 1)-ым входам элементов И 43 схем анализа узлов 36ft сравнения, где Jb . I + + 1,...,оС. Выход элемента ИЛИ-НЕ. 40 подключен к ( /i- 1)-ым входам элементов ИЛИ 42 схем 37;-й анализа узлов 36f, сравнения. Выход элемента ИЛИ 42 соединен с j-ым входом эле ментов И 43 всех других схем анализа данного узла 36 сравнения, а | i-й вход этого элемента подключен к входу aj . Выход элемента И 43 соединен с входом соответствующе го элемента ИЛИ 34, j-й вход - с Ьходом a.,v бло-. ка 2, (К + )-й вход подключен к управляющему входу 35. Входы элемента ИЛИ-НЕ узла 36i сравнения соединены с входами . В каждый канал 5 по входам 18 устройства поступает приоритетный код группы и записывается в регистр 6 приоритета. Приоритетный код в этом регистре может храниться сколь угодно долго и сменяться при необходимости в любой момент времени. При наличии сигналов на первом выходе блока 1 управления и элемента ИЛИ 8 приоритетный код через эле менты И. 9 второй группы переписывается в регистр 11, а затем поступает для анализа в блок 2 сравнения приоритетных кодов. Сигналы заявок от абонентов могут в любой момент времени по входам 19 устройства поступать в соответствуйщие разряды регистра 7 заявок, где хранятся до момента выбора на обслуживание. Приоритеты заявок в группе задаются постоянными и определяются номером разряда регистра 7 заявок, единич° ные выходы которого соединены с одноименными информационными входами узла 10 и йХодами элемента ИЛИ 8. Узел 10 выбирает на обслуживание в каждом цикле самую приоритетную заявку в группе. Выходы этого узла через : первые входы элементов И 12 первой rpy пы соединены сединичными входами выходного регистра 13, на выходах 2 которого формируется сигнал, соответствующий абоненту, выбранному на . обслуживание в данном цикле работы. Выходы элементов И 12 первой группы подключены -к одноименным нулевым входам регистра 7 заявок и узла 10, (тчем достигается снятие из очереди выбранной на обслуживание заяйкй. В узле 10 в каждом цикле работы выбирается одна самаястаршая по приоритету заявка в группе и фи;)сируетсяВ соответствующем разрядере гистра индикации. В каждом разряде регистра информационный йход- ерез первый вход элемента И 33 подключен J единичному входу триггера 3О, выход которого соеданен с выходом .уз,ла 10 и единичным входом элемен;,та ИЛИ 32. Нулевой вход 13 через вт ройвход элемейта ИЛИ 31..соединен с Нулевым входом триггера 30 и вторым входом элемента ИЛИ 32. Первый вход элемента И 33 подключен к управляюиему входу узла. Первый вход элемен та ИЛИ 31 стариего разряда регистрй подключен к установочному входу ys.r ла 10, а первый вход элементов ЙЙЙ 31всех других разрйЯ;ой соединен с Выходом элемента ИЛИ 32 предыдущего .-старшего регистра. Устройство работает следующим об разом. - ч ... Сигналы заявок от абонентов, при ритеты которых определяются прйоритетными кодами групп, записанньзми в регистры б приоритета, и приоритетами в группе, подаются в соответствующие разряды регистра 7 заявок. Сигнал пуска по входу 16 поступает на второй вход блока управления , на установочный вход узла 10 и через элемент ИЛИ 4 - на нулевые входы регистров 11 и выходных регистров 13i Под воздействием этого сигнала указанные регистры и узел 10 устанавливаются в исходное нулевое состояние . Одновременно в блоке 1 управления сигнал пуска поступает на элемент 26 задержки и через элементы ИЛИ 22 и 23 устанавливает триггеры 29/f и 29. управления и триггер 27 занятости в нулевое состояние. Через время, достаточное для установки устройства в исходное состояние, сигнал пуска с выхода элемента 26 задержки через элемент ИЛИ 25 поступает на единичный вход триггера 27 занятости, на единичном выходе которого формируется единичный сигнал, открывающий элемент И 28 для перевода триггера 29 управления в единичное состояние сигналами заявок из регистров б через элемент ИЛИ 24. Момент перехода триггера 29 управления в единичное состояние определяет начало цикла работы устройства. Сигнал с единичного выхода триггера 294 управления через элемент ИЛИ 23 уст.анавливает в. нулевое состояние триггер 27 занятости, через первый выход олока 1 подается на первые входы элементов И 9 вторых групп и управляющий вход узлов 10, а также поступает;на входгэлемента 26 задержки. При наличии заявок в регистрах 7 заявок на выходе элементов ;ИЛИ 8 вырабатываются сигналы, поступающие на третьи входи элементовИ 9 вторых групп. Под. воздействием сигналов на первом и третьем входах элемейТов И 9 вторых групп приоритетные коды из регистров 6 приоритета перепишутся в регистры 11 (в случае, если заявки на обслуживание в группе отсутствуют, приоритетный код группы в регистр 11 не перепишемся, так как элементы И 9 второй группы по третьим входам закрыты . С единичных и нулевых вы-ходов регистров 11 приоритетные коды в виде соответствующих сигналов поступают в блок 2 для сравнения. Одновременно под воздействием единичного сигнала с первого выхода блока 1 управления заявки из регистров 7 заявок поступают в узлы 10, каждый из которых работает следующим образом (фиг.3.. Первоначально, как было сказано вьпие, на установочный вход узла 10 поступает единичный сигнал с выхода элемента ИЛИ 4, который, последовательно, через элементы ИЛИ 31 и 32 устанавливает в нулевое состояние триггеры 30 разрядов регистра индикации . При поступлении сигнала на управляющий вход производится анализ приоритетности заявок в группе. Для определенности предположим, что в какой-то группе одновременно пост пили заявки на обслуживание от 1-го и 3-го абонентов. Тогда единичные сигналы по информационным входам 14 через элементы И 33 i7cтaнaвливaют триггеры 30 первого и третьего разрядов регистра индикации в единично состояние. Но сигнал с единичного выхода триггера 30 первого Чстаршего; разряда через элементы ИЛИ 32 и 31 сбросит в нуль триггер 30 третьего разряда и подтвердит нулевое состояние всех остальных триггеров.. Таким образом, в единичном состоянии будет находиться только триггер 30 первого разряда, соответству щий самой приоритетной заявке в гру пе. Сигнал с единичного выхода триг гера 30 подается для дальнейшей обработки на первый вход первого элемента И 12 первой группы. После того, как будет выбрана нА обслуживание данная заявка, триггер 30 пер вого разряда устанавливается в нулевое состояние сигналом, поступающим с выхода первого элемента И 12 первой группы. Сигнал с выхода триггера 29 управления, пройдя элемент 26 задерж ки , установит в единичное состояние триггер 29 управления, и в нулевое состояние триггер 29/). управления. Низкий уровень сигнала с единичного выхода триггера 29 управления в :каждом канале запирает элементыИ 9 второй группы и элементы И 33 узла 10, обеспечивая тем самым защиту устройства от воздействия приходящих заявок и меняющихся приоритетных кодов в течение цикла его работы. Время задержки элемента. 262 выбирается таким, чтобы оно было дост точным для выделения узлами 10 самой приоритетной заявки и переписи приоритетных кодов из регистров 6 приоритета в регистры 11. Сигнал с выхода триггера 292. подается через второй выход блока 1 управления на управляющий вход 35 блока 2 сравнения приоритетных кодов, в кото-, ром путем сравнения приоритетных кодов выделяется самая приоритетная группа в данном цикле работы. Так как приоритетные коды групп представляют собой целые двоичные числа, то для яснения принципа срав нения этих чисел достаточно рассмотреть работу узлов и 36, так как последующие узлы аналогичны узлу 36 Пусть код старшего разряда только одного j-ro числа равен единице ( Kj). Тогда на входы только элемента И 38 j-й схемы 37j анализа поступят единичные сигналы с входов а а. , . . . , , , )i i 3 pci. На выходе данного элемента И 38 сформируется единичный сигнал, на выходе других элементов И 38 узла 36 сравнения выработаются нулевые сигналы. Единичный сигнал с выхода элемента И 38 через первый вход соответствующего элемента ИЛИ 34 поступает на выход AJ блока 2 сравнения приоритетных кодов. Одновременно на соответствующие входы элементов И 43 всех . схем анализа узлов 36,..., 36 подаются нулевые сигналы с входов а j,-, закрывая тем самым эти элементы и препятствуя выработке ложных сигналов на других выходах блока 2 сравнения приоритетных кодов. Так как значение вторых и последующих разрядов чисел равны нулю, то схемы анализа узлив Зб,..., 362. сравнения никакого влияния на работу блок,а не окажут. Покажем это на работе узла 36-3 сравнения. Единичный сигнал с входа LJ поступает на первые входы элеметнтов ИЛИ-НЕ 40 ч ИЛИ 41 схемы 37/,j анализа. На вторые входы этих же элементов поступает нулевой сигнал с выхода элемента ИЛИ-НЕ 39 узла 36 сравнения. В результате на выходе элемента ИЛИНЕ 40 схемы анализа 37,j сформируется нулевой сигнал, который, поступая на первые входы элементов ИЛИ 42 схем 37.j2,. . ., 31 j , . - , 37.JK анализа никакого влияния на работу блока . не оказывает. На выходе элемента ИЛИ 41 схемы 37 анализа сформируется единичный сигнал, который поступит на (К 1)-е входы элементов И 43 схем 37,j2. , . .., 37, ,. . ., 37.jк. анализа. Однако он также на работу блока не влияет, так как в это время элементы И 43 этих схем анализа закрыты по j-ым входам нулевыми сигналами. На выходах элементов ИЛИ 41 других схем анализа (за исключением cxeNM ) узла 36 сравнения выработаются нулевые сигналы, а на выходе элементов ИЛИ-НЕ 40 этих же схем анализа - единичные сигналы. Единичные сигналы с выхода элемента ИЛИ-НЕ 40 через элементы ИЛИ 42 поступают на соответствующие входы элементов И 43 узлов 36..,., 36 , однако влияния на работу этих элементов не оказывает, так как последние закрыты нулевыми сигналами,по j-ым входам. Нулевые сигналы.с выходов элементов ИЛИ 41 поступают на (К + 1)-ые входы элементов И 43 соответствуюих схем анализа, закрывая вторично эти элементы и повышая тем самым помехоустойчивость блока 2. Единичный сигнсш, поступающий с входа а через второй элемент 42 поступает на соответ-ствующие входы элементов И 43 схем анализа узла 36 срав нания, но и он не влияет на работу блока, так как элементы И 43 предварительно закрыты нулевыми сигнала ми по соответствующим входам. Анало гично узлу Зб2 сравнения работают и все последующие узлы. Таким образом при заданной разрядности кодов чисел сигнал появится только на выходе А;, который является признаком того, что j-я группа является самой приоритетной в данном цикле работы устройства. Если среди старших разрядов чисе имеется несколько единиц, то тогда на выходах всех элементов И .38 узла 36 сравнения сформируются нулевые сигналы, а сигнал сравнения должен выработаться одним из последующих узлов 362L, . .., 36 сравнения. Это происходит следующим образом. Для определенности предположим, что только старшие разряды 1-г и j-ro чисел имеюткод единицы. Тог да единичные сигналы с входов а. ал/( через элементы ИЛИ 41 схем . и 37-)2. анализа поступают на (К+1)-ы входы элементов И 43 первой и j-ой схем анализа узлов 36, . .., 36 сра нения, подготавливая эти элементы к работе. Все другие элементы И 43 блока 2 будут отключены нулевыми си налами с выходов элементов ИЛИ 41 Д,-ых схем анализ,а 6 узла сравнения где Я 1 2,..., К и А 5 1, J. Эти самым в сравнении будут участвовать только 1-е и j-e числа. На ззыходах элементов ИЛИ-НЕ 40 схем 37,j- и 37 анализа сформируются нулевые сигналы за счет поступления единичных сигналов с входов а и на их первые входы. Эти сигналы поступают на первые входы элементов ИЛИ 42 данно и последующих схем 36. , . . , , 36j анализа. Одновременно на выходах элементов ИЛИ-НЕ 39 Д-ых схем анализа узла Зб сравнения сформиру ются единичные сигналы- за счет подачи на их входы нулевых сигналов. Единичные сигналы через элементы ИЛИ 42 поступают на соответствую щие входы элементов И 43 схем ана: лиза узла 3 6 2 сравнения. В результа те на всех входах, за иключением 1-го и j-ro, элементов И 43 схем 37, и 37j анализа будут присутствовать единичные сигналы. Значения сигналов на 1-ом и J-OM входах этих элементов будут определяться значением кодов вторых разрядов 1-г и j-ro чисел. Если коды вторых разрядов этих чисел равны единице, то сравнение в узле 36.2 не произойдет, так на 1-й вход элемента И 43 схемы 37,j анализа и на j-й вход элемента И 43 схемы 37-fi. анализа через элементы ИЛИ 42„с входов и ау соответственно.1 поступают нулевые сигналы. В случае, когда вторые разряды 1-го и j-ro.чисел равны нулю, то сравнение в узле 362. также не произойдет, так как на 1-й вход элемента И 43 схемы 37/f2. анализа и на j-й вход элемента И 43 схемы 37,j анализа с входов а и а.2 поступают нулевые сигналы. Пр.и наличии кода единицы во втрн ром разряде, например j-ro числа, на выходе элемента И 43 схемы 37/ анализа сформируется единичный сигнал за счет того, что на его 1-й и j-й входы подаются единичные сигналы с входов /2. , соответствен. но. Этот сигнал через j-ый вход элемента 34 поступит на выход А.- блока 2 сравнения приоритетных кодов. Работа узлов 36,..., 3 6 ( срав нения при анализе одноименных разрядов чисел аналогична работе узла 362 сравнения. Из анализа работы блока 2 сравнения видно, что в любом случае только на одном из выходов А,...,А,. появится единичный сигнал, соответствующий самой приоритетной группе абонентов, а на остальных выходах сформируются нулевые сигналы. Единичный сирнал с выхода А поступает на вторые входы элементой. И 12 соответствующей первой группы и на один из входов элемента ИЛИ 3. На выходе элемента ИЛИ 3 сформируется сигнал конца цикла работы устройства, который через выход 2U в качестве сигнала запроса на обслуживание поступает в устройство, к которому обращаются абоненты, а также на первый вход блока 1 управления. Так как один из элементов И 12 первой группы по первому входу подготовле,н к открытию сигналом с выхода узла 10, то при поступлении сигнала с выхода Aj на второй вход на его выходе 14 сформируется сигнал, который установит соответствующий разряд выходного регистра 13 в единичное состояние, в результате чего на одном из выходов 21 устройства появится сигнал, сЬответствующий абоненту группы, выбранному на обслуживание в данном цикле работы. Одновременно сигнал с выхода 14 элемента И 12 первой группы устанавливае.т в нулевое состояние соответствующие триггеры регистра 7 заявок и узла 10, снимая из очереди выбранную заявку на обслуживание. Кроме того, сигнал конца цикла работы через первый вход блока 1 управления и элемент ИЛИ 22 устано вит в нулевое состояние триггер 29 управления и подтвердит нулевое состояние триггера 29 управления, что обеспечивает отключение блока сравнения приоритетных кодов от ре гистров 11 хранения приоритета. При поступлении по входу 17 уст ройства сигнала ответа абонента че рез элемент ИЛИ 4 устанавливаются нулевое состояние регистры 11 и вы ходные регистры 13, а триггер 27 занятости в блоке 1 управления - в единичное состояние. При наличии сигналов заявок на выходах 15 реги ров 7 заявок триггер 29 управлени через элемент И 28 устанавливается в единичное состояние, формируя тем самым сигнал на первом выходе блока 1 управления, обеспечивающий на чало нового цикла работы устройства. Таким образом, приоритетное уст ройство обеспечивает выделение на обслуживание самого приоритетного запроса и одинаковые условия перезаписи данных для анализа в.узлы и блоки устройства как в начале его работы, так и в последующих циклах Таким образом, применение в устройстве элемента ИЛИ, блока сравнения приоритетных кодов, состоящего из элементов -И, ИЛИ и ИЛИ-НЕ, а в каждом канале элемента ИЛИ груп пы элементов И и регистра хранения приоритета выгодно отличает предлагаемое устройство от известного, так как позволяет повысить быстродействие и достоверность выходной информации. Формула изобретения 1. Многоканальное приоритетное устройство, содержащее блок управления, первый элемент ИЛИ, N канало (где N - число источников -заявок), каждый из которых содержит регистр приоритета, регистр заявок, узел анализа заявок, две группы элементов И и выходной регистр, причем вы ход первого элемента ИЛИ соединен с выходом конца цикла устройства и с входом сброса блока управления, вход пуска которого соединен с входом пуска устройства, сигнальный вход блока управления соединен с входом ответа абонента устройства, информационные входы регистра заявок каждого канала соединеньг с входами соответствующей группы входов заявок устройства, входы регистра приоритета соединены с входами соответствующей группы входов приоритета устройства, выходы регистра заявок каждого канала соединены с группой информационных входов блока управления и с первой группой входов узла анализа заявок своего канала, выходы узла анализа заявок каждого канала соединены с первыми входами соответствующих элементов И первой группы своего канала, выходы элементов И первой группы каждого канала соединены с соответствующими входами сброса регистра заявок и с информационными входами выходного регистра, выходы которого соединены с соответствующей группой информационных выходов устройства, вход сброса узла анализа заявок каждого канала соединен с первым выходом блока управления, каждый выход регистра приоритета каждого канала соединен с первым входомсоответ-. ствующего элемента И второй группы, отличающееся тем, что, с целью повышения быстродействия и надежности, устройство содержит второй элемент ИЛИ, блок сравнения, а в каждом канале элемент ИЛИ, буферный регистр, причем управляющий вход блока сравнения соединен с вторым выходом блока управления, первый и второй входы второго элемента ИЛИ соединены соответственно с входом пуска и ответа абонента устройствау вторые .входы элементов И второй группы каждого канала соединены с первьзм выходом блока управления,- третьи входы элементов И второй группы каждого канала соединены с выходом элемента ИЛИ своего.канала, входы элемента ИЛИ каждого канала соединены с выходами регистра заявок своего канала, выходы элементов И второй группы каждого канала соединены с информационными входами буферного.регистра своего канала, прямые и инверсные разрядные выходы- буферного регистра каждого канала соединены с соответствующими группами входов блока сравнения, вторые входы элементов И первой группы каждого канала соединены с соответствующим выходом .блока сравнения, вторая группа входов узла анализа заявок каждого канала соединена с выходами элементов И первой группы своего канала, установочный вход узла анализа заявок, вход сброса буферного регистра.и вход сброса .выходного регистра соединены с выходом второго элемента ИЛИ. , . 2. Устройство по п. 1, о т л и чающееся тем, что в нем блок управления содержит четыре элеЧ мента ИЛИ, два элемента задержки, три триггера, элемент И, причем первый вход первого элемента ИЛИ соединен с входом сброса блока управления, второй вход первого элемента ИЛИ, вход первого элемента задержки и первый вход второго элемента ИЛИ соединены с входом пуска блока управления, выход первого элемента ИЛИ соединен с нулевыми входами первого и второго триггеров, выход первого триггера соединен с первым выходом блока, с вторым входом второго элемента ИЛИ и через второй элемент задержки - с третьим входом первого элемента ИЛИ и единичным входом второго триггера, единичный выход которого соединен с вторым выходом блока, выход первого элемента задержки соединен с первым входом третьего элемента ИЛИ, выход которого соединен с единичным входом Третьего триггера, единичный выход которого соединен с первым входом элемента И, выход которого соединен с единичным входом первого триггера, второй вход элемента И соединен- с выходом четвертого .элемента ИЛИ входы которого соединены с группой информационных входов блока, нулевой вход третьего триггера соединен с выходом второго элемента ИЛИ вто рой вход третьего элемента ИЛИ соединен с сигнальным входом блока, вым ход второго триггера соединен с вторым выходом блика.

3, Устройство по п. 1, отличаю щ е е с я тем, что в нем

Узел анализа заявок содержит ре гистр индикации, каждый разряд которого состоит из триггера, первого и второго элементов ИЛИ, элемента. И-;- причем в каждом разряде еди5 яичный выход триггера соединен с соответствующим выходом узла и с первым входом первого элемента ИЛИ, второй вход которого соединен с нулевым входом триггера и с выходом

0 второго элемента ИЛИ, единичный вход триггера соеди11ен о выходом элемента И, первый вход которого соединен с соответствующим входом первой группы входов узла, второй вход

5 элемента И соединен с установочным входом узла, первый и второй входы второго элемента ИЛИ соединены соответственно с входом сброса узла и с соответствхпощим входом второй группы входов узла.

Источники информации, принятые во внимание при экспертизе

e 1. Авторское свидетельство СССР № 475622, кл. G Об F 9/46, 1973,

2. Авторское свидетельство СССР № 645159,кл. G 06 F 9/46,1979 (прототип) .

фг/. 1

Фие.г

fSbfXOd

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство динамического приоритета | 1980 |

|

SU868760A1 |

| Устройство приоритета для выбора групповых заявок | 1985 |

|

SU1319030A1 |

| Устройство приоритета | 1981 |

|

SU976446A1 |

| Устройство для группового обслуживания запросов | 1984 |

|

SU1196868A1 |

| Устройство приоритетного обслуживания каналов | 1989 |

|

SU1702369A1 |

| Устройство приоритета | 1984 |

|

SU1254483A2 |

| Устройство смешанного приоритета | 1989 |

|

SU1619272A1 |

| Устройство для приоритетного обслуживания заявок | 1989 |

|

SU1709313A1 |

f /nf/f ffv ffe/nen fav. ffjretf , Sfoff

fS f

fS f4

0t/g. J

fff /# г/уу/ &

Авторы

Даты

1982-11-07—Публикация

1981-04-13—Подача