(54) УСРЕДНЯЮЩИЙ ЧАСТОТОМЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1977 |

|

SU978063A1 |

| Аналого-цифровой преобразователь сдвига фаз | 1981 |

|

SU955519A2 |

| Цифровой следящий частотомер | 1983 |

|

SU1241143A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Цифровой частотомер | 1985 |

|

SU1247771A1 |

| Цифровой экстраполирующий частотомер | 1974 |

|

SU568903A1 |

| Цифровой фазометр | 1979 |

|

SU788025A1 |

| Низкочастотный частотомер | 1982 |

|

SU1093988A1 |

| Цифровой следящий частотомер | 1980 |

|

SU892335A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА-КОД | 1972 |

|

SU428548A1 |

Изобретение относится к измерению и преобразованию информации и может быть использовано для централизованного контроля параметров зне гообъектов. Наиболее близок к настоящему изо ретению цифровой частотомер, содерж щий двоичный умножитель, два элемента ИЛИ, два триггера управления, генераторы образцовой и тактовой частот, элемент задержки, управляемый делитель и делитель JНедостатком его является низкая ность измерений при отклонении изме ряемой частоты от заданного диапазо на, а также невозможность получения среднего значения частоты за большой интервал времени. Целью изобретения является повьш ние точности измерений и расширение функциональных возможностей схе мы. Поставленная цель достигается тем, что в усредняющий частотомер. содержащий последовательно соединенные первые ключ и триггер управления, выход которого подключен к первому входу второго ключа, второй вход которого соединен с вькодом генератора образцовой частоты, выход второго ключа подключен к первым входам двоичного умножителя и первого элемента ИЛИ, выход которого через делитель подключен к первому входу второго триггера управления, второй вход которого соединен с выходом первого триггера управления, а выход с первым входом третьего ключа, второй вход которого подключен к выходу генератора тактовой частоты, выход третьего ключа соединен со вторым входом первого элемента ИЛИ и первым входом управляемого делителя, второй вход которого подключен к первому выходу двоичного умножителя, второй выход которого через прследовательно соединенные второй элемент ИЛИ и элемент задержки подключей к третьему входу первого элемента ИЛИ, выход управляемого делителя соединен со вторым входом двоичного умножителя, введены последовательно соединенные двоичный разностный счетчик, управляемый реверсивный делитель и реверсивньш двоичный счетчик, а также блок переноса и индикатор, вход которого подключен к первому выходу реверсивного двоичного счетчика, второй выход которого через блок переноса соединен с первым входом двоичного разностного счетчика, второй вход которого соединен с выходом управляемого делителя.

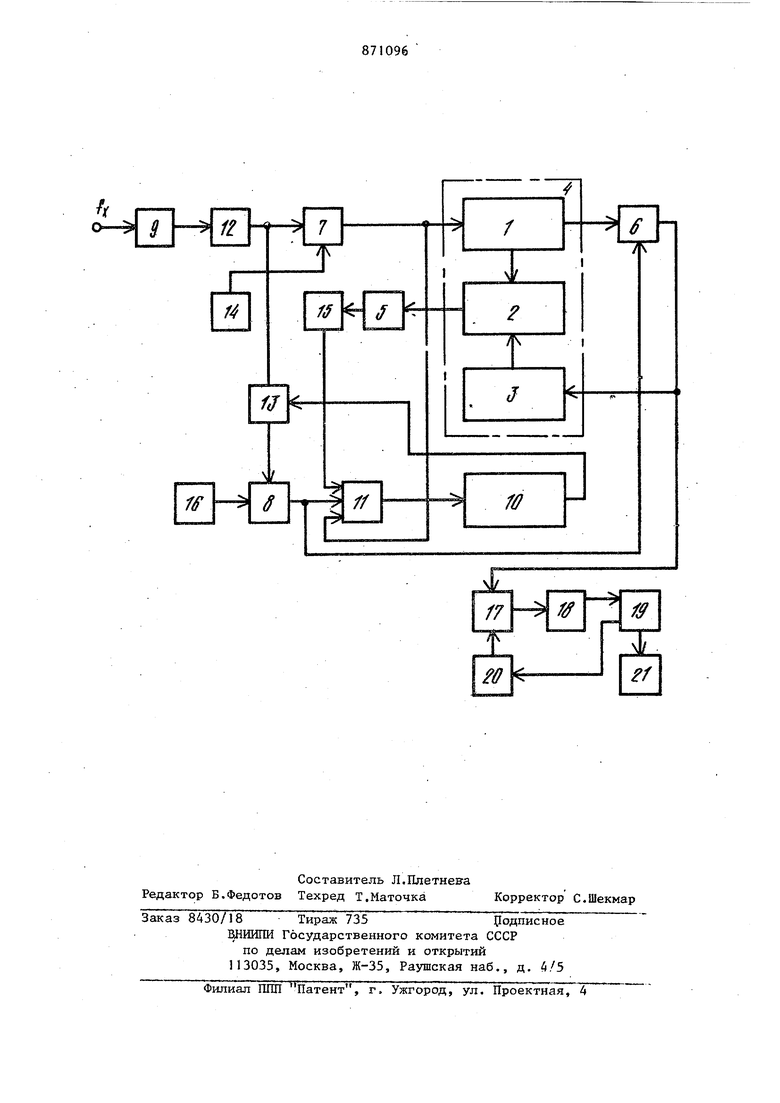

На чертеже представлена структурная Электрическая схема усредняющего частотомера.

Частотомер содержит счетчик 1 периода, блок элементов 2 И, счетчик 3 частотыj которые представляют со- бой двоичный умножитель 4, элемент 5 ИЛИ, управляемый делитель 6, ключи 7-9, делитель 10, элемент 11 ИЛИ, триггеры 12, 13 управления, генерато 14 образцовой частоты, элемент 15 задержки, генератор 16 тактовой частоты, двоичный разностньй счетчик

17,управляемый реверсивный делитель

18,реверсивный двоичный счетчик 19 текущего среднего значения частоты, блок 20 переноса, индикатор 21.

Устройство работает следующим образом. I

Первый этап - измерение периода.

Результат измерения - число, пропорциональное периоду измеряемой частоты, - фиксируется в счетчике 1 периода.

Триггеры 12 и 13, ключи 9 и 7, генератор 14 и счетчик 1 составляют функциональный узел, назначением которого является измерение периода. В начале каждого цикла измерения ключ 7 открьшается на время, равное периоду измеряемой частоты, и в счетчике Г фиксируется число, пропорциональное периоду измеряемой частоты.

Второй этап - преобразование числа, пропорциойального периоду измеряемой частоты, в число, пропорциональное измеряемой частоте, - состоит в делении,методом последовательного вычитания из постоянного числа значащей цифры старшего разряда числа, пропорционального периоду измеряемой частоты, причем одновременно делимое уменьшается на величину, пропорциональную весу остальных разрядов делителя. Операция деления осуществляется в управляемом делителе 6.

Триггер 13, ключ 8 и делитель 10

составляют функциональный узел, осуществляющий операцию вычитания. В начале процесса преобразования числа, пропорционального периоду, в число, пропорциональное частоте,

триггер 13 открьшает ключ 8, и на

вход делителя 10 через элемент 11 ИЛИ начинают поступать импульсы тактовой частоты. Одновременно через элемент 11 на вход делителя 10 начинают поступать импульсы с выхода элемента 5 ИЛИ.

Элемент 15 задержки предназначен для того, чтобы исключить возможность совпадения этих двух последовательностей импульсов. Как только на вход делителя 10 поступит определенное количество импульсов, выходной импульс его возвращает триггер 13 в исходное состояние, и ключ 8 закрьшается.

5 Это говорит о том, что операция вычитания, а вместе с ней и операция преобразования числа, пропорционалького периоду, в число, пропорциональное частоте, закончилось.

JJ При этом в счетчике 3 фиксируется число, пропорциональное измеряемой частоте.

На вход двоичного разностного счетчика 17 поступают импульсы, пропорциональные частоте в данном такте работы, из управляемого делителя 6.

В счетчике 17 формируется разность между средним значением частоты за предшествующие И тактов и значением . частоты в новом такте работы, которая поступает на вход управляемого реверсивного делителя 18, где происходит деление этой разности на порядковый номер такта работы устройства. С выхода делителя 18 импульсы поступают на вход реверсивного двоичного счетчика 19 и изменяют информацию о среднем текущем значении частоты, хранящуюся там,

С реверсивного двоичного счетчика 19 импульсы считьшаются и поступают в узел индикации 21, где преобразуются в двоично-десятичный код для ввода в ЭВМ и для индицирования.

5 Блок переноса 20 переносит состояние счетчика 19 текущего среднего значения в двоичный разностный счетчик 7.

Настоящее устройство выгодно отличается от известного тем, что позволяет осзтцествлять усреднение результатов измерений с одновременной индикацией промежуточных результатов усреднений, а также мгновенных значений частоты, что значительно упрощает контроль работы энергосистемы, оптимальный режим работы электрогенераторов, что ведет к экономии тошшва и безштрафовой поставке энергии потребителю.

Формула изобретения

Усреднякяций частотомер, содержащий последовательно соединенные первые ключ и триггер управления, выход ко.торого подключен к первому входу второго ключа, второй вход которого соединен с выходом генератора образцовой частоты, выход второго ключа подключен к первым входам двоичного умножителя и первого элемента ИЛИ, выход которого через делитель подключен к первому входу второго триггера управления, второй вход которого соединен с выходом первого триггера управления, а выход - с первьм входом третьего ключа, второй вход которого подключен к выходу генератора тактовой частоты,.выход третьего ключа соединен со вторым входом первого элемента Ш1Н и первым входом управляемого делителя, второй вход которого подключен к первому выходу двоичного умножителя, второй выход которого последовательно соединенные второй элемент ИЛИ и элемент задержки подключен к третьему входу первого элемента ИЛИ, выход управляемого делителя соединен со вторым входом двоичного умноямтеля, о т л и - чающийся тем, что, с целью повышения точности измерений и расширения функциональных возможностей, в него введены последовательно соединенные двоичный разностный счетчик, управляемый реверсивный делитель и реверсивный двоичный счетчик, а также блок переноса и индикатор, вход которого подключен к первому выходу реверсивного двоичного счетчика, второй выход которого через блок переноса соединен с первым входом двоичного разностного счетчика, второй вхсщ которого соединен с выходом управляемого делителя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-10-07—Публикация

1978-10-16—Подача