(54) УСТРОЙСТВО ДЙЯ ШЛЧИСЛЕНИЯ ДИАГРАММ РАЗРЕЖЕНИЯ ИНДИКАТОРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления диаграмм разрежения индикаторов | 1978 |

|

SU792264A1 |

| Устройство для вычисления параметров диаграмм, разрежения индикаторов при исследовании сердечно-сосудистой системы | 1980 |

|

SU920744A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов | 1984 |

|

SU1226488A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| Электромагнитный толщиномер | 1985 |

|

SU1268943A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1606991A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для обучения основам вычислительнй техники | 1981 |

|

SU1005156A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

. :-,.

Изобретение относится к вычислительной технике и может быть использовано для вычисления параметров яиarpeiMM разрежения индикаторов, нагфимер, при определении сердечного выброса.

Известно устройство для вычисления диаграмм разрежения индикаторов содержащее функциональный преобразователь, интегратор, два счетчика, триггер, два элемента ИЛИ, элемент И, регистр , распределитель, дешифра;тор и три группы выходов устройства,которьи«ш являются информационные выход : регистра, интегратора и одного из счетчиков l. Однако указанное уртройство обеспечивает вычисление только части общей площади под диаграммой разрежения.

Наиболее близким к предлагаемому по.ехнической сущности являетсяустройство для вычисления диаграмм разрежения индикаторов, содержащее функциональный преобразователь, интегра тор, распределитель, три счетчика.два триггера, два элемента ИЛИ, эле- . мент И, регистр, дешифратор, преобразователь код - частота, два элемента 2И-ИЛИ, генератор частоты и выхода устройства., которыми являются ннфорГмациоиные выходы интегратора и йн: версный выход первого триггера/ 2j.

. Недостатком известного устройства является Мсшая инф(н мативн6сть оценки диаграмм разрежения индикаторов, т.е. в результате обработки информации, поступсиощей с выхода функционального црео азователя, вычисляют только один параметр- площадь под

10 диаграммой разрежения, ограниченную первой волной циркуляции индикатора. Более информативным параметре, который определяется по диаграмме разрежения , является среднее время цирку-15ляции индикатора, равное отношению плсэдади к значению уровня диаграммы после равномерного разведения индикатора в крови.

Цель изобретения - повышение дос20товерности.

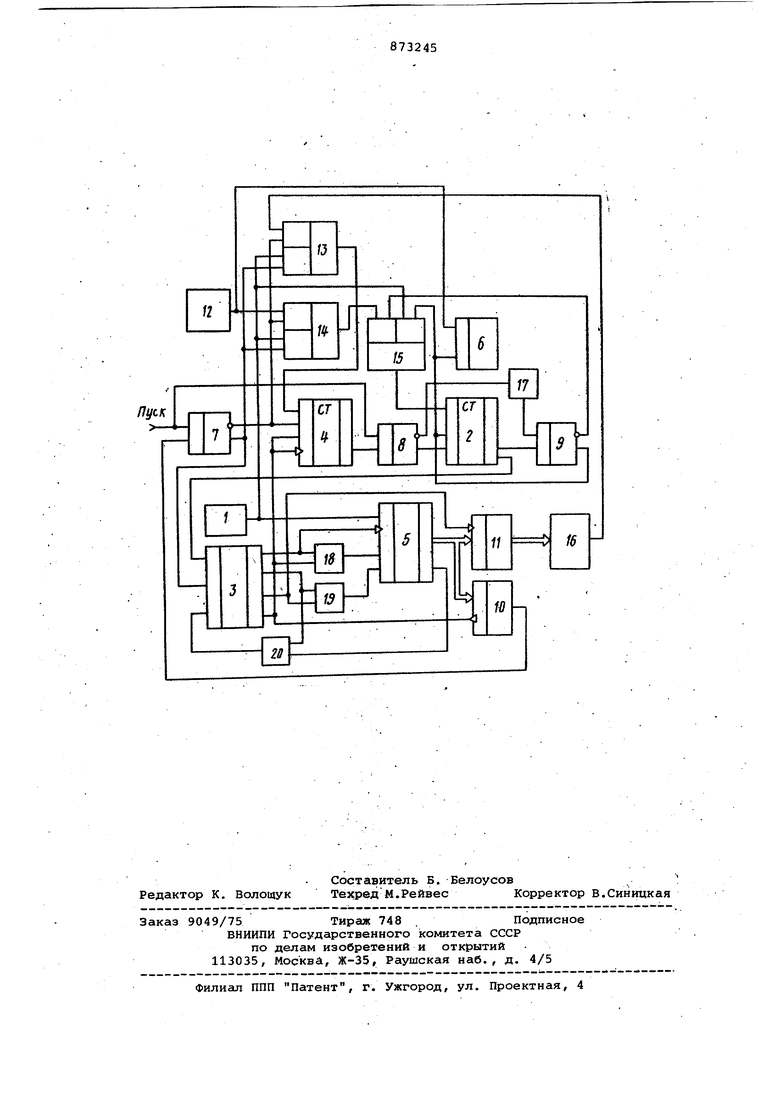

Эта цель достигается тем, что в устройство для вычисления диаграмм разрежения индикаторов, содержащее функциональный преобразователь, вы25ход которого соединен с первыми входами первого и второго элементов 2ИШ1И и первого счетчика, информсщионный выход которого соединен с первыми входами регистра и деши4« атора,

30 первый и второй триггеры, первые вхо|ды которых роединены с входом устройстаа, первый выход первого триггера соединен с первым входом интегратора, первый выход ко;торого соединен с первым входом распределителя, первый выход которого соединен с первым входом первого элемента ИЛИ и вторым входом первого счетчика, второй выход распределителя соединен с первыми входами элемента И и второго эле,мента ИЛИ, выход которого соединен с третьим входом первого счетчика, выход которого чсерез элемент И соединен с вторым входом распределителя, третий выход которого соединен со вторыми входами второго элемента ИЛИ и регистра, выход которого соединен с вхо дом преобразователя код - частота, четвертый выход распределителя соеди йен с первым и вторым входами второго счетчика, вторыми входами деигафратора и первого элемента ИЛИ, выход кото рого соединен с четвертым входом пер вого счетчика, выход дешифратора сое динен с вторым входом второго триггера, первый выход которого соединен со вторыми входами первого и второго элементов 2И-ИЛИ и третьим входом второго счетчика, выход которого сое динен с вторым входом первого триггера, в.торой выход второго триггера соединен с третьим входом распределителя и третьими входами первого и вт рого элементов 2И-ИЛИ, четвертые вхо ды которых соединены соответственно с выходами преобразователя код - час тота и генератора и выход первого элемента 2И-ИЛИ соединен с четвертым входом второго счетчика, третий счет чик, дополнительно введены элемент задержки, третий триггер и третий элемент 2И-ИЛИ, причем второй выход первого триггера соединен с входом схекЁ задержки, выход которой соединен с первым входом третьего триггера, второй вход которого соединен с вторым выходом интегратора, второй вход которого соединен с первым выходом третьего триггера и первыми вх дами третьего элемента 2И-ИЛИ и трет его счетчика, вторые входы которых соединены соответственно с выходами функционального преобразователя и генератора, второй выход третьего триггера соединен с третьим входом уретьего элемента 2И-ИЛИ, четвертый вход которого сосздинен с выходом вто рого элемента 2И-ИЛИ, а выход - с третьим входом интегратора. На чертеже показана блок-схема предлагаемого устройства. Устройство додержит функциональный преобразователь 1, выцгшщий элек трический сигнал в вида частоты импульсов , пропорциональный амплитуде диагргилмы разрежения, интегратор 2, распределитель 3, счетчики 4-6, триггеры 7-9/ дешифратор 10, регистр 11, .генератор 12, элементы 2И-ИЛИ 13-15, преобразователь 16 код - частота, задержки 17, элементы ИЛИ 18 и 19, элемент И 20. Устройство работает следующим образом. В исходном состоянии интегратор 2, счетчики 4-6, триггеры 7-9, регистр 11 и распределитель 3 установлены в нулевое состояние. Пуск устройства Ьсуществляется подачей импульса на единичные входы триггеров 7 и 8, которые при этом устанавливаются в единдчное состояние и открывают элементй 2И-ИЛИ 13 и 14, распределитель 3 и интегратор 2. Последний начинает интегрировать входной сигнал путбм счета числа импульсов, поступающих на его счетный вход с выхода первого элемента 2И-ИЛИ 14. Первый цикл работы устройства начинается при поступлении на вход интегратора 2 числа импульсов, равного AN, когда на его импульсном выходе возникает первый импульсный сигнал, запускающий распределитель 3. Дгшее на первом выходе распределителя временно появляется разрешающий потенциал, поступающий через элемент ИЛИ 18 на управляющий вход сложения счетчика 5, который за это время зарегистрирует среднюю частоту импульсов, поступающих на его вход с вьасода функционального преобразователя 1. При поступлении очередных AN импульсов на вход интегратора 2 сигнал с выхода последнего запускает распределитель 3, на втором выходе которого появляется временно разрешающий потенциал, поступающий через элемент ИЛИ 19 на управляющий вход вычитания счетчика 5. При этом из первого значения средней частоты импульсов вычитается второе значение средней частоты импульсов. Поскольку на участке подъема амплитуды диаграммл разрежения последующее значение средней частоты импульсоб всегда больше предьщущего, то возникающий на выходе переноса счетчика 5 импульс поступает через открытый во втором такте элемент И 20 на установочный вход расгцределителя 3, устанавливая его в исходное состояние. Аналогичным образом йроисходит работа и во всех последующих циклах н подъе1 е диаграммы разрежения, когда каждый цикл сравнения содержит два такта измерения. После достижения- максимального значения на диаграмме разрежения имеется участок, где средняя частота им- . пульсов, т.е. усредненное значение амплитуды диаграмкы разрежения, начинает уме11ьш 1ться по экспоненте n(t)« n(to) (1) и распределитель 3 начинает работать циклически по четыре такта в каяздом цикле. При этом в первом такте счетчик 5 работает на сложение, во втором и тоетьем - на вывьиитание и в четвертом - снова на сложение, в конце четвертого такта каждого цикла проверяется справедливость равенства п () - п (t ) - п (1) + +n(t.)Q (2) путем подключения дешиф ратора 10 к счетчику 5. Так как в на чальный период после достижения максимума амплитуда диаграммы разрежения уменьшается не строго по экспоне циальной зависимости (1), то равенство (2) не соблюдается, сигнал на выходе дешифратора 10 отсутствует и интегратор 2 по-прежнему продолжает считать сумму всех импульсов, кото,рые поступают с функционального преобразователя 1 через элемент 2ИИЛИ 14. На участке экспоненциальной завис мости средней частоты импульсов о времени равенство (2) соблюдается, поэтому дешифратор 10 в очереднсм цикле, а именно в конце четвертого такта, выдает сигнал, который поступает на вход установки в нулевое состояние триггера 7, в результате чего элементы 2И-Ш1И 13 и 14 закрыва ются по первым управляющим входам и открываются по вторым управляющим .входам. К этому моменту времени интегратор 2 зарегистрирует суммарное число импульсов, равное f п (t)dlt, поступакядих на его вход sS время. . от начала интегрирования до момента достижения равенства (2), а регистр 11 - разность средних частот nCt)(Ц)-KAN, которая перезаписывается из счётчика 5 в регистр 11 в начале третьего такта, когда передний фронт разреша1011{его потенциала с выхода рас пределителя 3. поступает на вход регистра 11. В счетчике 4 регистрирует ся число n(t-j), которое равно средней частоте импульса в четвертом так те, когда разрешающий потенциал р вы хода распределителя поступает на вход счетчика 4. На выходе преобразца ател код - частота 16, коэффициент .преоб-. разования которого устанавливают рав ным тТм Д Ь - целое положительное , „ : .. 40 число, появляется частота ff , которая через открытый элемент 2И-1ШИ 13 начинает поступать на вход счетчика 4. С этого момента счет чик работает на вычитание. Одновремен но частота fn 10 с выхода генерато ра 12 через открытый элемент 2И-Ш1И 14 начинает поступать на вход интегратора 2, появляющиеся импул сы на выходе которого уже не запускают рас пределитель 3, поскольку последний закрыт по управляющему входу. Интегратор 2 считает импульсы частотой f. в течение времени, ;ПОКа на выходе переноса счетчика4 цоявляется сигнал. Данный сигнеш устанавливает триггер 8 в нулевое состояние Это время определяется числом nXtj), которое было зарегистрировано счет чиком 4 и ч&стотой f , поступающей на вход счетчика 4, и равноий,) / f .. За это время интегратор 2 к числу импульсов n(t)dt досчитывает число, Vi(-fc-i) .-gtCt) «(t) равное fт.е. содержимое интегратора увеличива-; ется на величину площади под экстраполируемой частью диаграмма разрежения и станет равным Nogm-lnC-t)t-«- В момент установки триггера 8 в нулевое состояние потенциал с его инверсного выхода запускает элемент задержки 17, на выходе которого появляется сигнал, через время t задержки, 10-15 мин, в течение которого индикатор равномерно размещивается в крови и амплитуда диаграммы разрежения достигает постоянного уровня. При этом средняя частота импульсов на вьрсоде функционального преобразователя 1 также становится постоянной по величине, равное п(tat. золержии Импульсом с выхода элемента задёрйски 17 триггер 9 устанавливается в едини;яное состояние, s результате чего одновременно открываются интегратор 2, элемент 2И-ИЛИ 15 и счетчик 6, который начинает считать импульсы генератора 12 частоты fj. . При этом на счетный вход интегратора начинают поступать с выхода функционального преобразователя 1 через элемент 2И-ИЛИ 15 импульсы частотой равн которые вычитаются из числа МОРЩ- В момент полного вычитания числа Njjgy. в интеграторе 2 на его выходе переноса появляется импульс, который устанавливает триггер 9 в Hyjftвое состояние, прекращая регистрацию частоты . Время-, в течение которого происходит полное опорожнение интегратора, определяется равенством .BH- 1 Известно, что отношение площади, ограниченной первой волной циркуляции индикатора, к постоянному уровню амплитуды диаграммы разрежения после равномерного разведения индикатора в крови равно среднему времени цирку.ляции индикатора, которое в предложенном устройстве регистрирует счетчик б с точностью .±10 с. Таким образом, предлагаемое изобретение обеспечивает определение не только площади-под диагргиимой разрежения, но и среднего времени циркуляции индикатора, которое является более информативным параметром, так как оно равно времени центральной циркуляции крови и используется в качестве самостоятельного показателя при оценке производительности- сердца. Среднее время циркуля;2ии индикатора является достаточно точным показатеем, позволяющим оценивать степень недостаточности кровообращения, разичать одышку сердечного происхожце ния от одышки при легочных заболеваниях. Наиболее.выраженное увеличение этого показателя наблюдается при застое крови в малом круге кровообращения. Отсутствие увеличения этого показателя при сердечной недостаточности наблщцается у больных с анемией, тиреотоксикозом, лихорадкой, при которых ускоряется кровоток. Формула изобретения Устройство для вычисления диаграмм разрежения индикаторов, содержащее функциональный преобразователь, выхбд которого соединен с первыми входами первого и второго элементов 2И-ИЛИ и первого счетчика, информационный выход которого.соединен с первыми входами регистра и дешифратора первый и второй триггеры, первые входы которых соединены со входом устройства, первый выход первого триггера соединен с первым входом интегратора, первый выход которого соединен с пер,вым входом распределителя, первый выход которого соединен с первым вхо дом первого элемента ИЛИ и вторым входом первого счетчика, второй выход распред елителя соединен с первыми вх дгили элемента И и второго элемента ИЛИ, выход которого соединен с треть им входом первого счетчика, выход ко торого через элемент И соединен с вт рым входом распределителя, третий вы ход которого соединен со вторыми вхо дами второго элемента ИЛИ и регистра, выход которого соединен с входом преобразователя код - частота, четвертый выход расщ еделителя соединен с первБКм и вторым входакт второго счетчика, входами дешифратора и первого элемента ИЛИ, выход кот рого соединен с четвертым входом пер счетчика, выход дешифратора соединен с. вторым входом второго триггера, первый выход которого соединен со вторыми входами первого и второго элементов 2И-ИЛИ и третьим входом второго счетчика, выход которого соединен с вторым входом первого триггера второй выход второго триггера соединен сс третьим входом распределителя и ; третьими входами первого и второго элементов 2И-ИЛИ, четвертые входы которых соединены соответственно с вы- . ходами преобразователя код - частота и генератора, а; выход первого элемента 2И-ИЛИ соединен с четвертым входом второго счетчика, третий счетчик, отличающееся тем, что, с целью повышения достоверности, в него введены элемент задержки, третий триггер и третий элемент 2И-ИЛИ, причем второй выход первого триггера соединен через элемент задержки с первым входом третьего триггера, второй вход которого соединен с вторым выходом интегратора, второй вход кото рого соединен с первым выходом третьего триггера и первыми входами третьего элемента 2И-Ш1И и третьего счетчика, вторые входы которых соединены соответственно с выходами функционального преобразователя и генератора, второй выход третьего триггера соединен с третьим входом третьего элемента 2И-ИЛИ, четвертый вход которого соединен с выходом второго элемента 2И-ИЛИ, а выход - с третьим входом ининтегратора. . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 2547355/18-24, кл. G 06 F 15/52, 1977. 2.Авторское свидетельство СССР по заявке № 2702909/18-24, кл. G Об F 15/52, 1978 (прототип).

Авторы

Даты

1981-10-15—Публикация

1979-08-14—Подача