(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДИАГРАММ РАЗРЕЖЕНИЯ ИНДИКАТОЮВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления диаграмм разрежения индикаторов | 1979 |

|

SU873245A1 |

| Устройство для вычисления параметров диаграмм, разрежения индикаторов при исследовании сердечно-сосудистой системы | 1980 |

|

SU920744A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов | 1984 |

|

SU1226488A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Электромагнитный толщиномер | 1985 |

|

SU1268943A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

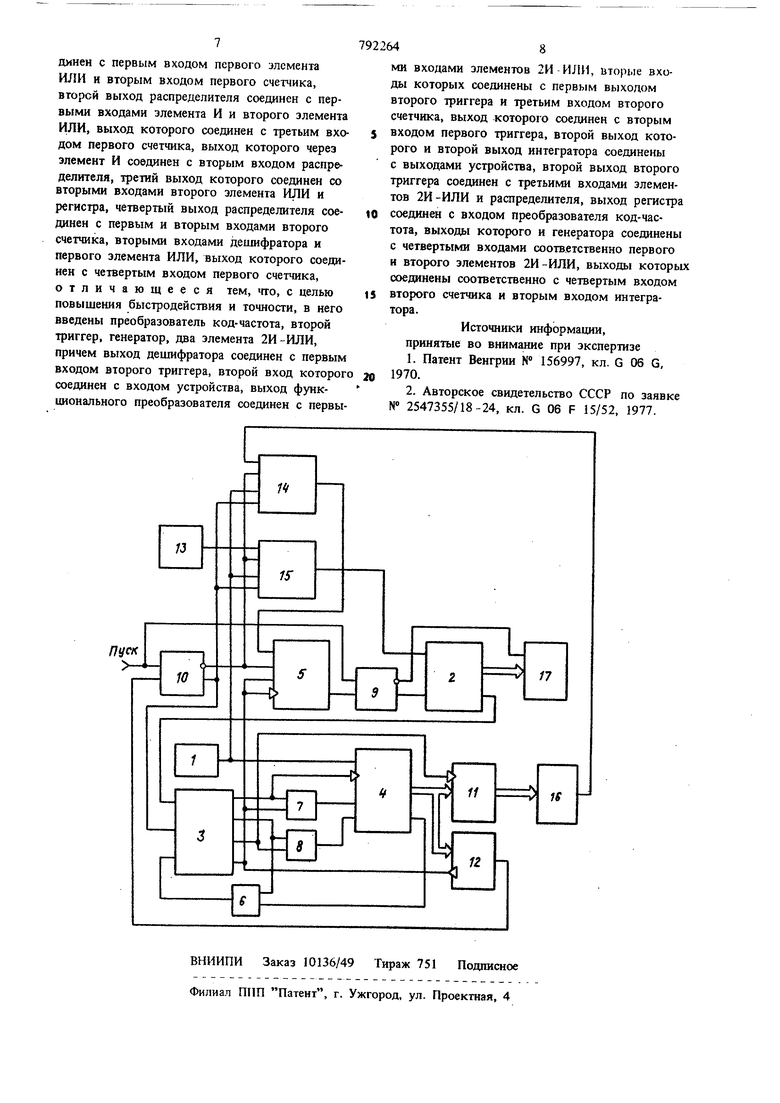

Изобретение относится к вычислительной технике и может быть использовано для вычисления площади диаграмм разрежения как радиоактивных, так и красочных индикаторов, например, при определении производительности сердца. Известна целевая вычислительная машина для вычисления диаграмм разрежения, обладаю щих рециркуляционным участком, содержащая функциональный преобразователь, усилитель, интегратор, датчик напряжения (вольтметр), логарифмирующий блок, блок дифференцирова ния, устройство для определения максимального напряжения, блок управления и три группы выходов. Однако указанная целевая вычислительная машина не позволяет вычислить диаграмм разрежения радиоактивных индикаторов 1. Наиболее близким по сущности техническим решением является устройство для вычисления диаграмм разрежения радиоактивных индикаторов, содержащее функциональный преобразователь, интегратор, два счетчика, триггер, два элемента ИЛИ, элемент И, регистр, распределитель, дешифратор 2. В известном устройстве интегратор суммирует число импульсов, которые поступают на его счетный вход от момента пуска устройства (t 0) до момента заверщения (t 1з) поиска зкспонекдиального зчастка на нисходящей ветви диаграммы разрежения, когда ее амплитуда уменьшается по экспоненциальной зависимости:H(:) n(-fco)) для t3 .(О где п() - значение средней частоты 11мпульсон вначале (t t,) экспоненниального участка; К - логарифмический декремент затухания. Поиск экспоненциального участка осуществляется путем проверки в реверсивном счетчике равенства: n(to) - n(t) -n(t2) ) О, (2) где n(tc), n(t), nCtj) и n(tj) - значения средней частоты илятульсов в моменты времени to, t, 12И tj , соответствующие появлению первого, второго, третьего и четвертого импульсов на импульсном выходе интегратора, который в промежутках между этими импульсами накапливает одинаковое количество импульсов;uN - in.(todt --(i)dt - Г h(t)at (Ч Недостатком известного устройства является то, что Б результате оценки диаграммы разрежения вычисляется не общая площадь под диаграммой разрежения, а только первая часть этой площади, равная значению/ n(t)dt, которое фиксируется в интеграторе к моменту остановки устройства. Для вычисления второй площади под экстралолируемой частью диаграммы разрежения индикатора, равной % необходимо вначале вычислить логарифмичес кий декремент затухания К из величины KAN, которая фиксируется, в регистре, а затем разделить величину п(1з), зарегистрированную счетчиком, на К. В заключение необходимо выполнить операцию суммирования двух величин: .-N о14 Чтобы осуществить указанные операции, тре буется специальное устройство для решения конечного уравнения (4). Целью изобретения является повышение быстродействия и точности. Указанная цель достигается тем, что в устройство для вычисления диаграмм разрежения индикаторов, содержащее функциональный преобразователь, выход которого соединен с первым входом первого счетчика, информационный выход которого соединен с первыми входами регистра и дешифратора, первый триггер, первый вход которого соединен с входом устройства, первый выход первого три гера соединен с первым входом интегратора, первый выход которого соединен с первым входом распределителя, первый выход которо соединен с первым входом первого элемента ИЛИ и вторым входом первого счетчика, вто рой выхбд распределителя соединен с первыми входами элемента И и второго элемента ИЛИ, выход которого соединен с третьим входом первого счетчика, выход которого чер элемент И. соединен с вторым входом распределителя, третий выход которого соединен со вторыми входами второго элемента ИЛИ и регистра, четвертый выход распределителя соединен с первым и вторым входами второг счетчика, вторыми входами дешифратора и первого элемента ИЛИ, выход которого соеди нен с четвертым входом первого счетчика. 4 ведены преобразователь код частота, второй риггер, генератор, два злемента 2И ИЛИ, ричем выход дешифратора соединен с первым ходом второго триггера, второй вход которого оединен с входом устройства, выход функционального преобразователя соединен с первыми входами элементов 2И - ИЛИ, вторые входы которых соединены с первым выходом второго триггера и третьим входом второго счетчика, выход которого соединен с вторым входом первого триггера, второй выход которого и второй выход интегратора соединены с выходами устройства, второй выход второго триггера соединен с третьими входами элементов 2И-ИЛИ и распределителя, выход регистра соединен с входом преобразователя код частота, выходы которого и генератора соединены с четвертыми входами соответственно первого и второго элементов 2И -ИЛИ, выходы которых соединены соответственно с четвертым входом второго счетчика и вторым входом интегратора. Блок-схема устройства приведена на чер1еже. Устройство содержит функциональный преобразователь 1, интегратор 2, распределитель 3, счетчики 4, 5, элемент И 6, элементы ИЛИ 7, 8, триггеры 9, 10, регистр И, дешифратор 12, генератор 13, элементы 2И-ИЛИ J4, 15, преобразователь 16 код - частота, индикатор 17. Устройство работает следующим образом. В исходном состоянии интегратор 2, счетчики 4 и 5, триггеры 9 и 10, регистр 11 и распределитель 3 установлены в нулевое состояние. Пуск устройства осуществляется подачей импульса на соответствующие входа триггеров 9 и 10, которые при этом устанавливаются в единичное состояние и открывают элементы 2И-ИЛИ 14 и 15, распределитель 3 и интегратор 2. Последний начинает интегрировать входной сигнал путем счета числа импульсов, поступающих на его вход с выхода элемента 2И-ИЛИ 15. Первый цикл работы устройства начинается при поступлении на вход интегратора 2 числа импульсов, равного А N, когда на его вьгходе возникает первый импульс, запускающий раепреде Л1п;ель 3. Далее с выхода распределителя временно появляется разрешающий потенциал, поступающий через элемент ИЛИ 7 на соответствующий вход счетчика 4, который за это время зарегистрирует среднюю частоту импульсов, поступающих на его вход с выхода функционального преобразователя 1. При поступлении очередных д N импульсов на вход интегратора 2 сигнал с выхода последнего запускает распределитель 3, на соответствующем выходе которого появляется временно разрешающий потенциал, поступающий через элемент 5 ИЛИ 8 на соответствующий вход счетчика 5. При этом из первого значения средней частот импульсов вычитается второе значение средней частоты импульсов. Поскольку на участке подъема амплитуды диаграммы разрежения последующее значение средней частоты имnjTibcoB всегда больще предыдущего, то возникающий на выходе счетчика 4 импульс по.ступает через открытый во втором такте элемент И 6 на вход распределителя 3, устанавливая его в исходное состояние. Аналогичным образом это происходит и во всех последующих циклах на подъеме диаграммы разрежения, когда каждый цикл срав нения содержит два такта измерения. После достижения максимального значения средняя частота импульсов, т.е. усредненное значение амплитуды диаграммы разрежения, начинает уменьщаться, распределитель 3 начина ет работать циклически по четыре такта в каждом цикле. При этом в первом такте счетчик 4 работает на сложение, во втором и третьем - на вычитание и в четвертом снова на сложение. В конце четвертого такта каждого цикла проверяется справедливость равенства (2) путем подключения депшфратора 12 к счетчику Так как в первый период после достижения максимума амплитуда диаграммы разрежения уменьщается не по экспоненциальной зависимости, то равенство (2) не соблюдается, сигна на выходе дещифратора 12 отсутствует и интегратор 2 по-прежнему продолжает считать сумму всех импульсов, которые поступают с функционального преобразователя 1 через элемент 2И-ИЛИ 15. На участке экспоненциальной зависимости средней частоты импульсов от времени равенство (2) соблюдается, поэтому дешифратор 12 в очередном цикле, а именно в конце четвертого такта, выдает сигнал, который поступает на соответствующий вход триггера 10, в резул тате чего элементы 2И -ИЛИ 14 и 15 меняют свое состояние. К этому моменту времени интегратор 2 зарегистрирует суммарное число импульсов, равное j n(t)dt, поступающнх на его вход за время °от начала интегрирования до момента достинсения равенства (2), а регистр 11 - разность средних частот n(to) n(t) К- ДМ, которая перезаписывается из счетчика 4 в регистр И в начале третьего такта, когда передний фронт разрешающего потенциала с выхода распределитепя 3 поступает на вход регистра 11. В счетчике 5 регистрируется число n{t2), равное средней частоте импульсов в четвертом такте, когда разрешающий потенциал с выхода распределителя поступает на соответствующий вход счетчика 5. На пыходе преобразователя 16, 4 коэффициент преобразования которого уста навливают равным -|9 , появляется часто д-КдЫ которая через открытый по второму управляющему входу элемент 2И-ИЛИ 14 начинает поступать на вход счетчика 5. С этого момента счетчик 5 работает на вычитание. Одновременно частота fj 10 с выхода генератора 13 через открытый по второму управляющему входу элемент 2И -ИЛИ 15 начинает поступать на вход интегратора 2, появляющиеся импульсы на выходе которого уже не запускают распределитель 3, поскольку последний закрыт. Интегратор 2 считает импульсы частотой fj в течение временн, пока на выходе счетчика 5 появляется сигнал. Данный сигнал устанавливает триггер 9 в нулевое состояние. Это время определяется числом n(t, которое было зарегистрировано счетчиком 5, и частотой f, поступающей на вход счетчика 5, и равно И (feb)- За это время интегратор 2 к числу импульсов J n(t)dt достигает число, равное .ЧМ) ЬП(ъХи(г) 2 ° 10ЬК К т.е. содержимое интегратора 2 увеличивается на величину площади под экстраполируемой частью диаграммы разрежения. При этом цифровой индикатор 17, управляющий сигнал на который поступает с выхода триггера 9, показывает величину общей площади под диаграммой разрежения. Таким образом, изобретение обеспечивает определение общей площади под диаграммой разрежения индикаторов, избегая при этом применения генератора экспоненциальной функции. Полученное значение общей площчди под диаграммой разрежения индикаторов используется для вычисления производительности сердца при диагностических исследованиях функционального состояния кровообращения. Формула изобретения Устройство дпя вычисления диаграмм разежения индикаторов, содержащее функциональый преобразователь, выход которого соединен первым входом первого счетчика, информаионный выход которого соединен с первыми ходами регистра и дешифратора, первый тригер, первый вход которого соед1тен с входом стройства, первый выход первого триггера оединен с первым входом интегратора, первый ыход которого соед1шен с первым входом аспределителя, первый выход которого сое

Авторы

Даты

1980-12-30—Публикация

1978-12-29—Подача