(54) ЛИНЕЙНОЕ ЭКСТРАЙОШРУИЯЦЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения информационных импульсов с фиксированной амплитудой на фоне узкополосной помехи | 1979 |

|

SU896765A1 |

| Устройство для автоматическойРЕгулиРОВКи уСилЕНия | 1979 |

|

SU801230A1 |

| Устройство выделения информационных импульсов с фиксированной амплитудой | 1981 |

|

SU951721A1 |

| Активное вероятностное реле | 1978 |

|

SU675602A2 |

| Устройство для автоматической регулировки усиления | 1978 |

|

SU748801A1 |

| Активное вероятностное реле | 1977 |

|

SU657632A2 |

| Устройство для оценки параметров сигналов и условиях действия помех | 1979 |

|

SU866741A1 |

| Устройство выделения информационных импульсов при наличии помех | 1982 |

|

SU1046944A1 |

| Устройство для полиномиальной оценки сигнала в условиях помех | 1990 |

|

SU1762313A1 |

| Дифференцирующее устройство | 1983 |

|

SU1092523A1 |

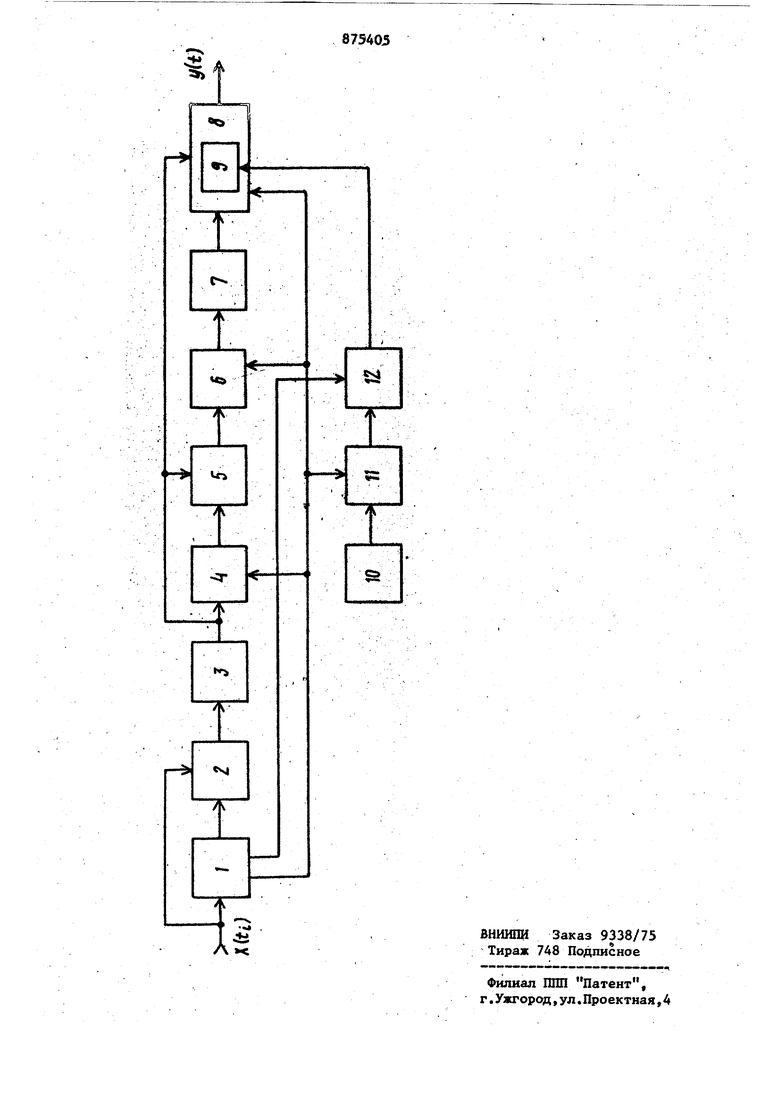

.. . . . ,; .-,. , i. , :-:.: Изобретение относится к ьпшсяиГ тельной технике и может быть использовано в инфop 4aциoнж -вычиclШTeAь . иых управляющих и телемепжческшс системах тщя восстановления неире 1ШВНОГО сигнала по его дискретньм &Т счетам, поступающим в случайные момен ты времени на фоне помех. : Известно линейное экстрапойи умщее устройство; решающее задачу восс анов ления непрерывного сигнала по отсче там, расстояние между которыми может меняться. Оно содержит последов тельно соединенные сумматор ключ; за поминающее устройство, перемнбжитель и интегратор, выход которого соеди нен с одним из входов сумматора. Иа второй вход сумматора подается входной сигнал устройства, а на второй вход перемножителя подается с блока хранения сигнал п длительности врет менного интервала между отсчетами Г 1 . Недостатком этого устройства является наличие эг ержки сигнала ka одик такт Наиболее близким по технической сущности является устройство, осуществлякацее линейное предсказание текущего значения сигнала по его дискретным значениям. Оно содержит источник опорного сигнала и последовательно соединенные первое запоминающее; устройство, блок вычитания, ключ, второе запоминающее устройство и первый интегратор, другой вход которого и . управляющий вход ключа подключены к источнику синхроимпульсов. К источнику синхроимпульсов подсоединены также входящие в состав устройства последовательно соеда1ненные второй интегратор и третье запоминающее устройство« Выход третьего запокшнающего устройства подсоединен к одному из входов первого интегратора, а один из выходов второго интегратора подсоединен к источнику опорного сигнала. 38 При восстановлении непрерыдного сигнала в обоих устройствах предполагается подача на отдельные блоки синхроимпульсов от специальных источников. Эти синхроимпульсы должны совпадать по времени с моментами при хода дискретов. Тем самым моменты прихода очередных значений сигнала считаются известными L23« Однако в информационно-вычисли- . тельных, управляющих и телеметрических системах дискретные значе1тая сиг нала передаются по каналам связи, где может отсутствовать синхронизация, либо из-за наложения помех смещаются моменты появления отсчетов, что приводит к снижеиию точности вое становления непрерыаиого сигнала, К значительному снижению точности восстановления сигналов в данных уст ройствах приводит также наложение шу ма в канале связи на значения сигнал если .не предусмотрена обработка сигнала с целью выделения информацион ного параметра сигнала из шума, Цель изобретения - повьшение точности экстраполяции в условиях помех Поставленная цель достигается тем что линейное экстраполирующее устрой ство, содержащее первый запоминающий элемент, информационнь й вход и вы . ход которого соединены с соответствукнцими входами блока вычитания, выход которого через последовательно соединенньш первый ключ и второй запоминающий элемент связан с информационным входом первого интегратора, вход установки начальных условий которого соединен с информационным вхо дом первого запоминающего элемента,, также соединенные последовательно источник опорного напряжения, второй интегратор и третий запоминающий эле мент, выход которого подключен к вхо ду регулирования постоянной времени первого интегратора, оно содержит вт рой ключ, фильтр и активное вероятностное реле, вход которого является входом устройства и соединен с инфор мационным входом второго ключа, выход которого через фильтр связан с информационным входом первого запоми нающего элемента, стробнрующий выход активного вероятностного реле соединен с управляющим входом второго ключа, выход отметки начала отсчета активного вероятностного, реле соединён с управляющим входом третьего запоминающего элементу, а выход отметки; конца отсчета - с управляющими входайи первого запоминающего элемента и первого ключа, а также с входами сброса первого и второго интеграторов , На чертеже представлена-блок-схема устройства. В состав его входят активное вероятностное реле 1, первый ключ 2, фильтр.3, первый запоминакшрсй элемент 4, блок 5 вычитания, второй ключ 6, втрройзапоминаюпщй элемент 7, интегратор 8 с управляемым резистором 9, источник опорного напряжения 10, интегратор 11, третий запоминающий элемент 12. Устройствр работает следуюпщм образом. Дискретные значения сигнала, представляющие собой последовательность импульсов малой длительности, амплитуда которых несет информацию о мгновенном значений восстанавливаемого сигнала, поступают в случайные моменты времени в смеси с помехой на вход активного вероятностного реле 1. Ак-. , тивное вероятностное реле 1 выявляет в условиях помех моменты появления и окончания информационных импульсо з и на этот промежуток времени откры- . . вает ключ 2,пропуская импульсы на вход фильтра 3, согласованного с И1 дульсным сигналом, Следоватеьно, на подключенный к фильтру 3 вход запоминающего элемента 4 и прямой вход блока 5 будет проходить только полезный сигнал - амплитуда информационног го импульса. Все остальное время ключ 2 закрыт и шум на вход блоков 4 и 5 не проходит. На инверсный вход блока 5 поступают отсчеты сигнала, -задержанные элементом 4 на один такт, так что на выходе блока 5 образуется разность значений поступившего и предшествующего отсчетов. К моменту окончания отсчета заканчивается формирование сигнала фильтром 3, одновременно активным вероятч ностным реле J подается сигнал об окончании отсчета на ключ 6, который открываясь, пропускает разность двух соседних значений сигнала на запоминающий элемент 7. Этим же сигналом сбрасывается ;интегратор I 1, который после этого интегрирует постоянное опорное напряжение источника 10 до прихода следующего отсчета. Сбросу интегратора 1 предшествует запись значения выходного напряжения в запоминающий элемент 12, где оно хранится до прихода следуиицего отсчета. Дня эторо на запоминающий элемент 12 подается сигнал о начале отсчета. Та- КИМ образом, на управляющий вход резистора $ поступает напряжение, пропорциональное времени между двумя последними Ьтсчетами, т.е. постоянг ная интегрирования интегратора 8 меняется пропорционально времени между отсчетами. . :,.-. -:. V После того как в запоминанщем элементе 7 за4а1ксирована разность пришед шего и предьщущего отсчетов происходит запись нового отсчета в -запоминающий элеме;нт 4. Для этого с pei- ; ле 1 на запоминающий элемент 4 подавt ся сигнал об окончании отсчета.. Одновременно в интеграторе: 8 происходит устайЬвка начального условия, значени которого вьшвляется фильтром 3 из ntyM Таким .образом, устройствб кадаёт на Ш11ходе напряжение, пропорсриональ ное разности вьивленных из, шума значений пришедшего и предыдущего отсчетов и обратно пропорциональное длительности интервала времени меяэду этими отсчетами в условиях помех,когда моменты появления отсчетов случайный характер и могут смеща ться под действием шума, Технико-экономический эффект заключается в повьшении точности восстановления непрерывного сигнала в ус ловия Е помех, когда отсчеты сигнала искажения шумом и моменты появления отсчетов либо предварительно неизвест ны, либо -смещаются под действием помех. Это увеличивает сферу применения устройства,. . Формула изобретения Линейное экстраполирующее устройство, содержащее первый запоминающий элемент, информационный вход и выход которого соединены с соответствующими входа14и блока вычитания, выход которого через последовательно соединенные первый ключ и второй запоминающий элемент связан с информационным входом первого янтёгратрра, вход установки начальных условий которого соединен с информационным входом первого запомип нающего элемента, а также соеданенные последовательно источник опорного напряжения , второй интегратор и третий запоминающий элемент, выход которого подключен к входу регулирования постоянной времени первого интегратора, о т л и ч а ю щ е е с я тем, что, с целью повышения точности экстраполяции в условиях помех, устройство содержит второй ключ, фильтр и активное вероятностное реле, вход которого является входом устройства и соединен с информационидм входом второго ключа, выход которого через фильтр связан с информацион№1м входом первого запоминающего элемента, стробирующий выход активного вероятностного реле соединен с управляющим входом второго ключа, выход отметки начала отсчета активного вероятностного реле соединен с управляющим входом третьего запоминающего элемента, а выход отметки конца отсчета - с управляющими входами первого запоминающего элемента и первого ключа, а также с входами сброса первого и второго интеграторов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 628500, кл. G 06 G 7/30, 1973. 2,Авторское свидетельство .СССР № 596969, кл, G 06 G 7/30, 1976 (прототип) .

Авторы

Даты

1981-10-23—Публикация

1980-02-18—Подача