1

содержит дна компаратора, объединенные первые входы которых являются первым входом формирователя прямоугольных импульсов, источник опорного напряжения, соединенный прямым и инверсным выходами с вторыми входами соответственно первого и второго компараторов, четыре D - триггера, информационные входь первых двух из которых подключены соответственно к выходам первого и второго компараторов, а прямые выходы - к информационным входам третьего и четвертого D - триггера, прямые выходы которых являются первым и вторым выходами формирователя прямоугольных импульсов, при этом входы синхронизации первого и второго, третьего и четвертого V - триггеров являютс} соответственно вторым и третьим входами формирователя прямоульньгх импульсов.

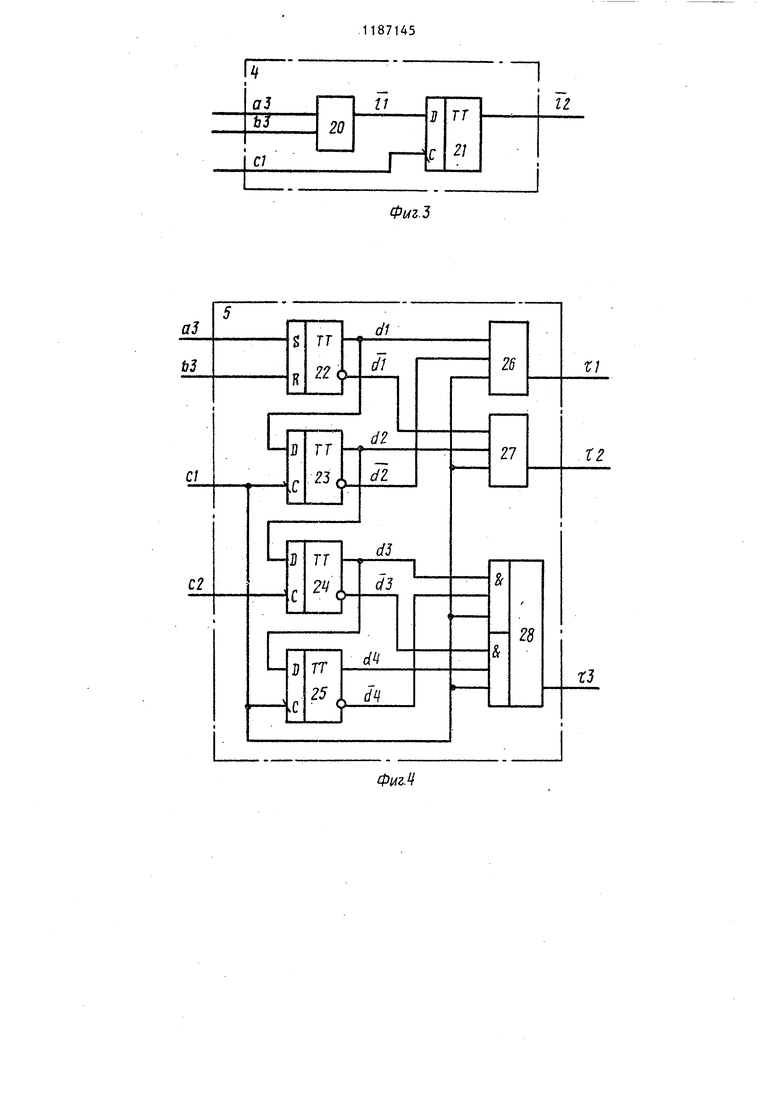

3.Устройство по п,1, отличающееся тем, что формирователь интервалов нулевой зоны содержит элемент ИЛИ, входы которого являются первым и вторым входами формиропателя интервалов нулевой зоны, D триггер, соединенный информационным входом с выходом элемента ИЛИ, вход синхронизации D - триггера является третьим входом формирователя интерва лов нулевой зоны, а выход - выходом формирователя интервалов нулевой зоны.

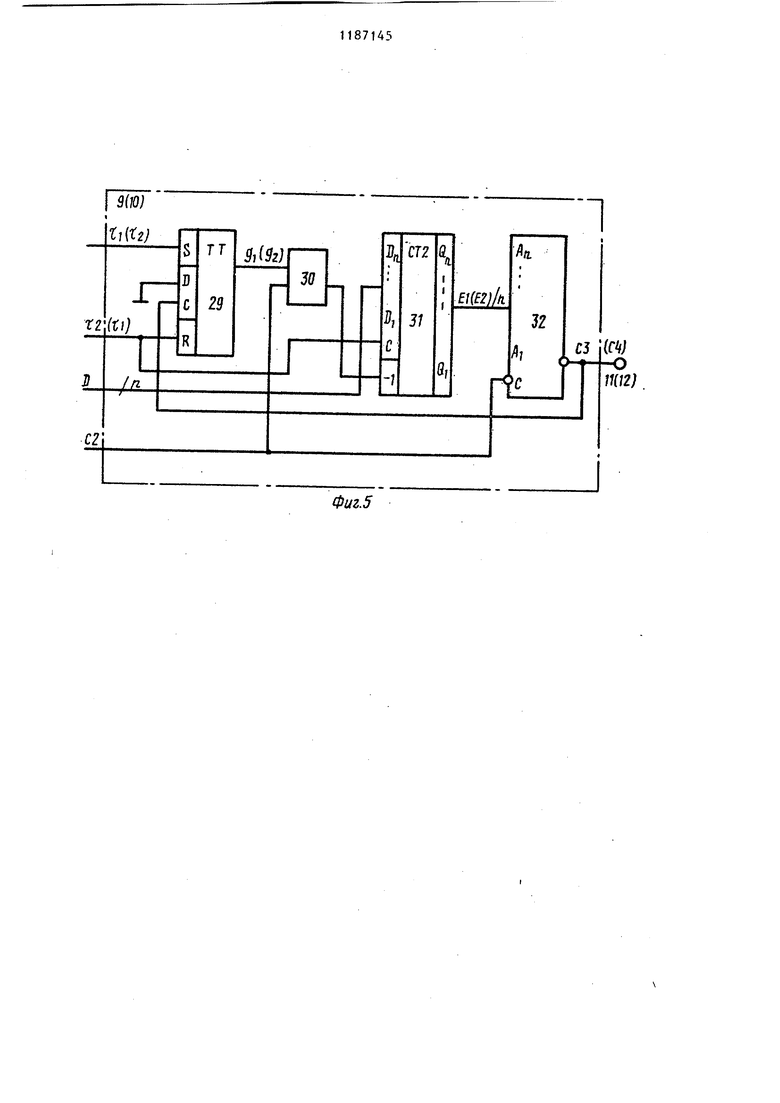

4.Устройство по п. 1, отличающееся тем, что формирователь управляющих импульсов содержит Кб- триггер, R - и 5 - входы которого являются соответственно первым и четвертым входами формирователя упраляющих импульсов, три О - триггера, причем прямые выходы первого и второго О - триггеров соединены с информационными входами соответственно второго и третьего О - триггеров,

а прямой выход R5 - триггера подключен к информационному входу первого D - триггера, первый и второй элементы ЗИ, подключенные первыми входами соответственно к прямому и инверсному выходам R5 триггера, вторыми входами - к инверсному и прямому выходам первого С - триггера, а их выходы являются вторым и третьим выходами формирователя управляющих импульсов, элемент ЗИ-ИЛИ, выход которого является первым выходом формирователя управляющих импульсов, приЭТом первый и второй вход элементов ЗИ элемента ЗИ-ИЛИ подключены соответственно к прямому и инверсному выходам второго и третьего D - триггеров, к инверсному и прямому выходам второго и третьего D - триггеров, вход синхронизации второго - триггера является третьим входом формирователя управляющих импульсов входы синхронизации первого и третьего Л - триггеров являются вторым входом формирователя управляющих импульсов и соединены с третьими входами элементов ЗИ и третьими входами элементов ЗИ элемента ЗИ-ИЛИ.

5. Устройство по п, 1, о т л ичающееся тем, что преобразователь код-временной интервал содержит D - триггер 5 и R входы установки которого являются соответственно вторым и третьим входами преобразователя код временной инт тервал, а информационный О- вход соединен с шиной нулевого потенциала элемент И, соединенный первым входом с выходом и -триггера, а второй вход элемента И является первым входом преобразователя код-временной интервал, вычитающий счетчик с предварительной записью, информационны вход которого является четвертым входом преобразователя код-временной интервал.вход записи соединен с R входом 3) -триггера, а счетный вход с выходом элемента И, дешифратор нулевого состояния счетчика, соединенный информационными входами с информационными выходами счетчика, входом стробирования - с вторым входом элемента И, а выходом - с входом синхронизации D -триггера и выходом преобразователя код-временной интервал.

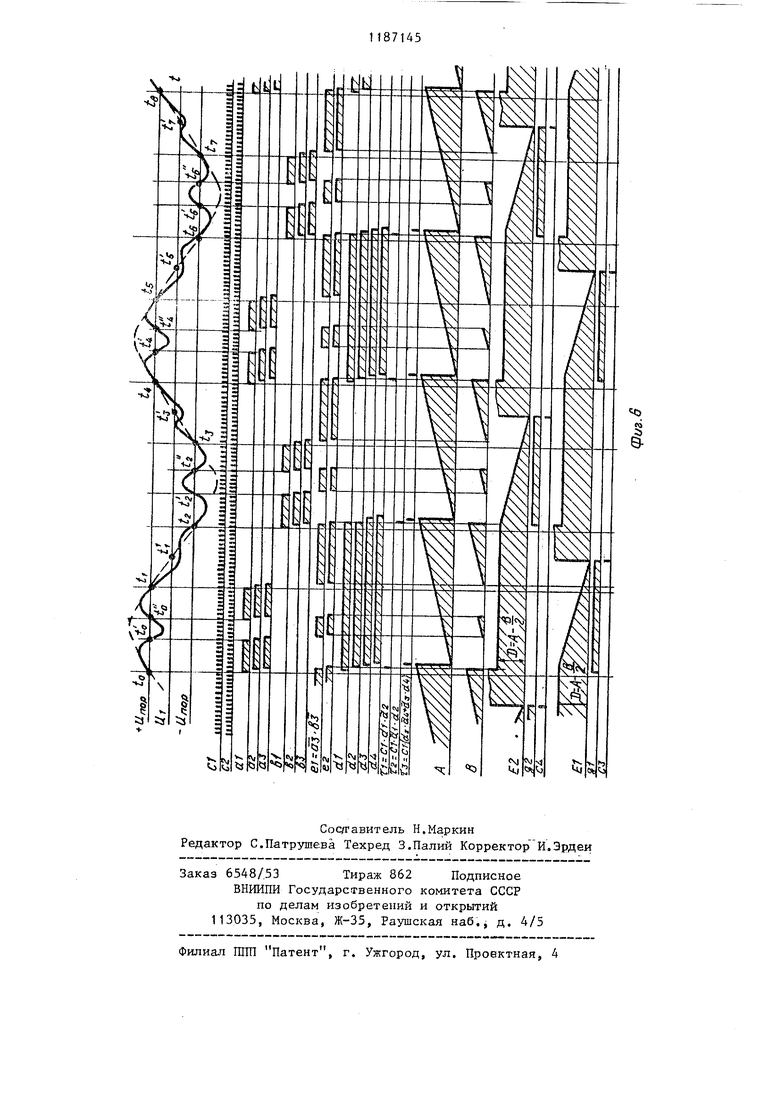

рых совпадает с фронтом С2. Сигнал d1 равен логической 1 в течение интервалов tp- t , tg и т.д. и логического О в течение интервалов t , tg (с точностью до сдвига). Далее на регистре сдвига на D-триггерах 23-25 сигнал d1 три раза сдвигается для получения сигналов d2, d3, d4,, с помощью которых формируются импульсы записи кода с выхода комбинационного сумматора 8 в преобразователи 9 и 10 кодвременной интервал и импульс установки в ноль счетчика 6. Первый сдвиг на D-триггаре 23 осуществляется по срезу С1, второй - на D-триггере 24 по фронту С2, а третий - на Dтриггере 25 также по срезу С1. На элементе ЗИ 26 формируются импульсысЛ, совпадающие с ClC d1 d2) и появляющиеся в моменты t, Ц, t с задержкой на сдвиги. Аналогично на элементе ЗМ 27 i)2 C1-dld2 появляется с Задержкой на сдвиги в моменты tj, tg и т.д.

На элементе 2-ЗИ-1ИЛИ 28 формируется импульс СЗ, совпадающий с импульсом С1 и задержанный относительно t 1 .и t 2 на один период С1. В качестве счетных импульсов для счетчиков 6 и 7 используются тактовые импульсы С2 (фиг.1,10). Разность между содержимым счетчика 6 и половиной содержимого счетчика 7 получается на комбинадионном сумматоре 8, работающем в режиме вычитания. Деление содержимого счетчика 7 на два осуществляется путем постоянного (монтажным способом) сдвига содержимого счетчика на один разряд вправо (в сторону ладших). При этом младший разряд счетчика 7 не используется, а на старший вычитающий вход сумматора 8 подается логический О. Выход суммы комбинадионного сумматоря 8 соединен с информадионными входами преобразователей 9 и 10 кодвременной интервал, следовательно, информадионными входами предварительной записи вычитающего счетчика 31, навход записи которого поступают импульсы записи о 1 2) . Каждый преобразователь кодременной интервал, кроме вычитащего счетчика 31, содержит деифратор 32 нулевого состояния

счетчика, D-триггер 29 с установками и элемент И 30. В настоящее время вместо отдельных вычитающего 5 счетчика и дешифратора нулевого состояния счетчика может быть применен реверсивный счетчик с встроенными дешифраторами нулевого и единичного состояний счетчика, имеющийся как в микросхемах серий

ТТЛ (К155ИЕ7. 133ИЕ7), так и К-МОП (К561ИЕ11, 564ИЕ11).

Дешифратор 32 нулевого состояния счетчика может быть реализован 5 при прямых выходах счетчика на логическом элементе ИЛИ-НЕ с инверс-« ным входом для стробирования сЗ(с4) А1...Апн- ЛГ. ... Триггер 29 и элементИ 30 образуют клапан для пропускания тактовых импульсов С2 на счетный вход вычитающего счетчика 31. Выходйые импульсы снимаются с выхода дешифратора 32.

5 Рассмотрим работу устрой:;тва во времени.

Пусть в момент tg (фиг.6) входное напряжение превьшгает положительный порог, в результате чего на

0 выходе компаратора 14 появляется уровень логической 1 (), который сдвигается на D-триггер 16 по фронту С1 (), а на D-триггере 18 - по фронту С2 (). В момент t входное напряжение становится меньше положительного-Порога, на выходе компаратора 14 снова появляется уровень логического О .(), который также сдвигается по С1

0 () и С2 (). Аналогично

происходит в моменты времени t,, t, t, t, t, tj, tg. Когда отрицательная полуволна входного сигнала превышает отрицательный порог, уровень

5 логической 1 появляется на выходе второго компаратора 15 (в 1 1), что происходит в моменты времени t, t, tg, tg. Когда отрицательная полуволна становится меньше отрицательного

0 порога, уровень логической 1 на

выходе компаратора 15 сменяется уровч нем логического О ( , моменты t, t, t, ty). Аналогично сдвигу a1 на D-триггерах 17 и 19 происходит

5 сдвиг сипнала в1 ( ).

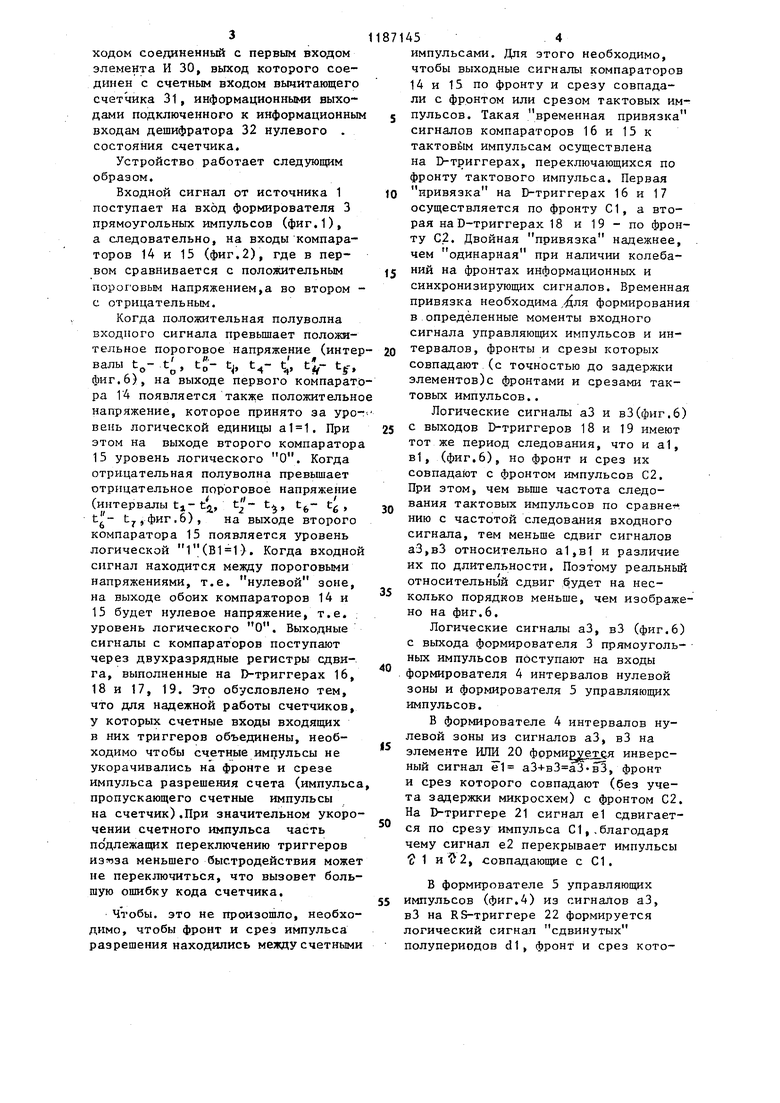

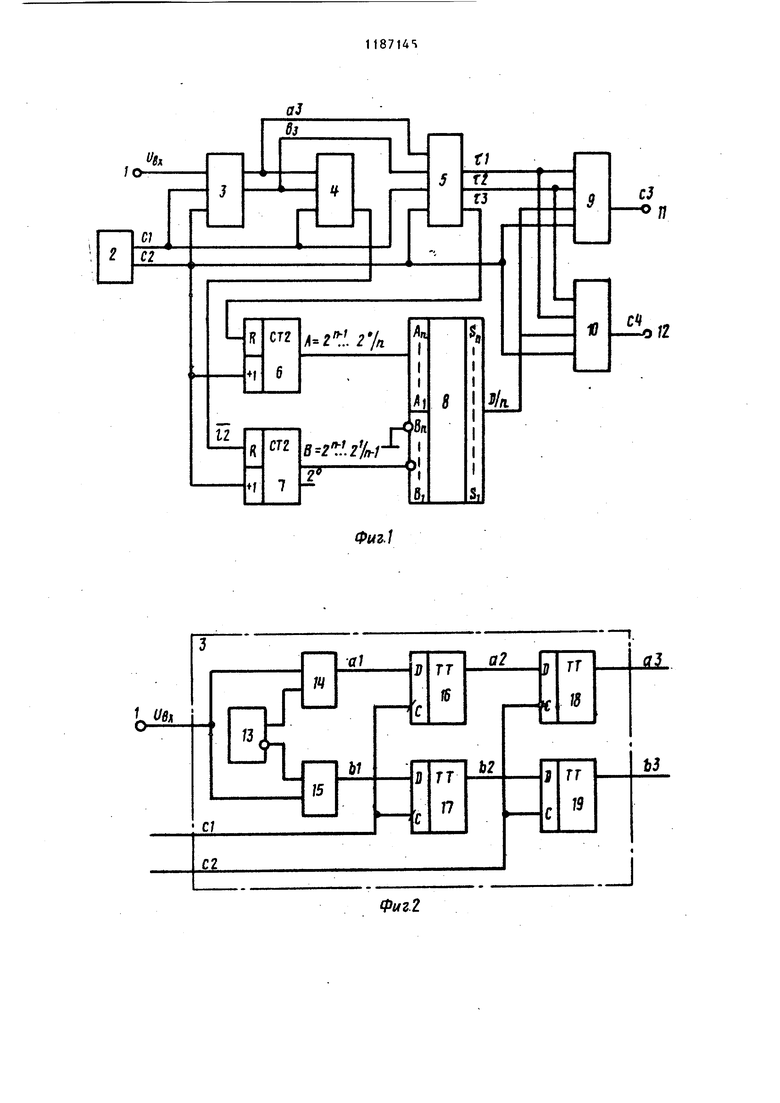

Когда значение входного напряжения находится между пороговыми уровнями | на выходах обоих компараторов 14 и 15 логический О, По положительному перепаду аЗ в момент t (с точностью до сдвига) RS-триггер 22 (фиг.8) переключается в состояние логической i, а в момент t .(с точностью до сдвига) по вЗ в состояние логического О. Аналогично в моменты t, tjH т.д. Таким образом формируется сигнал d1, который равен логической 1 в течение положительньпс сдвинутых полупериодов ( t tg и Т.Д.) логическому О в течени отрицательных сдвинутых полупериодо (tj - t, tg - tg и т.д.). В момент t импульс записи.С1 переписывает код D В вычитающий счетчик 31 преобразователя 10 код-временной интервал. При этом А-код, пропорцио нальный предьщущему сдвинутому отри цательному полупериоду; В-код, пропорциональный интервалу мезеду момен тами пересечения пороговьпс уровней входным сигналом. Одновременно импульс 1 в том ж преобразователе устанавливает ГЬтри гер 29 по входу R в состояние логического О если он по какой-либо причине находился в состоянии логической 1,например,при начальном включении. Тем самым предотвращаетс немедленное считывание записанного .кода. По срезу импульса 1 счетчик 7 (фиг.5) сигналом е2 сбрасывается в нуль по входу R и удерживаетс в нуле до тех пор, пока е2 1() Затем импульсом S 3 счетчик 6 сбрасывается в состояние нуль и со следующего импульса С2 начинает снова считать, преобразуя -положительный сдвинутый полупериод в код. Одновременно импульсом 1 момент tg D-триггер 29 в преобразователе 9 по входу S устанавливается в сос тояние логической 1 (), благодаря чему разрешается прохождение импульсов с2 через злемент ,И 30 на счетный вход вычитающего счетчика 31. Таким образом, код записанный в счетчик 31 преобразователя в предыдущий сдвинутый положительный полупериод (в момент аналогичный моменту t)начинает преобразовываться в интервал. После прохождед В импульсов С2 счетм А --j чик 31 првобра:эователя 9 установится в состояние О (), следующий (Б+1)-й импульс С2 пройдет через дешифратор 32 на выходную шину 11, а через элемент ЗИ 27 - на счетчный вход счетчика 31. По срезу (D +1 )-го умпульса 32,счетчик 31 из состояния О переключается в состояние 1, дешифратор 32 закрывается, прекращая прохождение импульса С2 на выходную шину 11. Одновременно по срезу (D+1)-ro импульса С2, прошедшего через дешифратор D-триггер 29 устанавливается в состояние О, запирая тем самым элемент И 30 и прекращая доступ импульсов С2 на счетный вход счетчика 31. Таким образом, в момент t на выходной шине 11 появится импульс СЗ, соответствующий переходу входного сигнала от положительного значенияк отрицательному. В течение интервала t - t , когда преобразователь 9 преобразует код в интервал, преобраэова: тель 10 находится в режиме хранения, а счетчики 6 и 7 заняты преобразот Ц - t, ванием интервалов соответственно в код. При этом интервал to - tg счетчиком. 7 не учитывается, так как после выхода входного сигнала из нулевой (межпороговый) зоны в момент t счетчик сбрасывается по входу R сигналом ЧН.) е2 (фиг.6). Начиная с момента t преобразователь 10 преобразует код, записанный в момент tg в интервал и выдает на выходную шину 12 импульс с4 в момент t . В это время преобразователь 9 находится в режиме хранения кода, записанного импульсом €2 с выхода комбинационного сумматора 8 в момент t. Далее процесс повторяется. 1 Изобретение относится к импульсн технике и может быть использовано для построения устройств. для измер ния частоты и фазы в устройствах уп равления тиристорными преобразовате . лями, работающих от питающей сети, форма напряжения которой сильно искажена. Цель изобретения - повышение то ности фиксации моментов переходов через нуль периодического сигнала, в том числе и искаженного. На фиг.1 изображена структурная схема устройства фиксации переходо через нуль периодического сигнала: на фиг.2 - 5 структурные схемы выполнения формирователя прямоугольных импульсов,формирователя интерв лов нулевой зоны, формирователя управляющих импульсов и преобразоват-ля код-временной интервал; на фиг. 6 - временные диаграммы,поясняющие работу устройства. Устройство фиксации переходов через нуль периодического сигнала содержит источник 1 входного сигнал генератор 2 тактовых импульсов, фо мирователь 3 прямоугольных импульсов, соединенньй первым входом с источником 1 входного сигнала, вторым и третьим входами соответствен с выходом и дополнительным выходом генератора 2 тактовь1х импульсов, формирователь 4 интервалов нулевой зоны, соединенный первым и вторым входами соответственно с первым и вторым выходами формирователя 3 прямоугольных импульсов, третьим входом - с выходом генератора 2 тактовых 1мпульсов, формирователь 5 управляющих импульсов, соединенный соответственно первым и вторым входами с вторыми выходами формирователя 3 прямоугольных импульсов и дополнительным выходом генератор 2 тактовых импульсов, первый счетчик 6, соединенный входом установки R с первым выходом формировател 5 управляющих импульсов, счетным входом - с дополнительным выходом генератора 2 тактовых импульсов, второй счетчик 7, соединенный входом установки R с выходом формирователя 4 интервалов нулевой зоны, счетным входом - с дополнительным выходом генератора 2 тактовых импульсов, комбинационный сумматор 8, соединенный прямыми информацион52ными входами с информационными выходами первого счетчика 6 и инверсными, кроме старшего, с информационными выходами второго счетчика 7 со сдвигом на один разряд в сторону старших, первый 9 и второй 10 преобразователи код-временной интервал. Соединенные первыми входами с дополнительным выходом генератора 2 тактовых импульсов, при зтом вторые и третьи входы преобразователей код-временной интервал подключены соответственно с вторыми и третьими выходами формирователя 5 управляющих импульсов, а выходы преобразователей 9 и 10 код-временной интервал подключены соответственно к первой 11 и второй 12 выходным шинам, причем формирователь 3 прямоугольных импульсов содержит источник 13 опорного напряжения и два компаратора 14 и 15, первые входы которых подключены к первому входу формирователя 2 прямоугольных импульсов, вторые входы - соответственно к прямому и инверсному выходам источника 13 опорного напряжения, а выходы - к информационньй входам первого и второго D -триггера 16 и 17, прямые выходы которых соединены -с информационными входами третьего и четвертогоО-триггера 18 и 19. Формирователь 4 интервалов нулевой зоны содержит элемент ИЛИ 20, выходом подключенный к информационному входу D -триггера 21, формирователь 5 управляюпщх импульсов содержит RS-триггер 22, прямой выход которого подключен к информационному входу первого D - триггера 23, прямым выходом соединенного с информационным входом-второго Dтриггера 24, прямой выход которого соединен с информационным входом четвертого D-триггера 25, при зтом гфямой выход К&-триггера 22 и инверсньш выход первого D -триггера 23 подключены к первому и второму входу первого элемента 3 И 26,9нверсный выход RS -триггера 22 и прямой выход первого D -триггера 23 подключены к первому и второму входу второго элемента ЗИ 27, прямой выход второго D - триггера 24 подключен к первому входу элемента ЗИ элемента ЗИ-ИЛИ 28, преобразователь код-временной интервал содержит D-триггер 29, вы3ходом соединенный с первым входом элe feнтa И 30, выход которого соединен с счетным входом вычитающего счетчика 31, информационными выходами подключенного к информационны входам дешифратора 32 нулевого . состояния счетчика. Устройство работает следующим образом. Входной сигнал от источника 1 поступает на вход формирователя 3 прямоугольных импульсов (фиг.1), а следовательно, на входы компараторов 14 и 15 (фиг.2), где в первом сравнивается с положительным пороговым напряжением,а во втором с отрицательным. Когда положительная полуволна входного сигнала превышает положительное пороговое напряжение (инте валы t,, t, t|, ttf t,., фиг.6), на выходе первого компарат ра 14 появляется также положительн напряжение, которое принято за уро веиь логической единицы . При этом на выходе второго компаратор 15 уровень логического О. Когда отрицательная полуволна превышает отрицательное пороговое напряжение (интервалы tj- t,j, t - t, t , t- tJ.,фиг,6), на выходе второго компаратора 15 появляется уровень логической Г (. Когда входно сигнал находится между пороговыми напряжениями, т.е. нулевой зоне, на выходе обоих компараторов 14 и 15 будет нулевое напряжение, т.е. уровень логического О. Выходные сигналы с компараторов поступают через двухразрядные регистры сдвига, выполненные на D-триггерах 16, 18 и 17, 19. Это обусловлено тем, что для надежной работы счетчиков у которых счетные входы входящих в них триггеров объединены, необходимо чтобы счетные имцульсы не укорачивались на фронте и срезе импульса разрешения счета (импульс пропускающего счетные импульсы на счетчик).При значительном укор чении счетного импульса часть подлежащих переключению триггеров изя5за меньшего быстродействия може не переключиться, что вызовет боль шую ошибку кода счетчика. Чтобы, это не произошло, необхо димо, чтобы фронт и срез импульса разрешения находились между счетным 54 импульсами. Для этого необходимо, чтобы выходные сигналы компараторов 14 и 15 по фронту и срезу совпадали с фронтом или срезом тактовых импульсов. Такая временная привязка сигналов компараторов 16 и 15 к тактовб1м импульсам осуществлена на 1 -т1 иггерах, переключающихся по фронту тактового импульса. Первая привязка на D-триггерах 16 и 17 осуществляется по фронту С1, а вторая на D-триггерах 18 и 19 - по фронту С2. Двойная привязка надежнее, чем одинарная при наличии колебаНИИ на фронтах информационных и синхронизирующих сигналов. Временная привязка необходима , формирования в определенные моменты входного сигнала управляющих импульсов и интервалов, фронты и срезы которых совпадают (с точностью до задержки элементов)с фронтами и срезами тактовых импульсов.. Логические сигналы аЗ и вЗ(фиг.б) с выходов D-триггеров 18 и 19 имеют тот же период следования, что и a1, в1, (фиг.6), но фронт и срез их совпадают с фронтом импульсов С2. При этом, чем Bbmie частота следования тактовых импульсов по сравне- нию с частотой следования входного сигнала, тем меньше сдвиг сигналов аЗ,вЗ относительно а1,в1 и различие их по длительности. Поэтому реальный относительный сдвиг будет на несколько порядков меньше, чем изображено на фиг.6. Логические сигналы аЗ, вЗ (фиг.6) с выхода формирователя 3 прямоугольных импульсов поступают на входы формирователя 4 интервалов нулевой зоны и формирователя 5 управляющих импульсов. В формирователе 4 интервалов нулевой зоны из сигналов аЗ, вЗ на элементе ИЛИ 20 фррми дет ея инверсный сигнал 1 аЗ+БЗ аЗв1, фронт и срез которого совпадают (без учета задержки микросхем) с фронтом С2. На Б-триггере 21 сигнал el сдвигается по срезу импульса С1,.благодаря чему сигнал е2 перекрывает импульсы 1 , совпадающие с С1 . В формирователе 5 управляющих импульсов (фиг.4) из сигналов аЗ, вЗ на RS-триггере 22 формируется логический сигнал сдвинутых полупериодов d1, фронт и срез котоc

12

Фиг.З

Фиг.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2262191C1 |

| СПОСОБ ИЗМЕРЕНИЯ ПАРАМЕТРОВ СИНУСОИДАЛЬНОГО НАПРЯЖЕНИЯ И ИЗМЕРИТЕЛЬ ЕГО РЕАЛИЗУЮЩИЙ (ВАРИАНТЫ) | 2014 |

|

RU2577549C2 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ СИНУСОИДАЛЬНОГО НАПРЯЖЕНИЯ | 2015 |

|

RU2582880C2 |

| Цифровое фазосдвигающее устройство | 1983 |

|

SU1185533A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1522408A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2002 |

|

RU2249911C2 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

1. УСТРОЙСТВО ДЛЯ ФИКСАЦИИ ПЕРЕХОДОВ ЧЕРЕЗ НУЛЬ.;. ПЕРИОДИЧЕСКОГО СИГНАЛА, содержащее выходные шины, источник входного сигнала, формирователь прямоугольных импульсов, подсоединенный первым входом к источнику входного сигнала, формирователь интервалов нулевой зоны, подсоединена, ный первым и вторым входами соответственно к первому и второму выходам формирователя прямоугольных импульсов, формирователь управляющих импульсов, подсоединенный первым входом к второму выходу формирователя прямоугольных импульсов, первый счетчик, подсоединенный входом установки к первому выходу формирователя управляющих импульсов, генератор тактовых импульсов, подсоединенный выходом к третьему входу формирователя интервалов нулевой зоны,и второй счетчик, отличающееся тем, что, с целью повьщ1ения точности фиксации моментов переходов через нуль искаженного периодического сигнала, в него введены два преобразователя код-временной интервал и комбинационный сумматор, подсоединенный прямыми информационными входами к информационным выходам первого счетчика, и инверсными, кроме старшего, соединенного с щиной нулевого потендиала к информационным выходам второго счетчика со сдвигом на один разряд в сторону старших, вход установки которого соединен с выходом формирователя интервалов нулевой зоны, при этом счетные входы обоих счетчиков соединены с дополнительным выходом генератора тактовых импульсов, с третьим входом формирователя прямоугольных- импульсов, с третьим вхос 59 дом формирователя управляющих импульсов и с первьши входами первого (Л .и второго преобразователя код- врес: менной интервал, соединенных вторыми и третьими входами соответственно- с вторыми и третьми выходами формирователя управляюпщх импульсов, четвертый вход которого подключен 00 к первому выходу формирователя прямоугольных импульсовi а четвертые входы преобразователей код- времен1 С ной интервал подключены к выходу суммы комбинационного сумматора, причем второй вход формирователя управляющих импульсов соединен с выходом генератора тактовых импульсов, выходы преобразователей кодвременной интервал соединены соответственно с первой и второй выходными шинами,а выход генератора тактовых импульсов соединен с вторым входом формирователя прямоугольных импульсов. 2. Устройство по П.1, отличающееся тем,что формирователь прямоугольных импульсов

| Детектор перехода через ноль | 1978 |

|

SU738130A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-10-23—Публикация

1984-01-05—Подача