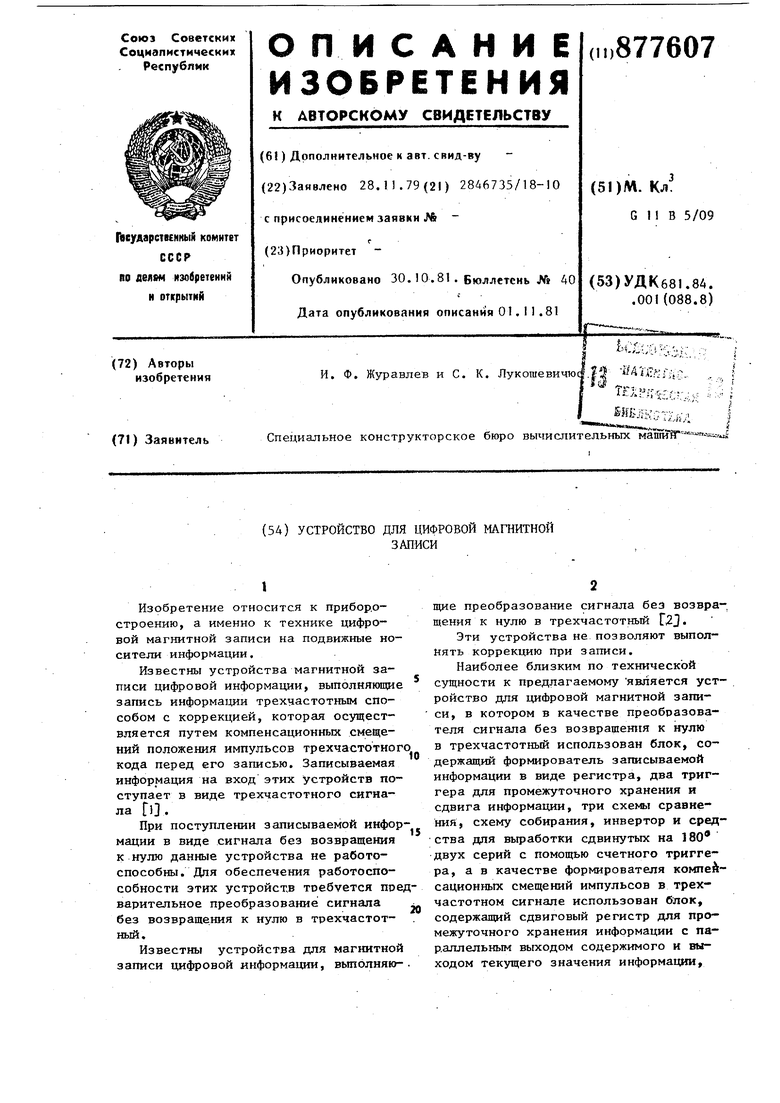

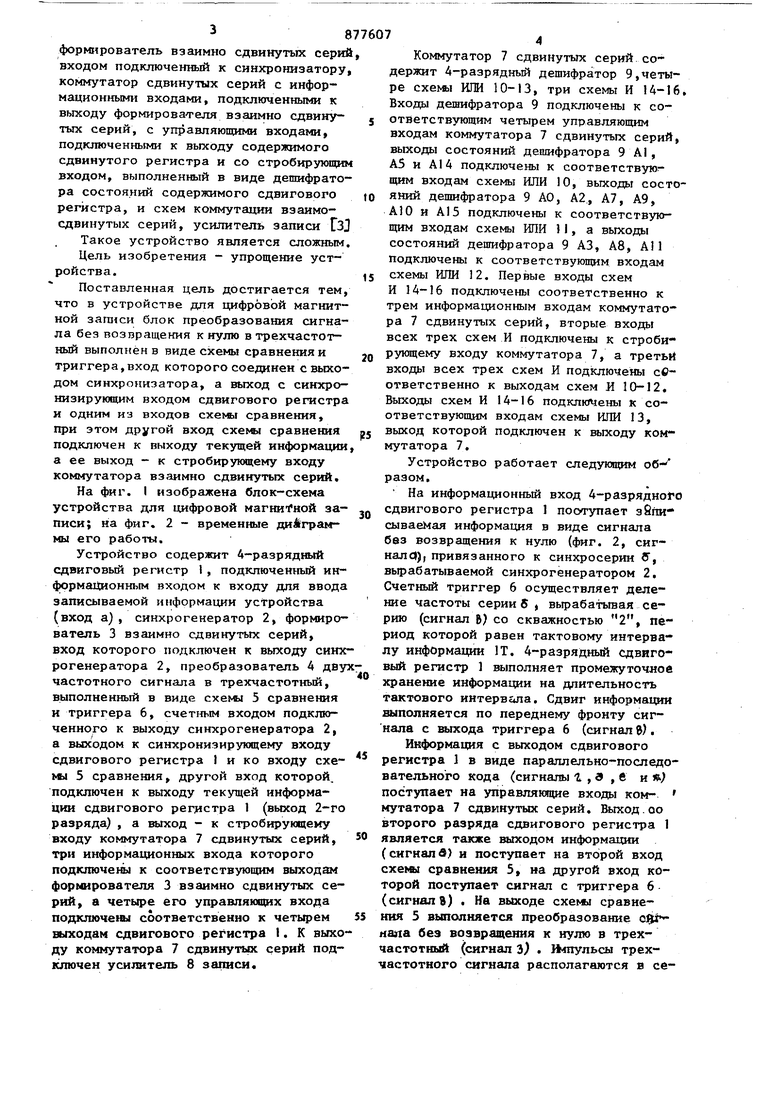

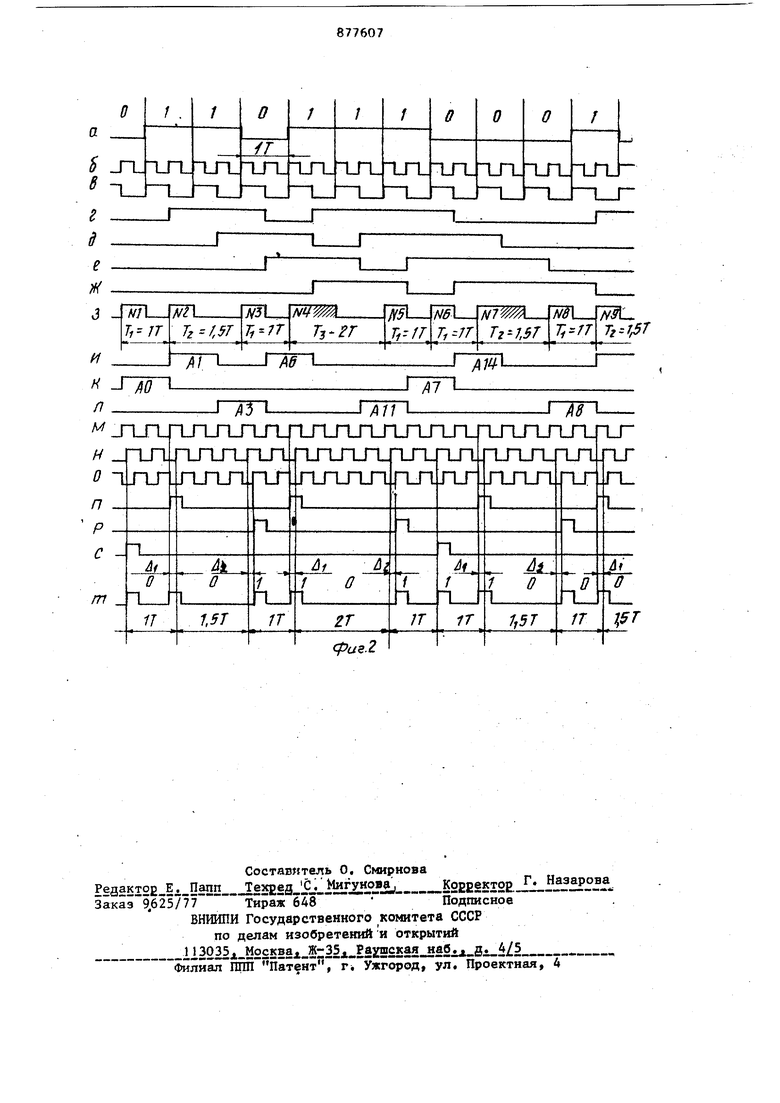

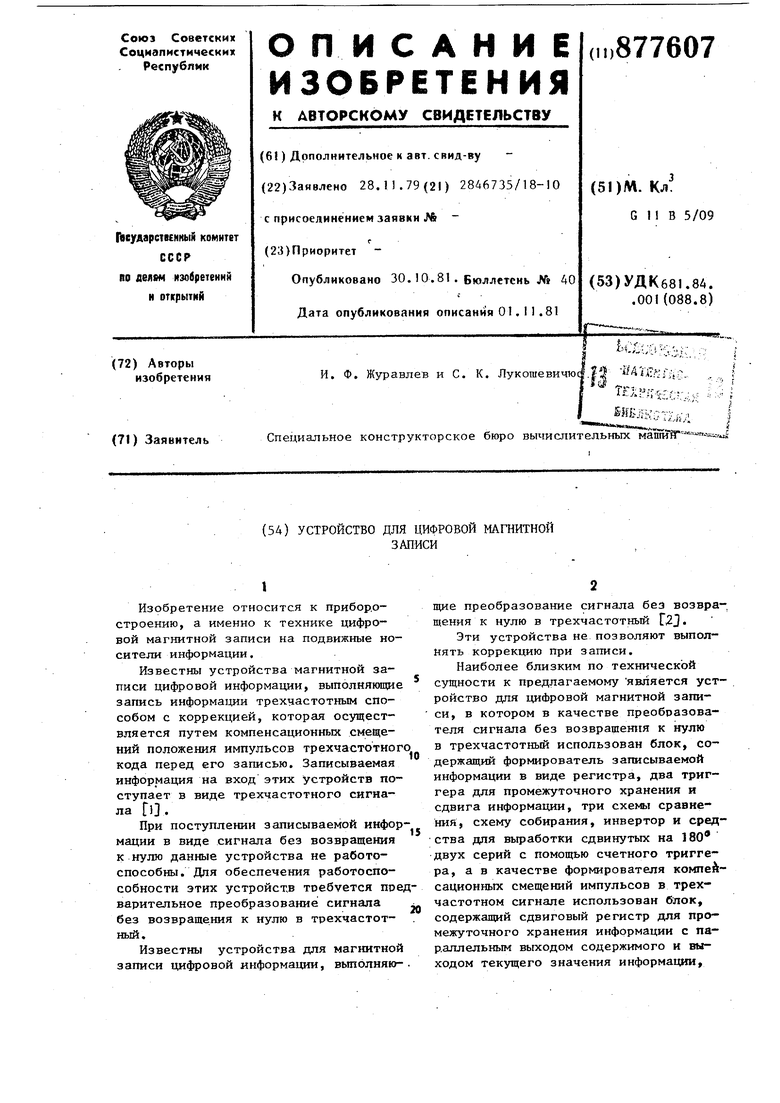

(54) УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ Изобретение относится к прибор.остроению, а именно к технике цифровой магнитной записи на подвижные носители информации. Известны устройства магнитной записи цифровой информации, выполняющие запись информа1дии трехчастотным способом с коррекцией, которая осуществляется путем компенсационных смещений положения импульсов трехчастотног кода перед его записью. Записываемая информация на вход этих устройств поступает в виде трехчастотного сигнала }. При поступлении записываемой инфор мации в виде сигнала без возвращения к нулю данные устройства не работоспособны. Для обеспечения работоспособности этих устройств тоебуется пре варительное преобразование сигнала без возвраще;ния к нулю в трехчастотный. Известны устройства для магнитной записи цифровой информации, выполняюЗАПИСИщие преобразование сигнала без возвра- щения к нулю в трехчастотный Г23. Эти устройства не позволяют выполнять коррекцию при записи. Наиболее близким по технической сущности к предлагаемому является устройство для цифровой магнитной затти- си, в котором в качестве преобразователя сигнала без возвращения к нулю в трехчастотный использован блок, содержащий формирователь заттисываемой информации в виде регистра, два триггера для промежуточного хранения и сдвига информации, три схемы сравнения, схему собирания, инвертор и средства для вьфаботки сдвинутых на 180 двух серий с помощью счетного триггера, а в качестве формирователя компейсационных смещений импульсов в трехчастотном сигнале использован блок, содержащий сдвиговый регистр для промежуточного хранения информации с параллельным выходом содержимого и выходом текущего значения информации. 38 формирователь взаимно сдвинутых серий входом подключенный к синхронизатору, коммутатор сдвинутых серий с информационными входами, подключенными к выходу формирователя взаимно сдвину тых серий, с управляющими входами, подключеннь1ми к выходу содержимого сдвинутого регистра и со стробирующим входом, выполненный в виде дешифратора состояний содержимого сдвигового регистра, и схем коммутации взаимосдвинутых серий, усилитель записи ГзЗ Такое устройство является сложным. Цель изобретения - упрощение устройства, Поставленная цель достигается тем, что в устройстве для цифровой магнитной записи блок преобразования сигнала без возвращения к кулю втрехчастотный выполнен в виде схемы сравнения и триггера,вход которого соединен с выходом синхронизатора, а выход с сиюфо- низирующим входом сдвигового регистра и одним из входов схемы сравнения, при этом другой вход схеьвл сравнения подключен к выходу текущей информации а ее выход - к стробирующему входу коммутатора взаимно сдвинутых серий. На фиг. I изображена блок-схема устройства для цифровой магнитной записи; на фиг. 2 - временные диАграммы его работы. Устройство содержит 4-разрядный сдвиговый регистр 1, подключенный информагШонным входом к входу для ввода записываемой информации устройства (вход а) , синхрогенератор 2, формирователь 3 взаимно сдвинутых серий, вход которого подключен к выходу синх рогенератора 2, преобразователь 4 дву частотного сигнала в трехчастотный, выполненный в виде схекеа 5 сравнения и триггера 6, счетным входом подключенного к выходу синхрогенератора 2, а выходом к синхронизирующему входу сдвигового регистра 1 и ко входу схема 5 сравнения, другой вход которой, подключен к выходу текущей информации сдвигового регистра 1 (выход 2-го разряда) , а выход - к стробирующеиу входу коммутатора 7 сдвинутых серий, три информационных входа которого подкточеш к соответствующим выходам форь ирователя 3 взаимно сдвинутых серий, а четыре его управлякщих входа подключены соответственно к четырем выходам сдвигового регистра I. К выхо ду коммутатора 7 сдвинутьрс серий подключен усилитель 8 записи. Коммутатор 7 сдвинутых серий содержит 4-разрядный дещифратор 9,четыре ИЛИ 10-13, три схемы И 14-16, Входы дешифратора 9 подключены к соответствующим четырем управляющим входам коммутатора 7 сдвинутых серий, выходы состояний дешифратора 9 А1, А5 и AI4 подключены к соответствую щим входам схемы ИЛИ 10, выходы состояний дещифратора 9 АО, А2, А7, А9, AID и А15 подключены к соответствующим входам схемы ИЛИ II, а выходы состояний дешифратора 9 A3, А8, АП Подключены к соответствующим входам схемы ИЛИ 12. Первые входы схем И 14-16 подключены соответственно к трем информационным входам коммутатора 7 сдвинутых серий, вторые входы всех трех схем И подключены к строби рующему входу коммутатора 7, а третьи входы всех трех схем И подключены соответственно к выходам схем И 10-12. Выходы схем И 14-16 подклкМены к соответствующим входам схемы ИЛИ 13, выход которой подключен к выходу коммутатора 7. Устройство работает следующим об-- разом. На информационный вход 4-разрядноГО сдвигового регистра 1 поотупает зЙпи сываеМая информация в виде сигнала без возвращения к нулю (фиг. 2, сигнал0), привязанного к синхросерии б, вырабатываемой синхрогенератором 2. Счетный триггер 6 осуществляет деление частоты серии S вырабатьгаая серию (сигнал 6) со скважностью 2, период которой равен тактовому интервалу информации IT. 4-разрядный сдвиговый регистр 1 выполняет промежуточное хранение информации на длительность тактового интерв&ла. Сдвиг информации выполняется по переднему фронту сигнала с ш 1хода триггера 6 (сигнал и). Информация с выходом сдвигового регистра 1 в виде параллельно-последовательного кода (сигналы 1 , Э , б и л поступает на управляющие входы коммутатора 7 сдвинутых серий. Выход.оо второго разряда сдвигового регистра 1 является также выходом информации (сигнал в) и поступает на второй вход схеквл сравнения 5, на другой вход которой поступает сигнал с триггера 6 (сигнале) . На выходе схемы сравнения 5 выполняется преобразование cfU нала без возвращения к нулю в трехчастотный (сигнал Ъ) 1 «гульсы трехчастотного сигнала располагаются в середине тактового интервала (импульсы N, N,, Ng, Ng), если текущая информ ция равна О (низкий уровень сигнала Э , и в начале тактового интервала (импульсы Ng, N, Njj-, Ny) j если текущая информация равна (высокий уровень сигнала 3) . Таким образом, преобразователь 4 выполняет пре образование сигнала без возвращения к нулю в трехчастотный (интервалы Т « JT, l в 1,5Т и Тз 2т), Информация с выходов сдвигового регистра J через зшравлякяцие входы .коммутатора 7 сдвинутых серий поступает а входы четырехразрядного дешифратора 9, который дешифрирует состояния информации сдвигового регистра 1 от О (выходы АОА15, фиг. ). При информации 0000 сдвигового регистра (сигналы ,, е«0 0) возбуждается выход АО, а лри . информации 0001 сдвигового регистра 1 (сигналы 1 1, , , Ж « о) возбуждается выход А1 и т.д. Схема ИЛИ 10, объединяющая вхйды А1, А6 и А14 дешифратора 9, возбужда ется при1 .информации 0001,0110 и 1110 сдвигового регистра 1 (сигнал . При рассмотрении сигналов И и 3 видно, что в момент действия пол жительного импульса сигнала и импуль сигнала 5 находится на границе двух интервалов IT и 1,5Т (импульс N N или IT и 2Т (импульс ), При воспро изведении записанных с высокой плотностью этих интервалов импульс, нахо дящийся на стыке этих двух интервалов, смещается в сторону более длинн го интервала, тем самым происходит фазовое искажение сигнала. Для их ко пенсации импульс перед записью смеща ют в сторону более короткого интервала. Эта задача решается с помощью се рии м, и и о , причем серия м опере:жает серию н на величину Д , а серия О запаздывает относительно оерии н на величину Дг. Схема И 1А в р зультате взаимодействия сигналов И Ъ им вырабатывает сигнал п , соответствующий смещению импульсов трехчастотного сигнала. Аналогичным образом схема И 16 « в результате взаимодействия сигналов Л , J и о вырабатывает сигнал р , соответствуняций компенсационному смещению импульсов трехчастотного сигнала вправо на запаздывание. В осталйных случаях при информации 0000, 0010, 0111, 1001, 1010 и 11 сдвигового регистра I, о наличии которой свидетельствуют положительные импульсы сигнала к. (на фйГ|2 показаны импульсы только для информации 0000, 0111 , импульс сигнала 3 находится на стыке длинных интервалов ,5Т и 2Т или 2Т и 2Т, или на схеме коротких интервапой IT и IT. В этом случае компенсационные смещения в трехчастотный .сигнал не вводятся, так как фазовые искажения при этом незначительны. Поэтому схема И 15 вырабатывает сигнал с без компенсационного смещения импульсов трехчастотного сигнала в результате взаимодействия сигналов к ,3 и к, Состояния информации 0100, 0101, 1100 и 1101 (шлходы А4, Аз, А12 и А13) для коммутации взаимно сдвии тьк серий не используются, так как эти состояиия информации сдвигового регистра 1 соответствуют второй половине широких импульсов (импульсы N и N7) сигнала з (на фиг. 2 .эта часть импульса заштрихована). Это происходит тогда, когда текущая информация 0( Э Oj , а предыдущая информация была 1(б - О . Использование защтриховаиной части импульса сигнала 3 в формировании компенсационных смещений привело бы к введению лишиих импульсов в трехчастотиом коде, что недопустимо. С выхода схемы ИЛИ 13 (сигнал т) трехчастотный сигиал, содержащий компенсационные смещения, поступает в усилитель записи, который выполняет, запись информации на магнитный носитель . . . Упрощение предлагаемого устройства достигается за счет совмещения функций сдвигового регистра для блока преобразования двухчастотного сигнала без возвращения к нулю в трехчастотный и для блока формирования компенсаионных смещений импульсов в трехчастотиом сигнале за счет умеиьшения азрядности сдвигового регистра пу- тем промежуточного хранения информации , в нем на длительность одного такта место полтакта и за счет упрощения лока преобразования сигнала без возращения к нулю в трехчастотный блаодаря возможности в дальнейшем обрабатывать его выходной сигнал, содеращий импульсы с излишней птриной Формула изобретения Устройство для цифровой магнитной «записи, содержащее синхронизатор, соединенный с ним, формирователь взаимно сдвинутых серий, блок преобразования сигнала без возвращения к нулю в трехчастотный сдвиговый регистр, усилитель записи и коммутатор сдвинутых серий, информационные входы которого подключены к выходам формирователя взаимно сдвинутых серий, его управляющие входы к выходам, один из которых является выходом информации сдвигового регистра, а его выход подключен к входу усилителя записи, отличающееся тем, что, с целью упрощения устройства, блок преобразования сигнала без воз878 вращения к нулю в трехчастотный выполнен в виде схемы сравнения и триггера, выход которого соединен с выходом синхронизатора, а выход с синхронизирующим входом сдвигового регистра и одним из входов схемы сравнения, при этом другой вход схемы сравнения подключен к выходу текущей информации, а ее выход - к стробирующему входу коммутатора взаимно сдвинутых серий. Источники информации, принятые во внимание при.экспертизе . Патент США № 3697977 кл. 340-347, 1972. 2.Патент США № 3774178, кл. 340-174.1, 1973. 3.Патент США № 3879342, кл. 360-45, 1975 (прототип).

г

д е )i

A JnJтгLПJl JlЛJlJlJ J1-ЛJlJ

//

срие.2 .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи цифровой информации | 1983 |

|

SU1123051A1 |

| Устройство кодирования цифровой информации способом модифицированной частотной модуляции | 1980 |

|

SU866571A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Полевая телеметрическая сейсмическая станция | 1986 |

|

SU1368837A1 |

| Способ записи-воспроизведения сигналов синхронизации в цифровом канале магнитной записи | 1982 |

|

SU1053150A1 |

| Устройство записи-воспроизведения цифровой информации на магнитном носителе | 1981 |

|

SU980138A1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| Устройство модуляции для цифрового аппарата магнитной записи | 1977 |

|

SU660086A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Способ кодирования сигнала с частичным откликом для передачи цифровой информации | 1985 |

|

SU1297230A1 |

Авторы

Даты

1981-10-30—Публикация

1979-11-28—Подача