Изобретение относится к вычислительной технике и может использовать- с/1 в системах передачи цифровой информации по каналам с межсимвольной интерференцией,

Цель изобретения - повышение помехоустойчивости.

На фиг. 1 изображены-временные диаграммы для случая п fК, ш 5К+2, совпадающего со способом-прототипом; на фиг. 2 - то же, для случая , для на фиг. 3 и 4 - временные диаграммы возможных вариантов передачи последовательности единиц (а) или нулей (б); на фиг. 5 и 6 - блок-схемы соответственно кодирующего и декодирующего устройств, с помощью которых может быть реализован данный способ.

Принцип кодирования по данному способу заключается в разрушении в пере- даваемом сигнале длинных последовательностей единиц или нулей при сохранении основного свойства сигнала с частичным откликом (.или дуобинар- ного кода) - высокой удельной скороети передачи.

Кодирование осуществляется следующим образом.

Если во входном сигнале (фиг.) отсутствуют последовательности симво- лов О длиной К+3 и более тактовых интервалов и последовательности символов 1 длиной К+1 и более тактовых интервалов, то формирование передаваемого сигнала осуществляется по правилу формирования дуобинарного кода. При этом каждому символу О входного сигнала (фиг. IQ.) соответствует изменение уровня выходного сигнала, а при символах 1 изменение уровня выходного сигнала не произво- дится (фиг. lS). На выходе канала, имеющего полосу пропускания if й1/2Т (Т - длительность тактового интервала передаваемого сигнала) в этом слу- чае формируется сигнал, который показан на фиг. 1Ь. Промежуточный уро- :Вень этого сигнала соответствует символам О исходной информации, а граничные уровни (+1 или -1) - симво- лам 1.

Для последовательностей символов 1 с числом символов формирование выходного сигнала осуществляется по следующему правилу (фиг. За): сна- чала вся последовательность длиной п символов 1 разбивается на блоки по К тактовых интервалов в каждом блоке. Длина последнего блока зависит от

величины К и может изменяться от 1 до К. Затем во всех блоках, кроме последнего, изменяют К раз уровень сигнала, начиная с середины второго до середины последнего тактового интервала включительно, В последнем блоке при любых соотношениях п и К уровень сигнала не изменяется.

Правило формирования сигналя для последовательностей символов О с числом символов иллюстрирует фиг. 3S. Сначала вся последовательность символов О длиной m тактовых интервалов разбивается на блоки по К+2 символа О, Длина последнего блока зависит от соотношения величин m и К и может изменяться от 1 до тактовых интервалов. Затем во всех блоках, кроме последнего, изменяют К+2 раза уровень сигнала, начиная с середины первого до середины предпоследнего, (К+1)-го тактового интервала. В последнем блоке при любых соотношениях между величинами m и К+ изменение уровня сигнала осуществляю по правилу формирования дуобинарного кода.

На фиг. 2 изображен вариант кодирования по предлагаемому способу при , когда в исходной информации есть серия символов 1 с числом и серия символов О с числом .

Сигнал с описанньгми свойствами может быть получен по-разному. Например, в первом варианте (фиг.2 и 3 формирование сигнала осуществляется с частотой, кратной полутактовой частоте входного сигнала. Во втором варианте (фиг. 4) при изменение К и К+2 раза уровней сигнала осуществляется с частотой, не кратной полутактовой частоте входного сигнала. При оба варианта кодирования обеспечивают формирование сигналов, не отличающихся по форме.

Восстановление исходной двоичной информации на приеме может осуществляться по следующему правилу:

участок сигнала с промежуточным уровнем между импульсами с разными граничными уровнями, имеющий длину, равную (К-1)-му тактовому интервалу, соответствует символам 1 исходной цифровой информации; другие участки сигнала с промежуточным уровнем соответствуют символам

импульсу сигнала с одним из граничных уровней соответствует символ О исходной цифровой последовательности, если уровень этого импульса противоположен уровню предшествующего импульса и импульсы разделены (К+1)-ым тактовым интервалом; все другие импульсы соответствуют симво- с лам 1.

Параметр К выбирается исходя из ряда противоречивых требований к сигналу и определяется характеристиками конкретного канала передачи. Ь мень- Ш шеиие величины К ведет к увеличению числа изменений уровня в принимаемом сигнале. Это повышает стабильность работы системы выделения синхронизации при приеме и уменьшает искажения 15 сигнала из-за низкочастотной межсимвольной интерференции. Минимизация величины К желательна также для уменьшения коэффициента размножения ошибок при декодировании сигнала. 20

Однако при малых значениях К наблюдается относительно большое изменение частоты следования импульсов передаваемого сигнала для последовательностей символов 1 и О, что 25 приводит к искажению длительности и амплитуды импульсов принимаемого сигнала. В худшем случае (при ) на приеме наблюдается 16%-ное уменьшение раскрыва глаз-диаграммы, которое 30 уменьшается при увеличении значения К.

Сущность изобретения составляет предлагаемая последовательность опе- ,раций над входным цифровым сигналом, при которой в принимаемом сигнале 35 для последовательностей символов 1 исключается появление однополярных последовательностей с одним из граничных уровней и ограничивается число тактовых интервалов без изменения 40 уровня принимаемого сигнала как для последовательностей символов 1. так и последовательностей символов О. Таким образом, в сигнале уменьшаются низкочастотные компоненты и 45 обеспечивается работа системы приема сигнала в режим самосинхронизации.

Указанный положительный эффект

одним из граничных уровнен, соответ ствующие только тем участкам в пере даваемом сигнале, в пределах которы изменение уровня сигнала происходит реже, чем через один тактовый интер вал входной цифровой последовательности (фиг. 1 и 2). При использовании предлагаемого способа кодирования длина участков передаваемого си нала без изменения уровня сигнала н может превышать К тактовых интервал при передаче 1 и К+2 тактовых интервалов при передаче символов О (фиг. 2, 3 и 4). Поэтому уровень ни кочастотных компонент в спектре: сигнала меньше, чем при использовании дуобинарного способа кодировани для которого длина участков принима мого сигнала с одним из граничных уровней может неограниченно возрастать.

Режим самосинхронизации при прие ме сигнала обеспечивается путем ста бильной подстройки системы синхрони зации, поскольку ограничение длины участков без изменения уровня при передаче сигнала, соответствующего последовательностям символов 1 входного цифрового сигнала, гарантирует на приеме получение импульсов следующих не реже чем через К-1, а при передаче последовательностей сим волов О - не реже,чем через К+1 тактовый интервал;

На практике разбиение последовательности одинаковых символов на бло ки производится последовательно.

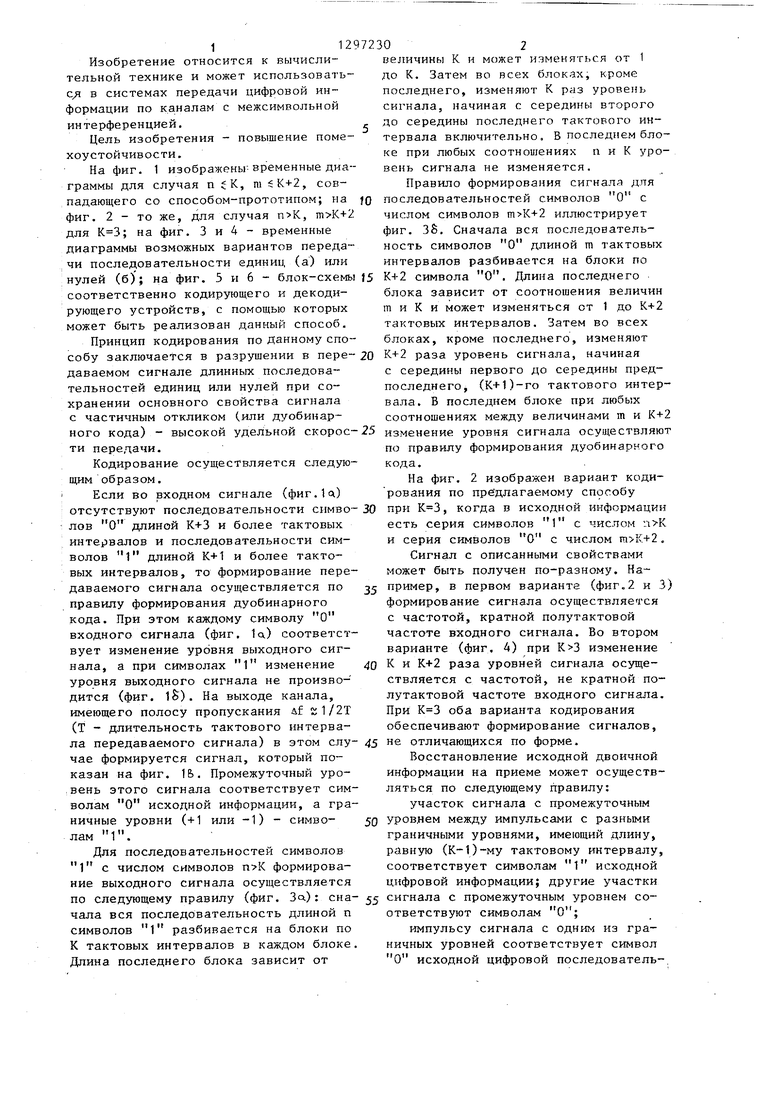

Устройство кодирования для реализации данного способа формирования сигнала с частотой, не 1фатной полутактовой частоте входного сигнала, включает в себя (фиг. 5) элементы 1 2 задержки на один тактовый интервал первый и второй дешифраторы 3, 4, элемент 5 задержки на К+2 тактовых интервалов, элементы И 6, 7, элементы НЕ 8, 9, первый, второй и третий, формирователи 10, 11, 12 импульсов.

элемент 13 задержки на 2 тактовых достигается путем формирования сигна- д интервала, RS-триггеры 14, 15, элела по описанному правилу и основан на особенностях передачи сигналов с частичным откликом, когда принимаемая последовательность импульсов представляет собой суперпозиц 1ю откликов тракта передачи на передаваемый сигнал в соседних тактовых интервалах. При этом в сигнале с частичным откликом форйируются импул1,сы с

мент ИЛИ 16, логический коь мутатор 17 счетный триггер 18,

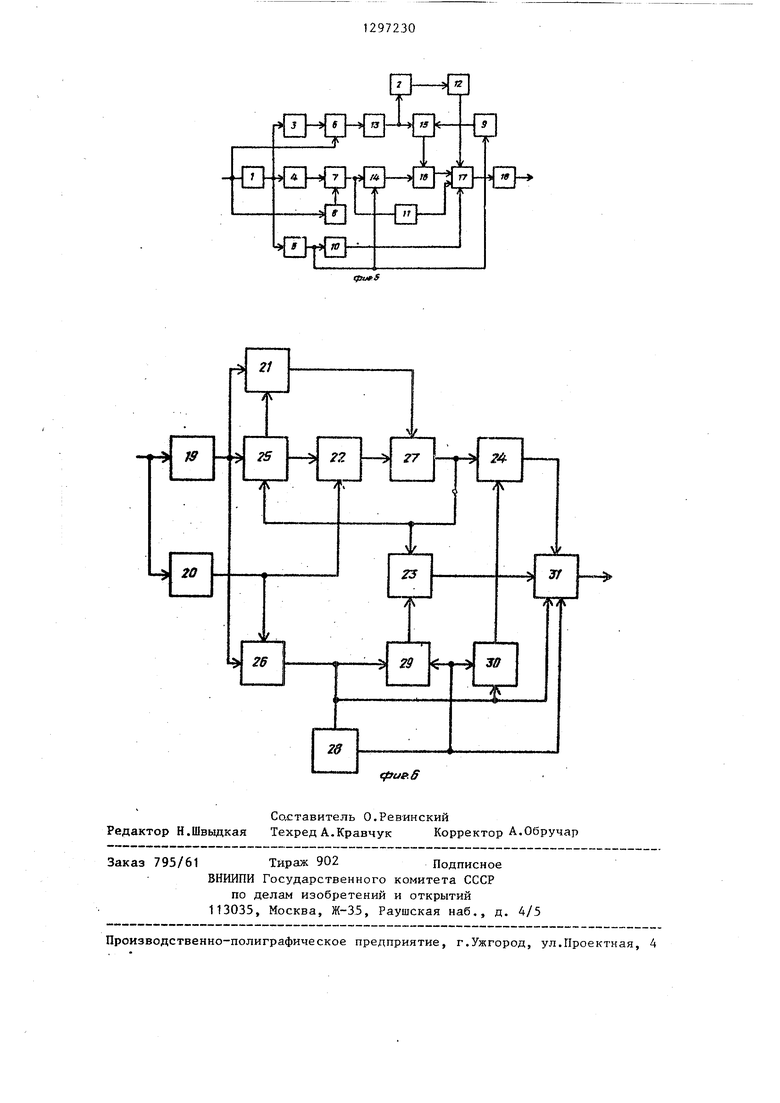

Устройство декодирования сигнала ее (фиг. 6) включает в себя компараторы 19, 20, эле;- енты 11 21 - 24, RS- триггер 25, элементы ИЛИ 26, 27, блок 28 выделения сигнала синхронизации, дешифратор 29 последопательодним из граничных уровнен, соответствующие только тем участкам в передаваемом сигнале, в пределах которых изменение уровня сигнала происходит реже, чем через один тактовый интервал входной цифровой последовательности (фиг. 1 и 2). При использовании предлагаемого способа кодирования длина участков передаваемого сигнала без изменения уровня сигнала не может превышать К тактовых интервало при передаче 1 и К+2 тактовых интервалов при передаче символов О (фиг. 2, 3 и 4). Поэтому уровень низкочастотных компонент в спектре: сигнала меньше, чем при использовании дуобинарного способа кодирования для которого длина участков принимаемого сигнала с одним из граничных уровней может неограниченно возрастать.

Режим самосинхронизации при приеме сигнала обеспечивается путем стабильной подстройки системы синхронизации, поскольку ограничение длины участков без изменения уровня при передаче сигнала, соответствующего последовательностям символов 1 входного цифрового сигнала, гарантирует на приеме получение импульсов следующих не реже чем через К-1, а при передаче последовательностей символов О - не реже,чем через К+1 тактовый интервал;

На практике разбиение последовательности одинаковых символов на блоки производится последовательно.

Устройство кодирования для реализации данного способа формирования сигнала с частотой, не 1фатной полутактовой частоте входного сигнала, включает в себя (фиг. 5) элементы 1, 2 задержки на один тактовый интервал первый и второй дешифраторы 3, 4, элемент 5 задержки на К+2 тактовых интервалов, элементы И 6, 7, элементы НЕ 8, 9, первый, второй и третий, формирователи 10, 11, 12 импульсов.

элемент 13 задержки на 2 тактовых интервала, RS-триггеры 14, 15, элемент ИЛИ 16, логический коь мутатор 17, счетный триггер 18,

Устройство декодирования сигнала (фиг. 6) включает в себя компараторы 19, 20, эле;- енты 11 21 - 24, RS- триггер 25, элементы ИЛИ 26, 27, блок 28 выделения сигнала синхронизации, дешифратор 29 последопательности К-1 символа О, дешифратор 30 последовательности К+1 символа О, сдвиговый регистр 31.

Устройство кодирования работает следующим образом.

ПрИ поступлении на вход устройства последовательности К+2 СИМЕОЛОВ О на выходе второго дешифратора 4 с задержкой в один тактовый интервал появляется импульс обнаружения этой последовательности, который поступает на первый вход элемента И 7, Второй вход этого элемента И 7 через элемент НЕ 8 соединен с информационным входом устройства кодирования. Из-за задержки сигнала в элементе 1 задержки на один тактовый интервал импульс на вьгходе элемента И 7 формируется, только в том случае, если на вход устройства кодирования после последовательности из K-i-2 символов О поступает хотя бы еще один импульс О. В случае появления импульса на выходе элемента И 7 он устанавливает RS-триггер 14 в состояние 1, 25 вателя 12 импульсов осуществляется Сигнал с прямого выхода RS-триггера 14 через элемент ИЛИ 16 поступает на управляющий вход логического коммутатора 17 и подключает к выходу этого коммутатора 17 выходы второго и третьего формирователей 11, 12 импульсов. Одновременно с этим на выходе второго формирователя 11 импуль30

с задержкой на один тактовый интерв входного цифрового сигнала с помогдь элемента 2 задержки, чем обеспечивается изменение .уровня выходного си нала только с второго тактового интервала в блоках для К символов 1 После запуска третьего формирователя 12 импульсов на его вьгходе форми руется последовательность из К им- пульсов, следующих с частотой, в К/(К-1) раз большей тактовой частот входного цифрового сигнала. Эти импульсы через логический коммутатор поступают на вход счетного тригге- Q pa 18, формирующего выходной сигнал

элемента И 7, появляется последовательность К+2 импульсов, следующих с частотой, в (К+2)/(К+1) раз большей тактовой частоты входного цифрового сигнала. Эти импульсы через логический коммутатор 17 поступают на вход счетного триггера 18, который формирует выходной сигнал. Запуск втрого формирователя импульсов 11 происходит калсдый раз при обнаружении вторым дешифратором 4 последовательности К+2 символов О до появления на входе устройства хотя бы одного символа 1. Появление этого символ приводит к тому, что на выходе злеУстановка RS-триггера 15 в состоя ние О осуществляется при появлении на выходе элемента 5 задержки на К+2 45 тактовых интервала символа О. Для последовательности с числом п символов 1, большим и кратным величине К и менение уровня сигнала в последнем блоке К символов 1 не производится

мента 5 задержки на К+2 тактовых ин- 50 из-за невозможности запуска третьего

терзала появляется импульс, который устанавливает RS-триггер 14 в состояние О. При этом независимо от того, какую длину имеет последний блок в последовательности m символов О, выход логического коммутатора 17 отключается от его третьего входа.

При нахождении RS-триггера 14 в состоянии О возможно подключение

формирователя 12 импульсов, поскольк отсутствует импульс сигнала на первом входе элемента И 6. При значении п, большем и не кратном величине К, 55 уровень сигнала в последних тактовых интервалах сигнала К после блока символов 1 входной информации не изменяется из-за отсутствия импульса на втором входе элемента И 6. При

72306

логического коммутатора 17 к первому или второму информационным входам з зависимости от состояния RS-тригге- ра 15. При появлении на входе .первого дешифратора 3 последовательности К символов , после которых также появляется символ 1, происходит установка триггера 15 Б состояние Т с задержкой на два тактовых интервала, которая необходима для выравнивания моментов появления информации на информационных входах логического коммутатора 17. Задержки создается элементом 13 задержки на два тактовых

интервала, а импульс установки RS- триггера 15 в состояние 1 формируется на выходе элемента И 6, При этом к выходу логического коммутатора 17 подсоединяется выход третьего формирователя 12 импульсов, что достигается подачей сигнала с прямого выхода RS-триггера 15 через элемент ИЛИ 16 на управляющий вход логического коммутатора 17. Запуск третьего формиро25 вателя 12 импульсов осуществляется

30

с задержкой на один тактовый интервал входного цифрового сигнала с помогдью элемента 2 задержки, чем обеспечивается изменение .уровня выходного сигнала только с второго тактового интервала в блоках для К символов 1, После запуска третьего формирователя 12 импульсов на его вьгходе формируется последовательность из К им- пульсов, следующих с частотой, в К/(К-1) раз большей тактовой частоты входного цифрового сигнала. Эти импульсы через логический коммутатор 17 поступают на вход счетного тригге- Q pa 18, формирующего выходной сигнал.

Установка RS-триггера 15 в состояние О осуществляется при появлении на выходе элемента 5 задержки на К+2 45 тактовых интервала символа О. Для последовательности с числом п символов 1, большим и кратным величине К, и менение уровня сигнала в последнем блоке К символов 1 не производится

50 из-за невозможности запуска третьего

формирователя 12 импульсов, поскольку отсутствует импульс сигнала на первом входе элемента И 6. При значении п, большем и не кратном величине К, 55 уровень сигнала в последних тактовых интервалах сигнала К после блока символов 1 входной информации не изменяется из-за отсутствия импульса на втором входе элемента И 6. При

значениях n К установка RS-триг- гера 15 в состояние 1 с запуском третьего формирователя 12 импульсов не происходит из-за отсутствия сигнала на одном из входов элемента И 6.

При нахождении RS-триггеров 14,15 в состоянии О выход логического коммутатора 17 подсоединяется к выходу первого формирователя 10 импульсов, который формирует импульсы, соответствующие символам О входной инфор20

нации. Тактовый интервал следования импульсов равен тактовому интервалу входного цифрового сигнала. При под- f5 ключении входа счетного триггера 18 к выходу первого формирователя 10 импульсов изменение уровня выходного сигнала осуществляется по правилу формирования дуобинарного кода.

В устройстве декодирования (фиг,6) входной сигнал поступает параллельно на входы первого и второго компараторов 19, 20, в которых принимается рен ение о наличии или отсутствии в анализируемом тактовом интервале импульсов сигнала с частичным откликом. На выходе компаратора 19 сигнал появляется при обнаружении импульсов

элемента И 24 поступает сигнал с вы- хода дешифратора 30, в результате чего появляется импульс на входе установки символа О в первой ячейке сдвигового регистра 31, и в эту ячейку записывается символ О. 10 В случае поступления на вход устройства через К+1 тактовый интервал импуль.са с верхним граничным уровнем запись символа О в первую ячейку памяти сдвигового регистра 31 осуществляется аналогично, но импульс с выхода компаратора 19 поступает на вход элемента И 24 через элемент И 21 и элемент ИЛИ 27. В дальнейшем при поступлении на вход устройства импульсов, которые разделены (К+1)-м тактовым интервалом и которые имеют различные уровни, процесс записи символа О в первую ячейку памяти сдвигового регистра 31 повторяется анало- 25 гично.

При появлении на входе устройства импульсов с разными граничными уровнями при условии, что эти импульсы

с верхним граничным уровнем, а на вы-зо Разделены (К-1)-м тактовым интерва- ходе компаратора 20 - с нижним гра- лом, сигнал на выходе дешифратора 30 ничкым уровнем. При появлении импуль- последовательности К+1 символа О

са на выходе компаратора 19 происходит установка RS-триггера 25 в состояние 1 и сигнал с прямого выхода этого триггера поступает на первый вход элемента И 22. Этот же импульс через элемент ИЛИ 26 поступает на вход дешифратора 29 последовательности К+1 символа О, дешифратора 30 последовательности К+1 символа 0 % вход блока 28 выделения сигнала синхронизации и записывается в первую ячейку памяти сдвигового регистра 31,

35

40

отсутствует, но формируется импульс на выходе дешифратора 29. При этом и 5пульс с выхода элемента ИЛИ 27 проходит через элемент И 24 и поступает на вход установки символов

1

в первых К ячейках памяти сдвигового регистра 31. В первую ячейку памяти этого регистра записывается символ 1, а в следу1ощ1гх; К-1 ячейках символы О заменяются символами 1. В результате этого в устройстве декодирования происходит восстановление

содержащего. К+2 ячеек памяти. Продай-45 последовательностей стшволов 1 с жение информации по сдвиговому регистру 31, в дешифраторе 29 последовательности К-1 символа О и дешифраторе 30 последовательности К+1 символа О осуществляется сигналом тактовой частоты с выхода блока 28 выделения сигнала синхронизации. При появлении на входе устройства через (К+1)-й тактовый интервал после им50

числом символов . Для импульсов входного сигнала с одинаковыми граничными уровнями, разделенных (К+1)-ми или {К-1)-ми тактовыми интервалами, установка символа О или -символа

1 в первую ячейку и с1-1мволов 1 в следующие К-1 ячейки памяти сдвигового регистра 31 не происходит из-за отсутствия сигнала на входах элемен- пульса с верхним граничным уровнем, та ИЛИ 27 (при повторном появлении импульса с нижним граничным урон- импульса на выходе компаратора 19 нем на выходе компаратора 20 формиру- отсутствует сигнал на втором входе ется сигнал, который после прохожде- элемента И 21, а при повторном появ- ния элемента И 22 и элемента ИЛИ 27 лении импульса на выходе компаратопоступает на первый вход элемента И 24 и устанавливает RS-триггер 25 в положе 1 1 е

О

При этом на второй вход

элемента И 24 поступает сигнал с вы- хода дешифратора 30, в результате чего появляется импульс на входе установки символа О в первой ячейке сдвигового регистра 31, и в эту ячейку записывается символ О. В случае поступления на вход устройства через К+1 тактовый интервал импуль.са с верхним граничным уровнем запись символа О в первую ячейку памяти сдвигового регистра 31 осуществляется аналогично, но импульс с выхода компаратора 19 поступает на вход элемента И 24 через элемент И 21 и элемент ИЛИ 27. В дальнейшем при поступлении на вход устройства импульсов, которые разделены (К+1)-м тактовым интервалом и которые имеют различные уровни, процесс записи символа О в первую ячейку памяти сдвигового регистра 31 повторяется анало- гично.

отсутствует, но формируется импульс на выходе дешифратора 29. При этом и 5пульс с выхода элемента ИЛИ 27 проходит через элемент И 24 и поступает на вход установки символов

1

в первых К ячейках памяти сдвигового регистра 31. В первую ячейку памяти этого регистра записывается символ 1, а в следу1ощ1гх; К-1 ячейках символы О заменяются символами 1. В результате этого в устройстве декодирования происходит восстановление

последовательностей стшволов 1 с

числом символов . Для импульсов входного сигнала с одинаковыми граничными уровнями, разделенных (К+1)-ми или {К-1)-ми тактовыми интервалами, установка символа О или -символа

1 в первую ячейку и с1-1мволов 1 в следующие К-1 ячейки памяти сдвигового регистра 31 не происходит из-за отсутствия сигнала на входах элемен- та ИЛИ 27 (при повторном появлении импульса на выходе компаратора 19 отсутствует сигнал на втором входе элемента И 21, а при повторном появ- лении импульса на выходе компаратоpa 20 - на первом входе элемента И 22) . В других случаях установка не происходит из-за отсутствия сигнала на выходах дешифраторов 29 и 30.

Таким образом, данный способ без внесения избыточности, перехода к пе- .редаче многоуровневого сигнала и введения блочной синхронизации на приеме обеспечивает повышение помехоустойчивости при высокой удельной скорости передачи цифровой информации на основе уменьшения искажений сигнала из-за низкочастотной межсимвольной интерференции и получения самосинхронизации на приеме.

Формула изобретения 1. Способ кодирования сигнала с

,1,2..,, начиная с середины второго до серединь К-го такта, осущесчв-- ляют изменением К раз уровня двухуровневого сигнала, после чего прове5 ряют условие (п-К) и в случае его выполнения повторяют описанную процедуру J-1 раз (j 1,2...) , до тех пор, пока условие (n-jK) не пере- станет выполняться, после чего на

10 оставшемся интервале длительностью (n-jK) оставляют уровень двухуровневого сигнала неизменным, кодирование последовательности m нулевых символов длительностью тТ для случая

15 с середины первого до середины (К+1)-го такта осуществляют изменением К+2 раз уровня двухуровневого сигнала, после чего проверяют условие т- -(К+2)-Т(К+2)Т и в случае его вычастичньм откликом для передачи циф- 20 полнения повторяют описанн то процеду- ровой информации, заключающийся в ко- РУ Раз (,...), до тех пор, по- дировании каждого нулевого символа ка условие m-Z(K+2)J Т(К+2). Т не

перестанет выполняться, после чего на оставшемся интервале длительностью

изменяется в середине такта, и коди- m-I(K+2)l.T ().Т изменяют уро- ровании единичных символок длитель- вень двухуровневого сигнала в середине каждого такта.

2. Способ по п. 1,отличаю- щ и и с я тем, что изменения уровня

что, с целью.повышения помехоустои- - двухуровневого сигнала, осуществляе- чивости, кодирование последователь- случае выполнения условий нести п единичных символов длитель- (n-jK) или т-Г(К+2) Т(К+2)-Т, ностью пТ, для случая , ,

длительностью, равной такту Т, двухуровневым сигналом, уровень которого

ностью Т двухуровневым сигналом, уровень которого в пределах такта не меняется, отличающийся тем,

„ зл с целью, повышения помехоустои-

производят с интервалом ОТ Т/2 до Т.,

Г О11ОООООО1О7 711 7 О О 7 7 О .

,1,2..,, начиная с середины второго до серединь К-го такта, осущесчв-- ляют изменением К раз уровня двухуровневого сигнала, после чего проверяют условие (п-К) и в случае его выполнения повторяют описанную процедуру J-1 раз (j 1,2...) , до тех пор, пока условие (n-jK) не пере- станет выполняться, после чего на

оставшемся интервале длительностью (n-jK) оставляют уровень двухуровневого сигнала неизменным, кодирование последовательности m нулевых символов длительностью тТ для случая

с середины первого до середины (К+1)-го такта осуществляют изменением К+2 раз уровня двухуровневого сигнала, после чего проверяют условие т- -(К+2)-Т(К+2)Т и в случае его выдвухуровневого сигнала, осуществляе- случае выполнения условий (n-jK) или т-Г(К+2) Т(К+2)-Т,

производят с интервалом ОТ Т/2 до Т.,

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ записи цифровой информации | 1982 |

|

SU1042074A1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| Устройство для передачи и приема дискретных сообщений | 1983 |

|

SU1095220A1 |

| Устройство для адаптивного кодирования сигналов цифровой магнитной записи | 1985 |

|

SU1307478A1 |

| СПОСОБ КОДИРОВАНИЯ ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ И УСТРОЙСТВО КОДИРОВАНИЯ | 2005 |

|

RU2281608C1 |

| Устройство для контроля длительности импульсов | 1980 |

|

SU901949A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2261531C1 |

| Система передачи дискретной информации | 1985 |

|

SU1325719A1 |

| Способ передачи-приема информации и устройство для его осуществления | 1989 |

|

SU1783630A1 |

| Способ записи цифровой информации | 1983 |

|

SU1112393A2 |

Изобретение относится к вычислительной технике. Его использование в системах передачи цифровой информации по каналам с межсимвольной интерференцией позволяет повысить помехоустойчивость. Способ заключается в кодировании каждого нулевого символа входного кода длительностью, равной такту Т, изменением:уровня двухуровневого сигнала в середйн ё такта и в кодировании единичных символов той же длительности неизменным уровнем двухуровневого сигнала. Благодаря замене этих сигналов при передаче длинных последовательностей единиц или нулей на сигналы со специальным законом изменения уровня двухуровневого сигнала уменьшаются искажения из-за низко- с частотной межсимвольной интерференции и обеспечивается самосинхронизация на приеме. 1 з.п. ф-лы, 6 ил. (Л с со ю со о

VX

Фие.

7

Н-

Составитель О.Ревииский Редактор Н.Швьщкая Техред А.Кравчук Корректор А.Обручар

Заказ 795/61 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Способ акустической дефектоскопии изделий | 1987 |

|

SU1578635A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Былянски П.Ингрем Д | |||

| Цифровые системы передачи, М.: Связь, 1980, с | |||

| Крутильный аппарат | 1922 |

|

SU234A1 |

Авторы

Даты

1987-03-15—Публикация

1985-02-25—Подача