Изобретение относится к импульсной технике и может применяться в различных фазово-импульсных системах автоматического регулирования в качестве нуль-органа. Известны устройства для определения угла сдвига фаз двух импульсных последовательностей 13. Однако они подвержены сбоям при совпадении входных импульсов. Известный фазовый детектор 12 свободен от этого недостатка, так ка входные импульсы поступают на раздел ные запоминающие элементы - двоичные многоразрядные счетчики с равными N. Счетчики обесмодулями N ., N ij печивают запоминание числа поступивших входных импульсов. Сдвиг фаз определяется с помощью элемента сравнения, в качестве которого используется (п+1)-разрядный вычитающий блок который определяет разность кодов от счетчиков. Эта разность при отсут ствии помех и пропуска импульсов во входных последовательностях принимае следующие значения: 0,1.или 0,-1. Пр наличии пропуска m входных импульсов, опорных или поступающих с задержкой относительно опорных на выбо ке объемом N при условии, что m N, эта разность увеличивается и в установившемся режиме работы детектора при прекращении пропусков в данной выборке) принимает значения m,(m-fl) или -т, -(т+1).Код разностипреобразовывается в напряжение и подается через фильтр на выход детектора. Таким образом, известный фазовый детектор при наличии пропусков работает неточно, что является его существенным недостатком. Целью изобретения является повышение точности работы фазового детектора при наличии пропуска импульсов в одной из входных последовательностях импульсов. Указанная цель достигается тем, что в фазовый детектор, содержащий два счетчика, два элемента И, триггер, цифро-аналоговый преобразователь, фильтр, причем первый вход фазового детектора соединен с суммирующим входом реверсивного счетчика, выход первого элемента И соединен с единичным входом триггера, выход суммирующего счетчика - с первым входом первого элемента И, выход цифро-аналогового преобразователя - с входом фильтра, выход которого соединен с выходом фазового детектора.

введены три элемента И, элемент ИЛИ, два формирователя импульсов, дешифратор, элемент задержки, при этом второй вход фазового детектора соединен с вычитающим входом реверсивного счетчика и с входом третьего элемента И, другой вход которого 1соединен с первым входом фазового детектора, а выход - с входом первого формирователя импульсов, выход которого соединен со входом установки О реверсивного счетчика и со входом запрета дешифратора, первый и второй выходы реверсивного счетчика соединены соответственно с первым и вторым входами дешифратора, первый и второй выходы которого- соединены соответственно со вторыми входами первого и второго элементов И и со входами элемента ИЛИ, выход которого соединен со входом циф ро-аналогового преобразователя и со входом суммирующего счетчика, выход второго элемента И - с нулевым входом триггера, единичный выход которого соединен со знаковым входом цифро-аналогового преобразователя и с первым входом чет.вертого элемента И, а нулевой - с первым входом пятого элемента И, третий выход дешифратора соединен с выходом индикации пропусков и через последовательно соединенные второй формирователь импульсов и элемент задержки - со вторыми входами четвертого и пятого элементов И, выходы которых соединены соответственно со входом установки реверсивного счетчика в состояние 01 и со входом установки в состояние 11.;

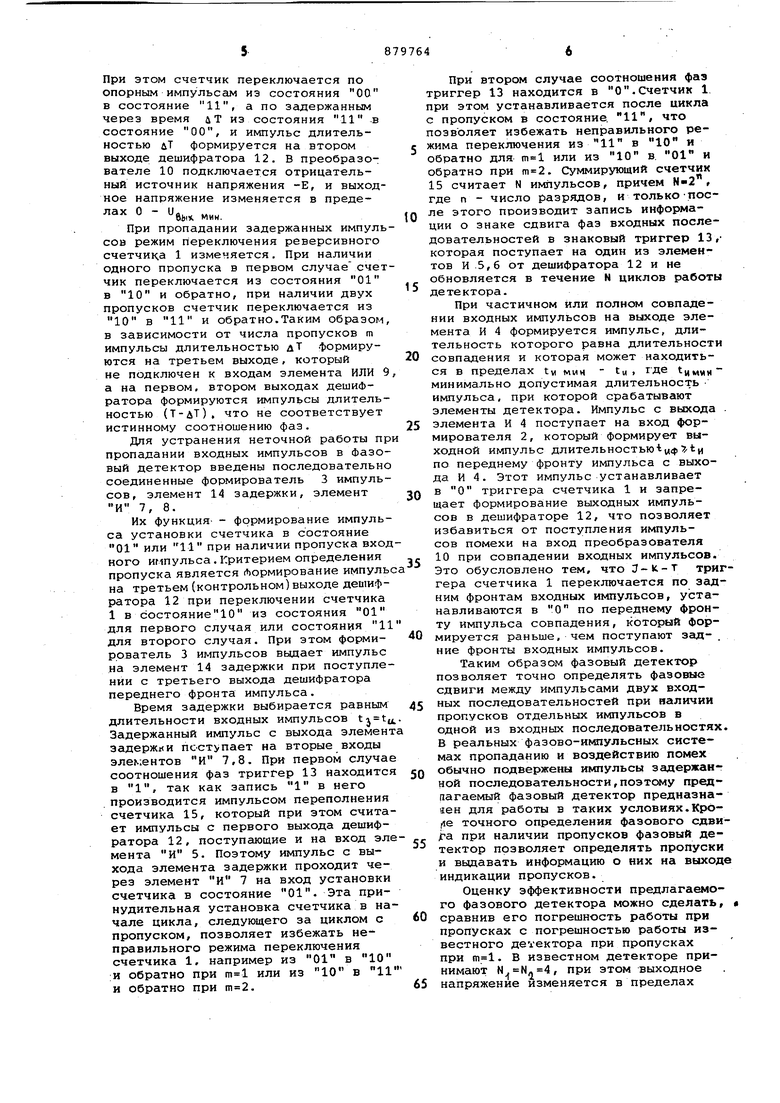

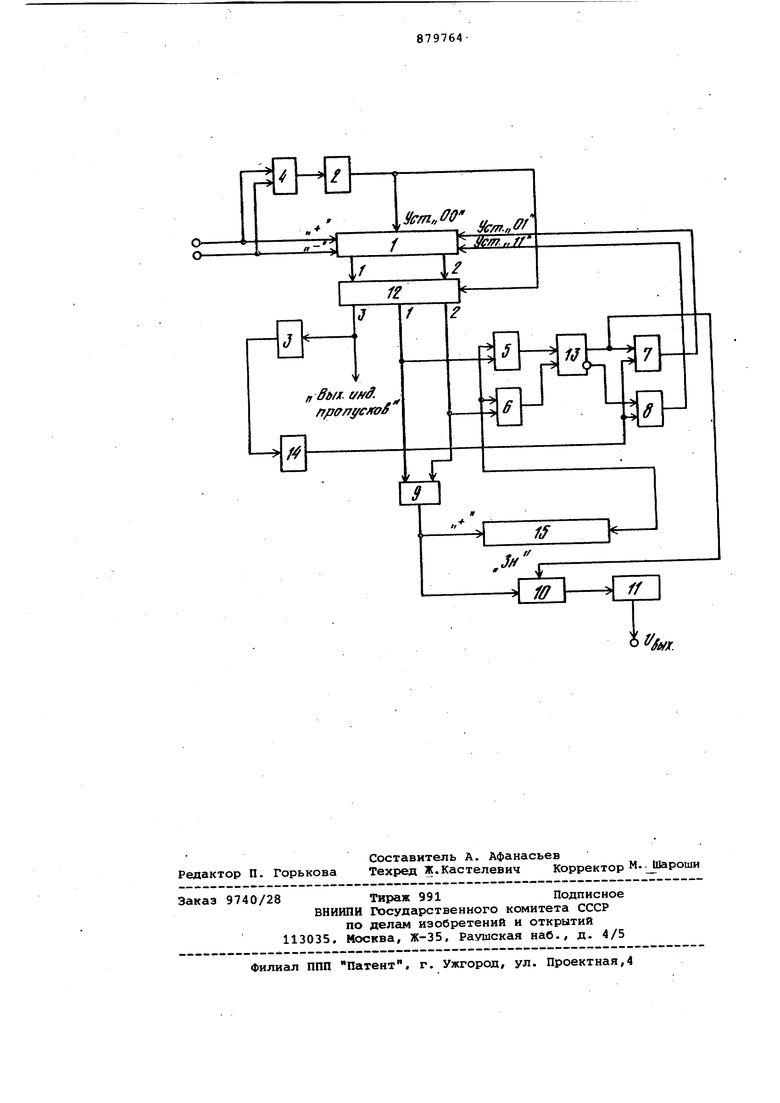

На чертеже приведена схема фазового детектора.

Фазовый детектор содержит реверсивный счетчик 1, формирователи 2,3 импульсов, элементы И 4,5,6,7,8,элемент ИЛИ 9, цифро-аналоговьй преобразователь 10. фильтр 11, дешифратор 12, триггер 13, элемент 14 задержки, суммирующий счетчик 15.

Первый и второй входы фазового детектора соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика 1 и со входом элемента И 4, выход которогосоединен со входом формирователя 2, выход которого - со входом сброса в О счетчика 1 и со входом запрета дешифратора 12, первый и второй выходы реверсивного счетчика 1 соединены соответственно с первым и вторым в.ходами дешифратора 12, первый и второй выходы которого соединены соответственно со вторыми входами элементов И 5 и б и со входами элемента ИЛИ 9, выход которого соединен со входом суммирующего счетчика 15 и со входом цифро-аналогового преобразователя 10, выход которого через фильтр 11 соединен с выходом фазового детектора, третий выход дешифратора - с вьвсодоМ

индикации пропусков и через формирователь 3 импульсов и элемент 14 задержки со вторыми входами элементов И 7,8, выходы которых соединены соответственно со входами установки реверсивного счетчика 1 в состояния 01 и 11, а первые входы которых соединены соответственно с единичным и нулевым выходами триггера 13, единичный и нулевой входы которого соответственно с выходами элементов И 5 и 6, первые входы которых соединены с выходом суммирующего счетчика 15, единичный выход триггера 13 соединен с знаковым входом цифроаналогового преобразователя 10.

Положительные импульсы опорной и Задержа нной последовательности с одинаковыми частотами f f/ f поступают на входы-фазового детектора. Рассмотрим сначала случай,когда опорные импульсы подаются на первый вход и далее на суммирующий вход реверсивного счетчика 1, а задержанные подаются на его вычитающий вход. Счетчик 1 имеет два разряда и соответственно четыре состояния: 00, 01, 10, 11. Опорные импульсы переключают счетчик в каждом цикле из состояния 00 в состояние 01, а задержанные импульсы нерез время дТ после этого переключения возвращают его в прежнее состояние. При этом на первом выходе дешифратора 12 формируется импульс длительностью U Т и амплитудой Ug, который поступает через элемент ИЛИ 9 .на вход цифро-аналогового преобразователя (ЦАП) 10, имеющего один разряд, кроме знакового.

Знаковый разряд состоит из триггера, ключа, двух эталонных источников напряжения 4-Е, -Е/

Подключение +Е происходит при наличии 1 в знаковом триггере, а подключение -Е при наличии О.

ЦАП 10 преобразовывает импульс амплитудой U(3 в импульс амплитудой и - kU о, где k задается исходя из U(5 и требуемого диапазона представления выходного напряжения

вblx мин ftыx макс)Для данного случая соотношение фаз Uftbiyi изменяется в пределах вbtx wflKC. Это Ьбеспечн.вается подключением к ключу-формирователю источника положительного напряжения +Е. Фильтр 11 интегрирует напряжение на его обратно пропорционально скважности импульсов, поступающих на

его вход Q 5 -у, а так как частоты

0 входные f , f f и соответственно периоды Т, TI равны, то Uftbin пропорционально ДТ.

Рассмотрим случай, когда на первый вход подаются задержанные импульсы, а на второй вход опорные.

При этом счетчик переключается по опорным импульсам иэ состояния 00 в состояние 11, а по задержанным через время и Т из состояния 11 -в состояние 00, и импульс длительностью дТ формируется на втором выходе дешифратора 12. В преобразователе 10 подключается отрицательный источник напряжения -Е, и выходное напряжение изменяется в преде ° - в.Ы. мин.

При пропадании задержанных импульсов режим переключения реверсивного счетчика 1 изменяется. При наличии одного пропуска в первом случаесчетчик переключается из состояния 01 в 10 и обратно, при наличии двух пропусков счетчик переключается из 10 в 11 и обратно.Таким образом, в зависимости от числа пропусков m импульсы длительностью дТ Формируются на третьем выходе, который не подключен к входам элемента ИЛИ 9 а на первом, втором выходах дешифратора формируются импульсы длительностью (Т-дТ), что не соответствует истинному соотношению фаз.

Для устранения неточной работы пр пропадании входных импульсов в фазовый детектор введены последовательно соединенные формирователь 3 импульсов, элемент 14 задержки, элемент И 7, 8.

Их ФУНКЦИЯ - формирование импульса установки счетчика в состояние 01 или 11 при наличии пропуска входного импульса,Критерием определения пропуска является Нормирование импульс на третьем(контрольном)выходе дешифратора 12 при переключении счетчика 1 в состояние 10 из состояния 01 для первого случая или состояния 11 для второго случая. При этом формирователь 3 импульсов вьщает импульс на элемент 14 задержки при поступлении с третьего выхода дешифратора переднего фронта импульса.

Время задержки выбирается равным длительности входных импульсов tj tu, Задержанный импульс с выхода элемент задержки nccTvnaer на вторые входы элементов И 7,8. При первом случае соотношения фаз триггер 13 находится в 1, так как запись 1 в него производится импульсом переполнения счетчика 15, который при этом считает импульсы с первого выхода дешифратора 12, поступающие и на вход элемента И 5. Поэтому импульс с выхода элемента задержки проходит через элемент И 7 на вход установки счетчика в состояние 01. Эта принудительная установка счетчика в начале цикла, следующего за циклом с пропуском, позволяет избежать не правильного режима переключения счетчика 1, например из 01 в 10 ;и Обратно при или иэ 10 в 11 и обратно при .

При втором случае соотношения фаз триггер 13 находится в О.Счетчик 1 при этом устанавливается после цикла с пропуском в состояние. 11, что позволяет избежать неправильного режима переключения из 11 в 10 и обратно для или из 10 в. 01 и обратно при . Суммирующий счетчик 15 считает N импульсов, причем N-2 , где п - число разрядов, и только-после этого производит запись информаoции о знаке сдвига фаз входных последовательностей в знаковый триггер 13,которая поступает на один из элементов И 5,6 от дешифратора 12 и не обновляется в течение N циклов работы

5 детектора.

При частичном или полном совпадении входных игтульсов на выходе элемента И 4 формируется импульс, длительность которого равна длительности

0 совпадения и которая может находиться в пределах tvi мин - tu , где IHMVIM минимально допустимая длительность импульса, при которой срабатывают элементы детектора. Импульс с выхода . элемента И 4 поступает на вход фор5мирователя 2, который формирует выходной импульс длительностью „({, 7 t и

по переднему фронту импульса с выхода И 4. Этот импульс устанавливает в О триггера счетчика 1 и запре0щает формирование выходных импульсов в дешифраторе 12, что позволяет избавиться от поступления импульсов помехи на вход преобразователя 10 при совпадении входных импульсов.

5 Это обусловлено тем, что Л-И-Т триггера счетчика 1 переключается по задним фронтам входных импульсов, устанавливаются в О по переднему фронту импульса совпадения, который фор0мируется раньше, чем поступают задние фронты входных импульсов.

Таким образом фазовый детектор позволяет точно определять фазовые сдвиги между импульсами двух входных последовательностей при наличии

5 пропусков отдельных импульсов в одной из входных последовательностях. В реальных фазово-и1«Н1ульсных системах пропаданию и воздействию помех обычно подвержены импульсы задержан0ной последовательности,поэтому предлагаемый фазовый детектор предназначен для работы в таких условиях.Кроfie точного определения фазового сдвиjra при наличии пропусков фазовый де5тектор позволяет определять пропуски и вьщавать информацию о них на выходе индикации пропусков.

Оценку эффективности предлагаемого фазового детектора можно сделать,

0 сравнив его погрешность работы при пропусках с погрешностью работы известного детектора при пропусках при . В известном детекторе принимают N,N.4, при этом выходное

5 напряжение изменяется в пределах 0-3 В. Для случая т«1 в циклах после пропуска разность кодов от счетчиков принимает значения 1, 2 вместо 0,1, причем значение 2 существует в тече ние йТ и определяет Фазовый сдвиг. Принимаем аТ 0,5 Т, тогда « « 1,5 В, а должно быть равно 0,5 В, т.е. абсолютная погрешность в циклах после пропуска uUgti 1,0 В, а .относительная , 200%, причем она увеличивается при увеличении т. В фазовом детекторе погоешность от пропусков равна О благодаря принудительной установке реверсивного счетчика в состояние 01 при положительном фазовом сдвиге и в состояние 11 при отрицательном фазовом сдвиге. Формула изобретения Фазовый детектор, содержащий два счетчика, два элемента И, триггер, цифро-аналоговый преобразователь, фильтр, причем первый вход Фазового детектора соединен с суммирующим вхо дом реверсивного счетчика, выход пер вого элемента И соединен с единичным входом триггера, выход суммирующего счетчика - с первым входом первого элемента И, выход которого соединен с единичным входом триггера, выход цифро-аналогового преобразователя с входом фильтра, выход которого сое динен с выходом Фазового детектора, отличающийся тем, что, с целью повышения точности его работ при наличии пропусков импульсов и помех, в него введены три элемента И элемент ИЛИ, два формирователя импульсов, дешифратор, элемент задержк при этом второй вход фазового детектора соединен с вычитающим входом реверсивного счетчика и со входом третьего элемента И, другой вход которого соединен с первым входом фазового детектора, а выход - с входом первого формирогателя импульсов, выход которого соединен со входом установки в О реверсивного счетчика и со входом запрета дешифратора, первый и второй входы которого соединены соответственно с первым и вторым выходами реверсивного счетчика, а первый и второй выходы соединены соответственно со вторыми входами первого и второго элементов И и со входами элемента ИЛИ, выход которого соединен со входом цифро-аналогового преобразователя и со входом суммирующего счетч.ика, выход второго элемента И с нулевым входом триггера, единичный выход которого соединен со знаковым входом цифро-аналогового преобразователЯИ с первым входом четвертого элемента И, а нулевой - с первым входом питого элемента И, третий выход дешифратора соединен с выходом индикации пропусков и через последовательно соединенные второй формирователь импульсов и элемент задержки со вторыми входами четвертого и пятого элементов И, выходы которых соединены соответственно со входом устанраки реверсивного счетчика в состояние 01 и со входом установки в состояние 11. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 601628, кл. 6 01 R 25/00, 1978. 2.Заявка Японии Н 53-5107, 110 Н 2 1978.

т.

ycm.ffO

ycm.,.fff

ffCfff.., ff

1/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа периодических сигналов | 1981 |

|

SU978066A1 |

| Устройство для определения моментов экстремумов гармонических сигналов | 1981 |

|

SU1004899A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Преобразователь перемещения в код | 1983 |

|

SU1091205A1 |

| Устройство для виброрезонансных испытаний изделий | 1984 |

|

SU1249367A1 |

| Устройство для измерения коэффициента затухания упругих волн при акустическом каротаже | 1981 |

|

SU995046A1 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Цифровой частотный детектор | 1979 |

|

SU815863A1 |

| ЭЛЕКТРОННЫЙ ПРИБОР ДЛЯ ОПРЕДЕЛЕНИЯ СКОРОСТИ, ПРОЙДЕННОГО РАССТОЯНИЯ И ВРЕМЕНИ | 1965 |

|

SU170776A1 |

| Вихретоковый дефектоскоп | 1983 |

|

SU1103141A1 |

-

t, Bb/x. vffS. /jpff/rffCfioS

//

KA 10 ц //

1

.

Авторы

Даты

1981-11-07—Публикация

1980-01-28—Подача