I

Изобретение относится к импульсной тех-:нике и может использоваться, например, в качестве формирователя опорного напряжения для демодуляции и модуляции сигналов в двухканальиых системах с амплитудно-фазовой модуляцией и одноканальным управле; нием.

Известен формирователь импульсов, содержащий генератор пилообразных импульсов, источник постоянного напряжения, два. пороговых устройства., два генератора прямоугольных импульсов, выходы источников постоянного напряжения н пилообразных импульсов подключены ко входу двух пороговых устройств, выходы которых подключены ко входу двух генераторов прямоугольных импульсов |1.

Недостатком такого формирователя импульсов является низкая точность относи тельного фазового сдвига входного и выходного сигналов при дрейфе частоты входного снгнала.

Наиболее близким по своей сущности техническим рещением к предлагаемому изобретению является формирователь импульсов,: который включает в себя два генератора нмпульсов Г1 и Г2, частоты котефых выбраны так, что частота Г1, по крайней мере, на

порядок выше частоты входного сигнала, а частота Г2 на порядок выше частоты Г1, две переменные схемы ПС1 и ПС2 для измерения длительности входного сигнала в двойном коде с использованием сигналов Г1 н F2, схему умножения, на вход которой

5 подается сигнал с ПС1 н сигнал управления кратностью умноження, задаваемой с пульта управлення через схему формирования сигнала кратносгн, схему запоминания, на вход которой поступает сигнал с выхода умножителя и управляющий сигнал от триг repia, схему сравнения, на выходе которой формируется импульс задержки, при условии совпадения сигналов на входах от ПС2 и схемы запоминания. Относительная дли; тельность задержки определяется отноше.- нием частотгенераторов Г1 н Г2, умноженным на коэффициент кратности (2).

Недостаток известного устройства состоит в зависимости фазового сдвига выход. ных импульсов относительно входных при 30 изменении частоты входного снгнала.

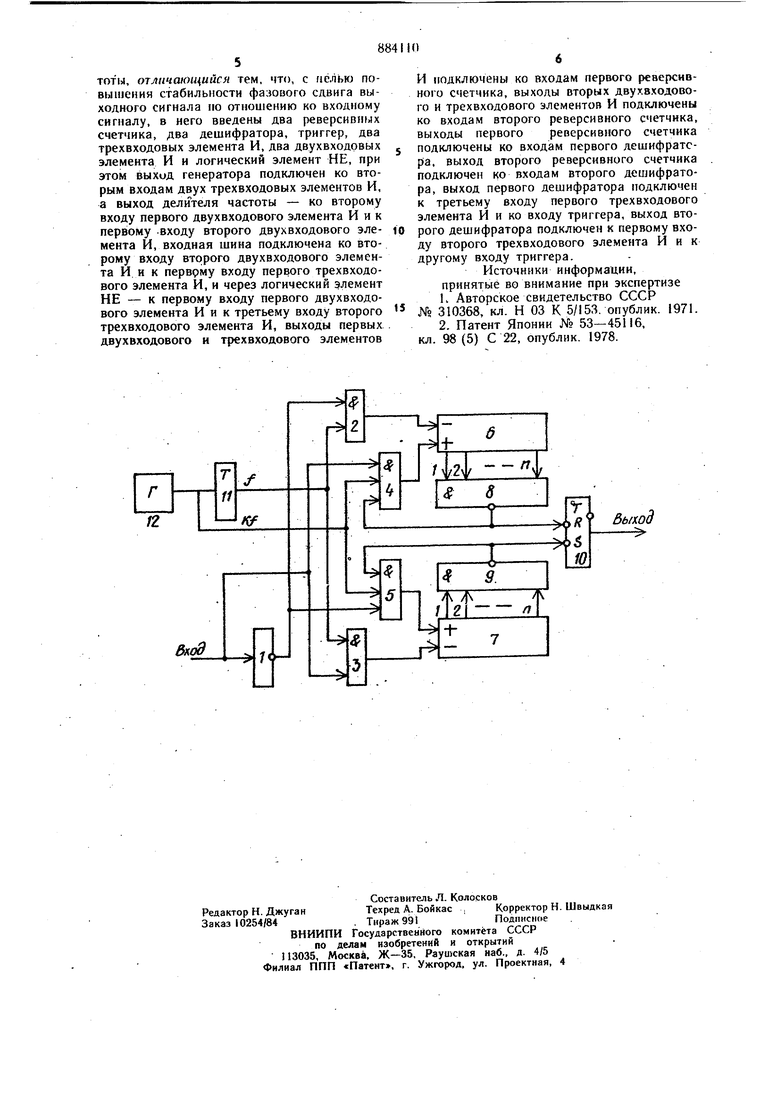

Цель изобретения - повышение стабнль: ностн фазового сдвнга выходногосигнала по отношению ко входному снгналу. Поставленная цель достигается тем, что в формирователь импульсов, содержащий генератор, подключенный к делителю частоты, введены два реверсивных счетчика, два дешифратора, триггер, два трехвходовых элемента И, два двухвходовых элемента И и Логический элемент НЕ, при этом выход генератора подключен ко вторым входам двух трехвходовых элементов И, а выход делителя частоты - ко второму входу первого двухвходового элемента И и к первому входу второго двухвходового элемента И, входная шина подключена ко второму входу второго двухвходового элемента И и к первому входу первого трехвходового элемента И и через логический элемент НЕ - к первому входу первого двухвходового элемента И и к третьему входу второго трехвходового элемента И, выходы первых двухвходового и трехвходового элементов И подключены ко входам первого реверсивного счетчика, выходы вторых двухвходового и трехвходового элементов И подключены ко входам втррого реверсивного счетчика, выходы первого реверсивного счетчика подключены ко входам первого дешифратора, выход второго реверсивного счетчика подключен к входам второго дешифратора, выход первого дешифратора подключен: к третьему входу первого трехвходового элемента И и ко входу триггера, выход второго дешифратора под ключен к первому входу второго трехвходового элемента И и - к другому входу триггера.. . На чертеже представлена структурная схема формирователя импульсов. Устройство состоит из логического элемента НЕ 1, двух двухвходовых элементов И 2 и 3, двух трехвходовых Элементов И 4 и 5, двух реверсивных счетчиков 6 и 7, двух дешифраторов 8 и 9 на элементах И- НЕ, триггера 10, делителя частоты 11, генератора 12. Выход генератора 12 подключен ко вторым входам двух трехвходовых элементов И и через делитель частоты 11 - ко второму входу первого двухвходового элемента И 2 и к первому входу второго двухвходового элемента И 3. Вход устройства 1подключен ко второму входу второго двухвходового элемента И 3, к первому входу первого трехвходового элемента И 4 и через логический элемент НЕ 1 - к первому входу первого двухвходового элемента И 2 и к третьему входу второго трехвходового элемента И 5. Выходы перрых двухвходового и трехвходового элементов И 2 и 4 подключены ко входам первого реверсивного счетчика 6, выходы вторых двухвходового и ,, -„ трехвходового элементов И 3 и 5 - ко входам второго реверсивного счетчика 7. Выходы первого реверсивного счетчика 6 подключены ко входам первого дешифратора 8, выходы второго реверсивного счетчика 7 - ко входам второго дешифратора 9. Выход первого дешифратора 8 подключен к третьему входу первого трехвходового элемента И 4 и ко входу триггера 10, выход второго дешифратора 9 подключен к первому вх&ду второго трехвходового элемента И 5 и к другому входу триггера 10, выход которого является выходом устройства. Подлежащий сдвигу сигнал поступает непосредственно на сигнальные входы элементов 3 и 4 и через первый 4 трехвходовый и второй 3 двухвходовый элементы И, и через элемент НЕ I - на сигнальные входы первого 2 двухвходового н второго 5 трехвходового элементов И. Пусть сначала выходной триггер находится в нулевом состоянии, а в счетчиках 6 и 7 записаны максимальные числа (т. е. во всех счетчика занесены единицы), Следовательно, на выходах дешифраторов 8 и 9 будут сигналы с уровнем логического нуля, и схемы 4 и 5 будут закрыты по третьим входам. Пусть на сигнальный вход поступает сигнал с уровнем логической единицы, элемент И 3 открывается и через него счетные импульсы поступают на вычитающий вход счетчика 7. Как только содержимое счетчика уменьшается на единицу, на выходе дешифратора 9 появляется открывающий элемент 5 сигнал. Однако эта схема остается закрытой по сигнальному входу. Содержимое счетчика 7 уменьшается в течение положительного полупериода входного сигнала. В тот момент, когда на сигнальном входе окажется отрицательная полуволна, элемент И 3 закрывается, но открываются элементы И 2 и 5. Через элемент ,И 2 счетные импульсы посту вычитающий вход счетчика 6 (в счетчике 6 начинается процесс, аналогичный процессу в счетчике 7, но с задержкой на полупериод входного сигнала), а через элемент И 5 импульсы поступают на суммирующий вход счетчика 7. В этот момент на выходе дешифратора 9 сигнал равняется логическому нулю, вследствие чего элемент И 5 закрывается, а выходной триггер опрокидывается в единичное состояние. Обратно в нулевое состояние триггер возвращается через полупериод час; . -„- . -о тоты несущен с помощью деш ифратора 8, когда закончится аналогичный процесс в счетчике 6. Таким образом, процессы вычитания и суммирования счетных импульсов в счетчиках 6 и 7 повторяются со сдвигом на часть полупериода входного сигнала, а на выходе триггера 10 будет сигнал, аналогичный входному, но сдвинутый по фазе относительно входного сигнала, Формула изобретения Формирователь импульсов, содержащий генератор, подключенный к делителю частоты, отличающийся тем, что, с пёпью повы1иения стабильности фазового сдвига выходного сигнала но отношению ко входному сигналу, в него введены два реверсивных счетчика, два дешифратора, триггер, два трехвходовых элемента И, два двухвходрвых элемента И и логический элемент НЕ, при этом выход генератора подключен ко вторым входам двух трехвходовых элементов И, а выход делителя частоты - ко второму входу первого двухвходового элемента Инк первому -входу второго двухвходового элемента И, входная шина подключена ко второму входу второго двухвходового элемента И и к перврму входу первого трехвходового элемента И, и через логический элемент НЕ - к первому входу первого двухвходового элемента И и к третьему входу второго трехвходового элемента И, выходы первых двухвходового и трехвходового элементов

И подключены ко входам первого реаерснвного счетчика, выходы вторых двухвходового и трехвходового элементов И подключены ко входам второго реверсивного счетчика, выходы первого реверсивного счетчика подключены ко входам первого дешифратора, выход второго реверсивного счетчика подключен ко входам второго дешифратора, выход первого дешифратора подключен к третьему входу первого трехвходового элемента И и ко входу триггера, выход второго дешифратора подключен к первому входу второго трехвходового элемента И и к другому входу триггера.

Источники информации, принятые во внимание при экспертизе Iv Авторское свидетельство СССР JNTs 310368, кл. И 03 К 5/153. опублик. 1971.

2. Патент Японии № 53-45116, кл. 98(5) С 22, опублик. 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь уго-код | 1972 |

|

SU439836A1 |

| Устройство для управления широтноимпульсным преобразователем | 1976 |

|

SU650199A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для калибровки нуля двухполупериодных цифровых фазометров | 1978 |

|

SU748280A1 |

| Многоканальное усредняющее устройство | 1978 |

|

SU744609A1 |

| Измеритель амплитудно-частотных характеристик | 1980 |

|

SU951184A1 |

| Цифровой измеритель скорости | 1981 |

|

SU980001A1 |

| Фазометр | 1978 |

|

SU765750A1 |

| Устройство для формирования управляющих импульсов | 1987 |

|

SU1525833A1 |

Авторы

Даты

1981-11-23—Публикация

1980-03-24—Подача